当 ChatGPT 能写代码,当 Copilot 能画 PCB,硬件工程师的护城河,还剩下什么?

凌晨两点,你还在对着 ORCAD 密密麻麻的电阻网络发呆,为了一颗运放的选型翻阅了十几份 datasheet;隔壁工位的软件同事,刚刚用 Cursor 一键生成了 300 行驱动代码,正收拾东西准备下班。

你感叹:“硬件的命苦啊,软件有 AI 加持,我们有什么?难道 AI 还能替我焊板子?”

别急。真正的“硬件 AI 革命”,其实刚刚开始。它不会替你焊板子,但它正在重塑硬件工程师的“定义权”。

现状:我们正处于硬件设计“AI化”的前夜

很多人觉得 AI 离硬件很远,因为硬件是物理的、实体的、容错率极低的。但如果你观察近两年的 EDA(电子设计自动化)巨头动态,你会发现一场无声的变革正在发生:

- Cadence 推出了 Allegro X AI,宣称可以将 PCB 布局布线时间从数周缩短至数小时。

- Synopsys 将 AI 引擎嵌入到了从架构探索到验证的全流程。

- Altium 联手 Microsoft,试图利用云和 AI 重构元器件管理和设计协作。

市面上主流的 AI 工具,正在从“辅助计算”向“自主决策”演进。以下是目前几类主流工具的真实画像:

1. 元器件选型与知识库类

- 代表工具: SnapMagic Search (前身为SnapEDA)、Octopart AI、SamacSys

- 优点: 自然语言搜索。你不再需要像考古一样翻几百页的 PDF 找封装尺寸。输入“5V 2A 同步降压 小封装”,AI 直接给出推荐型号、对比成本、库存,甚至附带经过验证的符号和封装库。

- 缺点: 数据的“幻觉”风险。 如果 AI 推荐的元器件恰好处于“缺货”边缘,或者推荐的替代料存在隐性的性能陷阱(如 ESR 过高),新手工程师容易掉进坑里。

2. 原理图与Layout设计类

- 代表工具: Cadence Allegro X AI、Altium Designer 的 CoDesigner、以及一些初创的“AI布线员”。

- 优点: 算力碾压人力。 对于常规的 DDR 布线、电源模块布局,AI 的迭代速度是人类的千倍。它能同时兼顾热仿真、信号完整性和 EMI/EMC 规则,通过强化学习在几分钟内生成几十种布局方案,并挑出最优解。

- 缺点: 缺乏“艺术感”和“边界感”。 AI 目前的逻辑是“规则驱动”,它不懂“结构件干涉”,不懂“产线工人的焊接便利性”,更不懂“这个板子要卖给对散热噪音极其敏感的甲方”。它做的很“规范”,但可能很“蠢”。

3. 仿真与验证类

- 代表工具: Ansys AI + 仿真、Keysight Eggplant (测试自动化)

- 优点: 全空间探索。 传统的仿真需要人设定边界条件,AI 可以自己探索设计空间的边界,找到那个“人永远不会去试,但确实最优”的参数组合。在信号完整性(SI)和电源完整性(PI)分析中,AI 可以将仿真覆盖率提升几个数量级。

- 缺点: 算力成本极高。 跑一次全系统的 AI 驱动仿真,可能消耗的云服务费用比雇一个工程师还贵。且模型的可解释性差,出了 bug,你很难定位是仿真设置错,还是 AI 模型错。

深层次分析:AI到底动了谁的奶酪?

我们逐一拆解硬件开发的各个阶段,看看 AI 的真实影响:

-

元器件选型: AI是“信息平权”者。

过去,选型靠经验,老工程师知道哪些厂家靠谱,哪些型号是“坑”。现在,AI 让菜鸟也能快速拿到一份看似完美的 BOM。但 AI 取代不了的是“供应链嗅觉”和“隐性成本”的判断。当 AI 推荐一颗便宜 1 毛钱的电容,但会导致整条产线需要增加一道人工涂覆工序时,只有懂工艺、懂成本的工程师能做出正确的取舍。

-

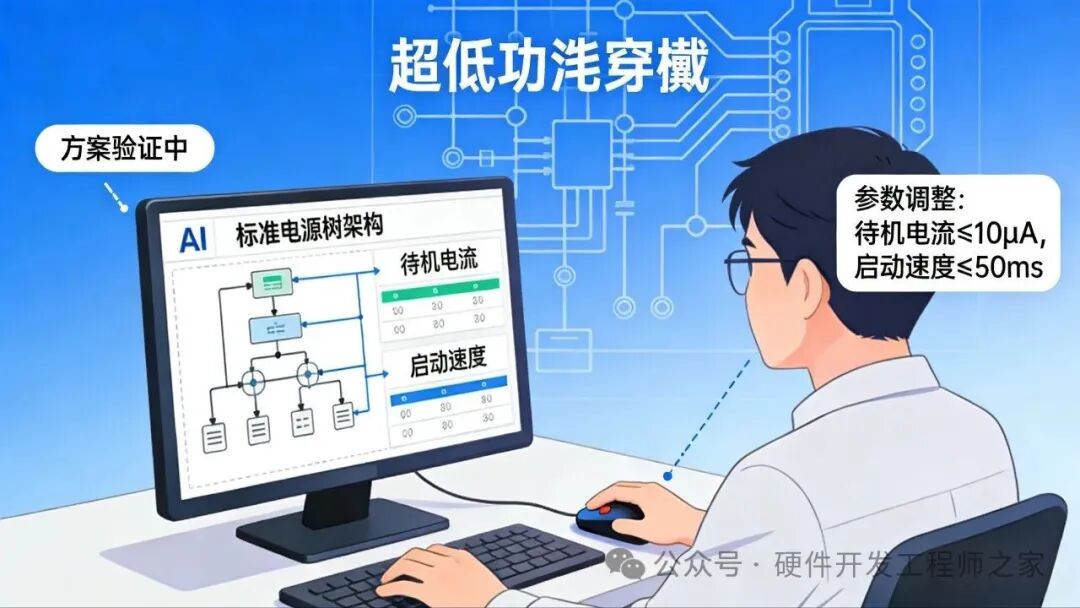

方案验证与原理图: AI是“草图大师”。

现在的 AI 已经能根据需求规格书,生成完整的电源树架构或 MCU 最小系统原理图。但它做不出“定制化”。比如你要做一款超低功耗的穿戴设备,AI 给的架构往往是标准库里的,它不懂你的产品需要在“待机电流 1uA”和“启动速度 10ms”之间做一个微妙的平衡。原理图的核心不是连线,而是“权衡”。

-

Layout(布局布线): AI是“搬砖冠军”。

这是 AI 目前最惊艳的领域。对于数字电路和高密度互连,AI 的表现已经接近甚至超过中级工程师。但它不懂“机械耦合”。硬件工程师在这个阶段的不可替代性在于:当结构工程师突然要求“板子厚度减薄 0.5mm”或者“接口位置左移 3mm”时,人类能瞬间在脑海里重构布局,而 AI 需要重新训练模型,且往往因为规则冲突而“死锁”。

-

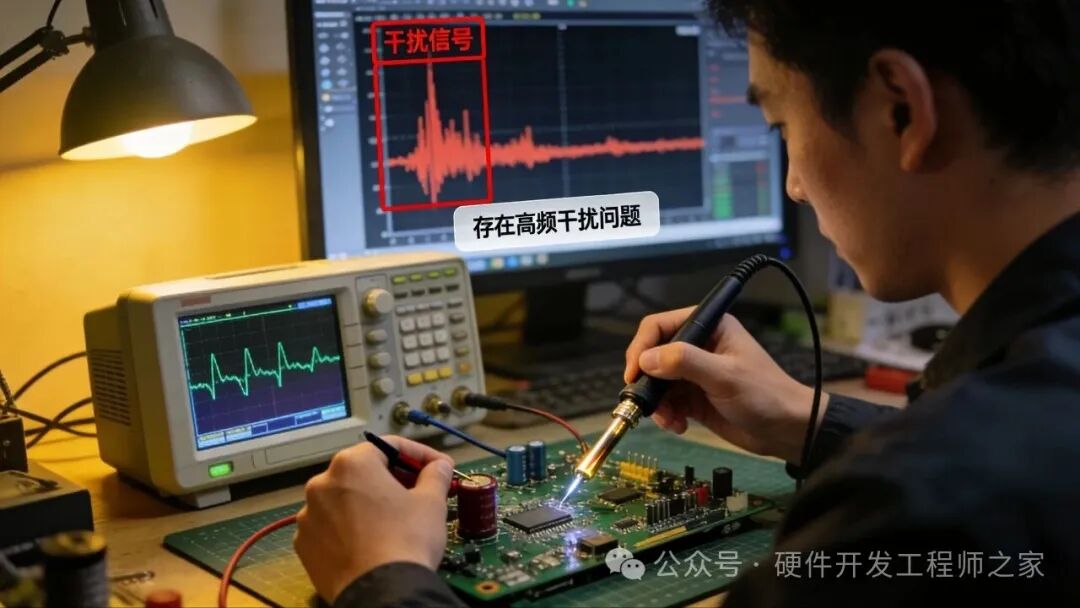

测试与调试: AI是“远程助手”。

你拿着示波器戳波形,AI 在后台帮你分析 FFT(快速傅里叶变换)频谱,并提示“疑似电源纹波叠加了 Wi-Fi 的 2.4GHz 干扰”。AI 可以帮你做自动化测试脚本。但拿起烙铁换电容、飞线、根据“嘶嘶声”判断电感饱和——这些触觉、听觉与视觉的融合判断,是物理世界对 AI 设下的高墙。

核心结论:AI不会取代你,但会用AI的硬件工程师会

这是老生常谈,但放在硬件领域,这句话的底层逻辑完全不同。

硬件工程师的本质不是“连线员”,而是“物理世界的约束解算者”。

软件工程师面对的是无限的逻辑空间,而硬件工程师面对的是:

- 物理定律的约束(欧姆定律、麦克斯韦方程)

- 物理空间的约束(结构尺寸、散热风道)

- 供应链的约束(交期、价格、二级货源)

- 时间的约束(上市时间、测试周期)

AI 目前最强的能力,是在单一维度上(如布线效率、信号质量)做到极致。但硬件工程的复杂,在于多维度约束的非线性耦合。

AI 的价值,是把你从“低维度的重复劳动”中解放出来,让你去处理“高维度的系统整合”。

硬件工程师如何破局?—— 从“画板工”到“系统架构师”的跃迁

面对 AI 的浪潮,硬件工程师不能只满足于“会画图、会仿真”。破局的底层逻辑在于“掌控复杂性”和“定义产品力”。

策略一:把自己变成“AI训练师”和“AI质检员”

不要害怕 AI 画板子,你要学会用 AI。

- 建立个人/团队的知识库: 把你们公司踩过的坑、特殊的工艺要求、客户的偏好,转化为规则文件,输入给 AI 工具。AI 生成的东西,你要能一眼看出“这个地方如果这样走线,产线良率会下降 2%”。

- 能力转移: 以前你花 80% 时间在画图,现在你要花 80% 时间在定义约束和验收结果。

策略二:向上游“吞噬”,掌握“系统定义权”

这是最关键的一点。如果你只懂原理图和 Layout,你永远是 AI 的“手下败将”。你必须往前走,走到产品定义阶段。

- 从“硬件设计”走向“硬件架构”: 你要比产品经理更懂技术可行性,比软件更懂底层驱动,比结构更懂散热与 EMI。当团队讨论下一代产品时,你要能说出:“基于我们目前的功耗预算和算力需求,我们不应该选 A 芯片,而应该选 B 芯片,因为虽然 B 贵 30%,但能省掉一路 DCDC、缩小 30% 的 PCB 面积、且软件迁移成本最低。”

- 底层逻辑: 这是“决策权”的争夺。AI 可以做最优解,但“最优”的前提是“目标函数”由谁定。谁定义目标函数,谁就是这个产品的核心。

策略三:深耕“跨界T型”知识,成为“物理与数字的桥梁”

AI 擅长处理数字世界的逻辑,但硬件工程师的价值在于“物理感知”。

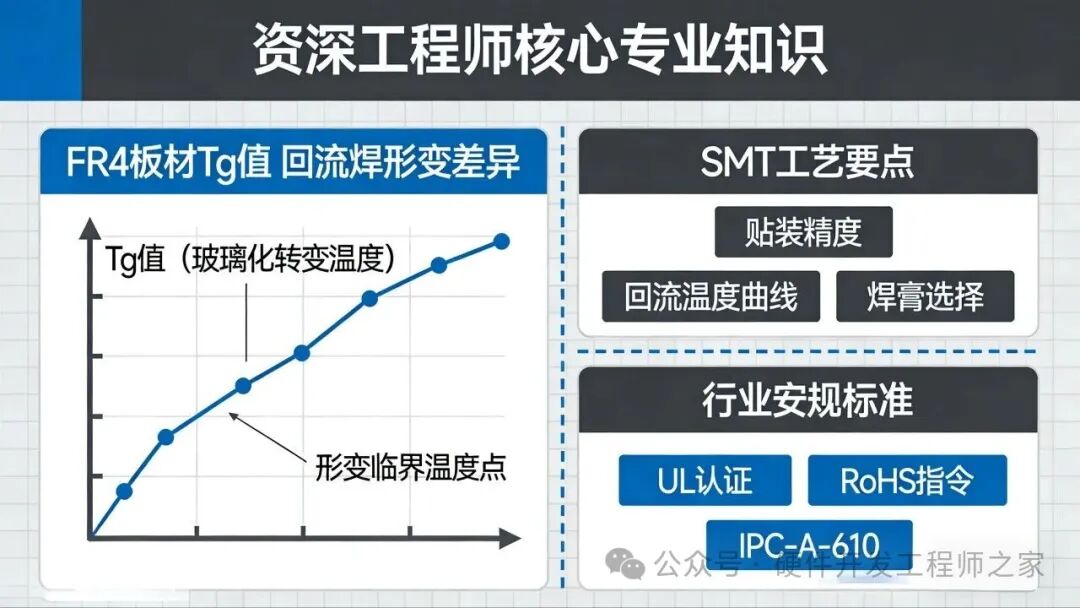

- 懂材料: 同样是 FR4 板材,不同 Tg 值(玻璃化转变温度)在回流焊时的形变差异,AI 模型很难精确建模,但资深工程师有直觉。

- 懂工艺: 懂 SMT(表面贴装技术)工艺流程,知道什么样的设计会让贴片机吸嘴无法下压。

- 懂行业标准: 医疗、汽车、军工,每个行业的认证标准和安规要求,是 AI 难以跨越的“合规墙”。

策略四:拥抱“软硬协同”的全栈能力

未来的硬件工程师,如果不会写一点嵌入式代码,不会看 Python 脚本(用于自动化测试或调用 AI 接口),会非常被动。

- 硬件定义软件,软件定义硬件。 当你能在硬件设计阶段,就预判到软件算法对硬件资源的消耗模式,并能通过微调硬件架构来释放软件算力时,你在团队中的地位将不可撼动。

结语:我们正在进入“硬件黄金时代”

很多人悲观地认为硬件行业夕阳红、薪资低、成长慢。但恰恰相反,AI 的出现,正在让硬件行业迎来一次“寒武纪大爆发”。

当 AI 将繁杂的底层设计工作自动化后,硬件的创新门槛降低了。以前需要一个 10 人团队做一年的板子,现在可能只需要 3 个人加 AI 辅助,就能在半年内高质量完成。

这意味着,创意的价值、系统整合的价值、解决复杂物理约束的价值,将被无限放大。

作为硬件工程师,不要再纠结于“AI能不能替代我画图”。

你要做的,是放下鼠标,走到白板前,画出那张没有人画过的系统架构图;是走到产线上,摸一摸回流焊炉的温度曲线;是坐到客户对面,听懂他那些无法量化的“感觉”。

这些,才是 AI 永远无法复制的,属于硬件工程师的“硬核浪漫”。

未来的顶级硬件工程师,不是画图最快的人,而是最能驾驭 AI、最懂系统、最通人性的人。

本文探讨了AI在硬件设计领域带来的变革与工程师的应对之道,更多深度技术讨论与实践分享,欢迎访问 云栈社区。