时钟系统是嵌入式开发的基石,尤其在STM32这类高性能微控制器中,它负责为CPU、内核总线及所有外设提供精准的时间基准。透彻理解时钟架构,不仅关乎程序能否正确运行,更是进行系统功耗优化与实现精确时序控制的关键。本文将从时钟源讲起,逐步剖析整个时钟树,并提供基于HAL库的实战配置代码与优化技巧。

STM32 时钟源全解析

STM32 提供了多种时钟源以适应不同的应用场景与成本要求,主要分为高速与低速两大类。

高速时钟源 (High-Speed Clock)

- HSE (高速外部时钟):通常由外部晶体振荡器或时钟信号提供。其频率范围因系列而异,常见如 4~26 MHz、4~48 MHz 等。HSE 精度高,稳定性好,适用于对时序精度有严格要求的场景,如USB通信、音频处理等。

- HSI (高速内部时钟):由芯片内部的RC振荡器产生,频率固定(如8MHz、16MHz、64MHz,依型号而定)。HSI精度相对较低,受温度和电压影响,但其最大优点是成本低且上电后立即可用,常作为系统启动或HSE失效时的备选时钟。

低速时钟源 (Low-Speed Clock)

- LSE (低速外部时钟):通常是外接的32.768 kHz晶振。这个频率经过分频恰好可以得到1 Hz的秒脉冲,因此专门用于为实时时钟 (RTC) 提供精准的计时基准。

- LSI (低速内部时钟):芯片内部的另一个RC振荡器,频率约为32 kHz。它主要用于为独立看门狗 (IWDG) 提供时钟,也可以在LSE不可用时作为RTC的备用时钟源,但精度较差。

核心引擎:PLL (锁相环)

时钟源提供的频率往往无法直接满足内核和外设的高频需求,这时就需要PLL(锁相环) 登场。PLL 是一个倍频器,能将一个较低的输入频率“倍频”到更高频率。

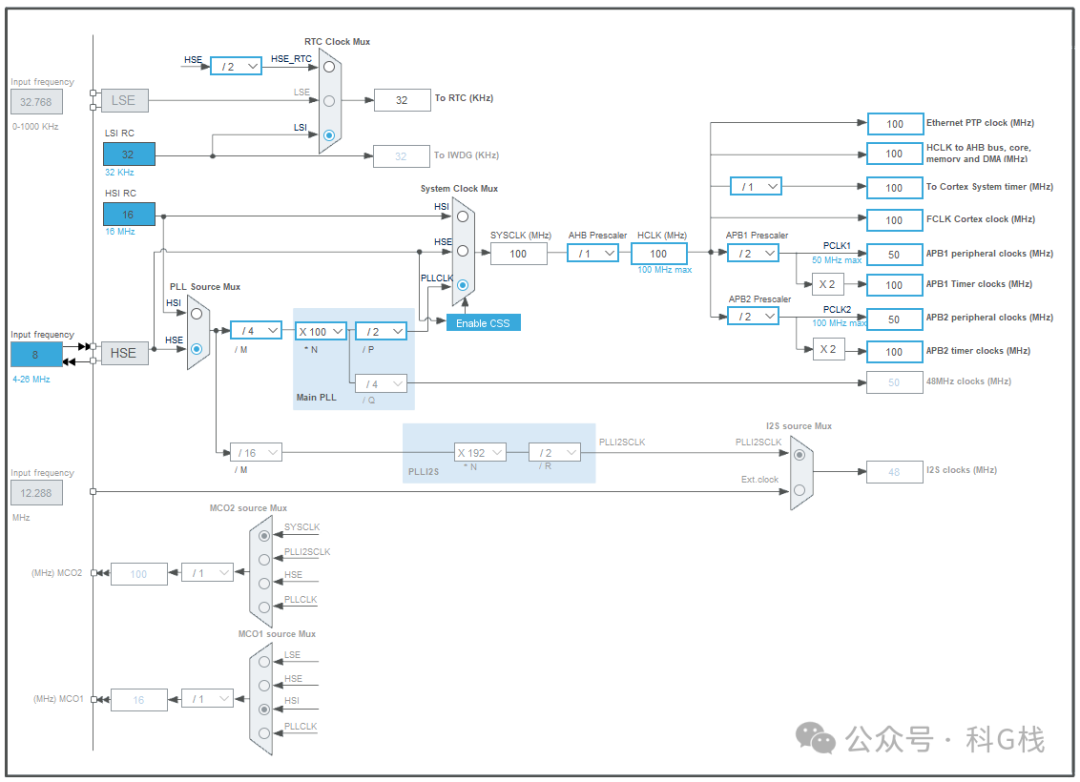

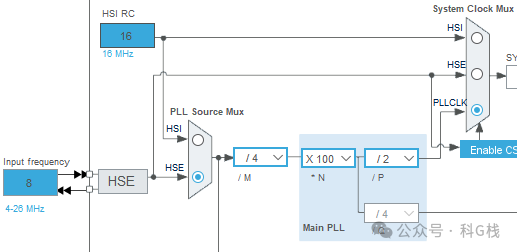

PLL的工作流程可以分解为几个关键步骤,由一个PLL Source Mux(选择开关) 开始,它决定是使用HSE还是HSI作为PLL的输入源。

- 预分频器 (/M):对应参数

PLLM。它的作用是将选中的时钟源频率降低,确保输入到PLL核心(VCO)的频率在一个规定的安全范围内(通常是1-2MHz)。

- *倍频器 ( N)**:这是PLL的核心,对应参数

PLLN。它将预分频后的低频时钟进行大幅度倍频,产生一个非常高的频率,即VCO(压控振荡器)时钟。

- 后分频器 (/P 和 /Q):VCO输出的频率通常过高,需要再次分频才能使用。

- 后分频器 /P (PLLP):专门用于生成系统时钟 (SYSCLK)。

- 后分频器 /Q (PLLQ):用于生成其他外设所需的时钟,最典型的就是USB OTG FS、SDIO等所需的精确48MHz时钟。

整个PLL生成系统时钟的核心计算公式如下:

*系统时钟(SYSCLK) = (时钟源频率 / M) N / P**

PLL配置完成后,得到的SYSCLK并非直接使用,它作为源头,会经过多级分频器(预分频器),最终为芯片上的不同模块提供合适的工作时钟。

系统时钟分发与总线时钟

SYSCLK生成后,会进入一个复杂的分发网络,为不同的总线域和外设提供时钟。

-

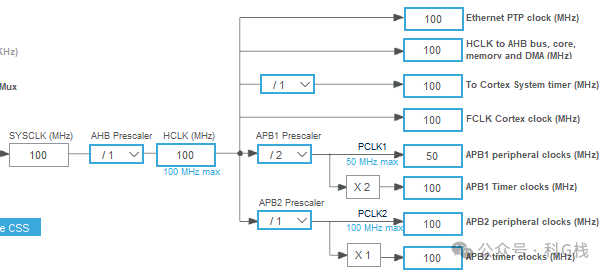

AHB Prescaler (HPRE):系统高性能总线预分频器。它对SYSCLK进行分频,产生HCLK。

- HCLK:AHB总线时钟,直接供给CPU、内存(Flash/SRAM)和DMA控制器,是系统核心的运行时钟。

- FCLK (Cortex自由运行时钟):通常与HCLK同频,用于Cortex-M内核的某些内部操作,不受内核停止影响。

- Cortex System Timer (SysTick):其时钟源可以是HCLK或HCLK/8。

-

APB1 Prescaler (PPRE1):低速外设总线(APB1)分频器。它进一步对HCLK分频,产生PCLK1。

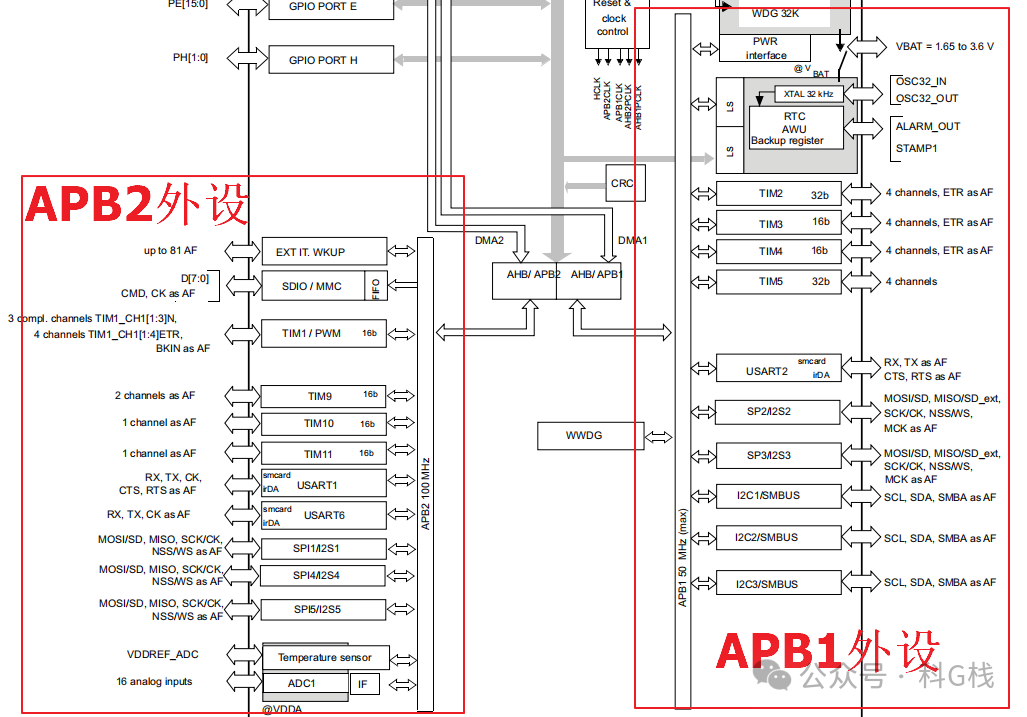

- PCLK1:APB1外设时钟,供给诸如I2C1/2/3、SPI2/3、USART2等低速外设。

- APB1 Timer clocks:一个特殊规则是,连接到APB1总线上的定时器(如TIM2-TIM7),其输入时钟是PCLK1的2倍(如果APB1预分频系数不为1)。

-

APB2 Prescaler (PPRE2):高速外设总线(APB2)分频器。它也对HCLK分频,产生PCLK2。

- PCLK2:APB2外设时钟,供给诸如SPI1、USART1、ADC等高速外设。

- APB2 Timer clocks:同理,APB2总线上的定时器(如TIM1、TIM8-TIM11)的输入时钟是PCLK2的2倍(如果APB2预分频系数不为1)。

下图清晰地展示了APB1和APB2总线上连接的外设模块:

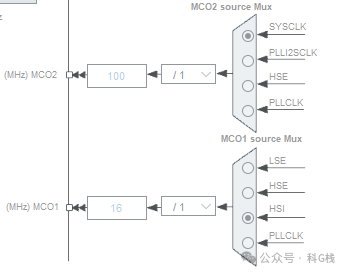

此外,STM32还提供了MCO (微控制器时钟输出) 功能,可以将内部时钟(如SYSCLK、HSI、HSE、PLLCLK等)通过特定的引脚输出,为外部器件提供时钟源。

实战:使用HAL库配置系统时钟

理解了理论,我们来看如何用代码实现。以下是基于STM32 HAL库的一个典型时钟初始化函数 SystemClock_Config(),它将外部8MHz晶振(HSE)通过PLL倍频到100MHz作为系统时钟。

void SystemClock_Config(void)

{

RCC_OscInitTypeDef RCC_OscInitStruct = {0};

RCC_ClkInitTypeDef RCC_ClkInitStruct = {0};

/** 配置主内部稳压器输出电压

*/

__HAL_RCC_PWR_CLK_ENABLE();

__HAL_PWR_VOLTAGESCALING_CONFIG(PWR_REGULATOR_VOLTAGE_SCALE1);

/** 根据RCC_OscInitTypeDef结构体中的参数初始化RCC振荡器

*/

RCC_OscInitStruct.OscillatorType = RCC_OSCILLATORTYPE_LSI|RCC_OSCILLATORTYPE_HSE;

RCC_OscInitStruct.HSEState = RCC_HSE_ON;

RCC_OscInitStruct.LSIState = RCC_LSI_ON;

RCC_OscInitStruct.PLL.PLLState = RCC_PLL_ON;

RCC_OscInitStruct.PLL.PLLSource = RCC_PLLSOURCE_HSE;

RCC_OscInitStruct.PLL.PLLM = 4; // M = 4

RCC_OscInitStruct.PLL.PLLN = 100; // N = 100

RCC_OscInitStruct.PLL.PLLP = RCC_PLLP_DIV2; // P = 2

RCC_OscInitStruct.PLL.PLLQ = 4; // Q = 4

if (HAL_RCC_OscConfig(&RCC_OscInitStruct) != HAL_OK)

{

Error_Handler();

}

/** 初始化CPU、AHB和APB总线时钟

*/

RCC_ClkInitStruct.ClockType = RCC_CLOCKTYPE_HCLK|RCC_CLOCKTYPE_SYSCLK

|RCC_CLOCKTYPE_PCLK1|RCC_CLOCKTYPE_PCLK2;

RCC_ClkInitStruct.SYSCLKSource = RCC_SYSCLKSOURCE_PLLCLK; // 系统时钟源选择PLL输出

RCC_ClkInitStruct.AHBCLKDivider = RCC_SYSCLK_DIV1; // AHB分频 = 1, HCLK = SYSCLK = 100MHz

RCC_ClkInitStruct.APB1CLKDivider = RCC_HCLK_DIV2; // APB1分频 = 2, PCLK1 = HCLK/2 = 50MHz

RCC_ClkInitStruct.APB2CLKDivider = RCC_HCLK_DIV2; // APB2分频 = 2, PCLK2 = HCLK/2 = 50MHz

if (HAL_RCC_ClockConfig(&RCC_ClkInitStruct, FLASH_LATENCY_3) != HAL_OK)

{

Error_Handler();

}

}

代码解析:

此配置实现了:SYSCLK = (8MHz / 4) * 100 / 2 = 100MHz。同时,AHB无分频(HCLK=100MHz),APB1和APB2均为2分频(PCLK1=PCLK2=50MHz)。注意,APB上的定时器时钟会因此翻倍至100MHz。

功耗优化关键技巧

在嵌入式系统中,功耗管理至关重要,而时钟是最大的功耗来源之一。掌握以下技巧可以有效优化STM32的功耗:

- 动态电压频率调节 (DVFS):根据当前CPU负载,动态降低系统时钟主频(SYSCLK),并可能同步降低内核电压。这在HAL库中通常通过

HAL_RCC_ClockConfig 函数在运行时重新配置来实现。

- 关闭未使用的外设时钟:在初始化外设前开启其时钟,在进入低功耗模式或任务完成后,及时关闭其时钟以省电。例如:

__HAL_RCC_GPIOA_CLK_DISABLE()。

-

合理利用低功耗模式:STM32提供了多种低功耗模式。

- 睡眠模式 (Sleep):仅停止CPU时钟,外设仍运行。唤醒速度快。

- 停止模式 (Stop):停止所有时钟(HSI/HSE, PLL),保留SRAM和寄存器内容。唤醒后需重新配置时钟。

- 待机模式 (Standby):功耗最低,几乎关闭所有电源域,仅需引脚或RTC闹钟唤醒。SRAM内容丢失。

// 示例:进入睡眠模式(等待中断唤醒)

HAL_PWR_EnterSLEEPMode(PWR_MAINREGULATOR_ON, PWR_SLEEPENTRY_WFI);

总结与进阶建议

STM32的时钟系统是其高效稳定运行的基石。从基础的时钟源选择,到复杂的PLL倍频与总线分频,再到精细的功耗控制,每一个环节都考验着开发者对底层硬件的理解。建议在实际项目开发中,务必结合具体型号的《参考手册》时钟章节和《数据手册》,明确各时钟源的极限参数与配置限制。通过反复实践与调试,你不仅能避免常见的时钟配置陷阱,更能设计出性能与功耗俱佳的嵌入式系统。关于更多底层编程与计算机基础的深入探讨,欢迎在云栈社区与广大开发者交流分享。 |