在互联网行业频繁出现大规模裁员的背景下,嵌入式开发被许多从业者视为躲避失业风险的避风港。这种认知的核心逻辑在于嵌入式系统与物理世界的紧密耦合,使得其开发周期、产品生命周期以及技术迭代速度与纯软件互联网产品存在显著差异。但我们必须意识到,这种所谓的“避风港”属性并非来源于行业门槛的降低,而是来源于硬件约束、实时性要求以及长周期的工业逻辑所构建的技术壁垒。

一、嵌入式开发与纯软件开发的底层逻辑差异

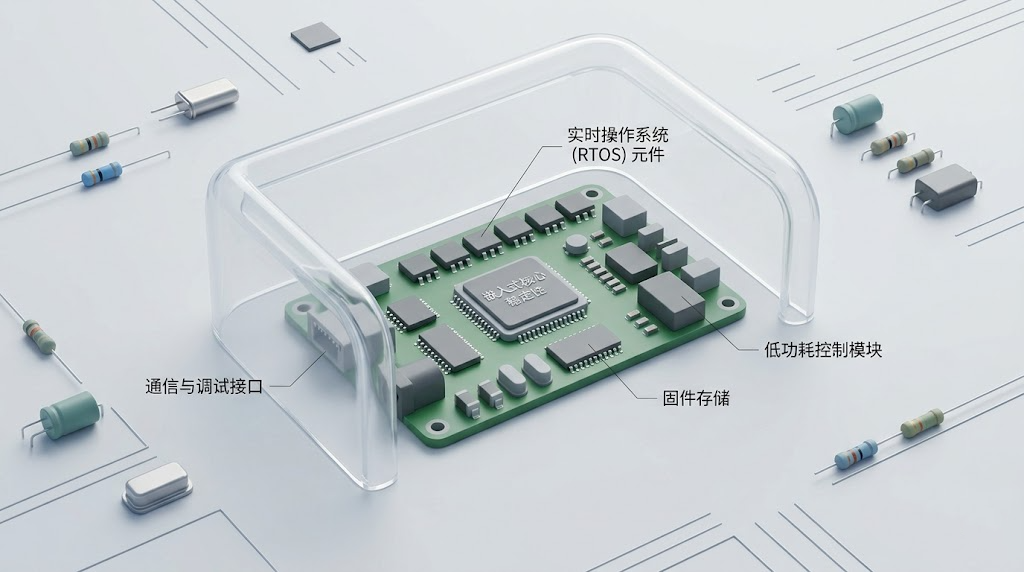

互联网开发的核心在于业务逻辑的快速迭代与高并发处理,其资源往往是虚拟的、可水平扩展的。而在嵌入式领域,我们面对的是受限的硬件资源:CPU 主频可能只有几十兆赫兹,内存(RAM)可能仅有几十 KB,闪存(Flash)空间也极为有限。在这种环境下,代码的执行效率不仅关系到用户体验,更直接决定了系统能否稳定运行。

我们编写的每一行代码都必须考虑其对硬件资源的影响。在纯软件开发中,开发者很少关注变量分配在栈上还是堆上,但在嵌入式开发中,动态内存分配(malloc/free)在许多高可靠性场景下是被严格禁止的。因为在长时间运行的系统中,堆碎片会导致系统因内存分配失败而崩溃。我们必须通过静态内存分配或内存池(Memory Pool)来保证内存分配的确定性。这种对底层细节的极致掌控,是嵌入式工程师的核心竞争力之一,也常常是C/C++开发者深入钻研的领域。

二、硬件抽象层与驱动程序的开发深度

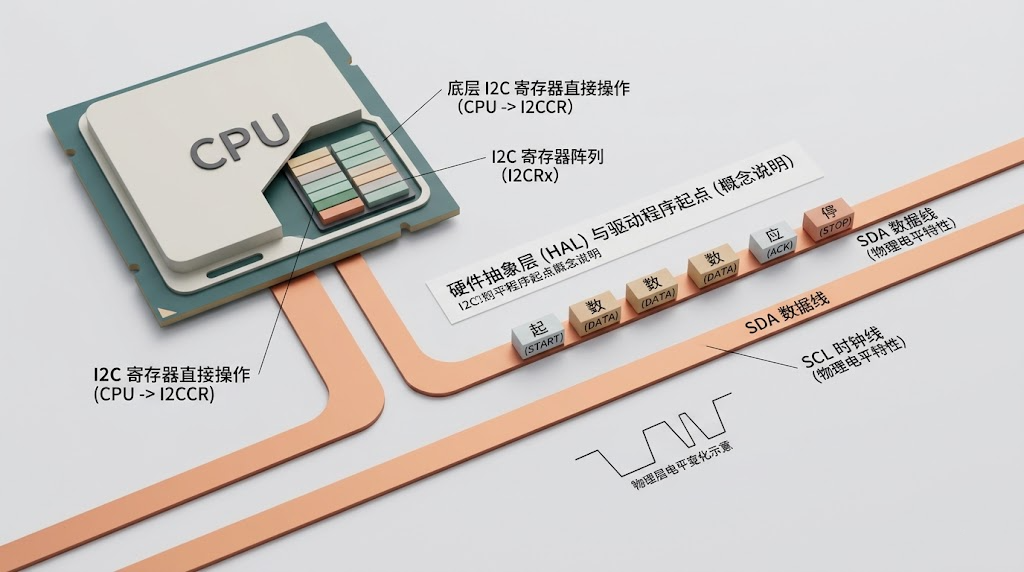

嵌入式全栈开发的起点通常是硬件抽象层(HAL)与驱动程序。我们不能像应用层开发那样调用标准库接口,而是要直接操作寄存器。以一个简单的 I2C 接口驱动为例,我们不仅要理解协议的起始位、停止位、应答位等逻辑时序,还要考虑物理层的电平特性。

在高速 I2C 通信中,上拉电阻的阻值直接影响信号上升沿的陡峭程度。如果总线电容过大,上升沿会变得圆滑,导致接收端无法正确采样。我们在编写驱动程序时,需要通过示波器观察波形,调整驱动电流强度或降低通信频率。这种跨越软件与物理电性能的调试能力,是纯互联网工程师难以在短时间内掌握的。

此外,中断驱动机制是嵌入式系统的核心。我们必须深入理解中断嵌套、中断优先级以及中断服务程序(ISR)的执行时间。在 ISR 中,我们严禁执行阻塞操作或长耗时计算,否则会引发任务调度异常或导致更高级别中断的响应延迟。这种对微秒级时序的敏感度,是构建高性能嵌入式系统的基础。

三、实时操作系统内核的确定性分析

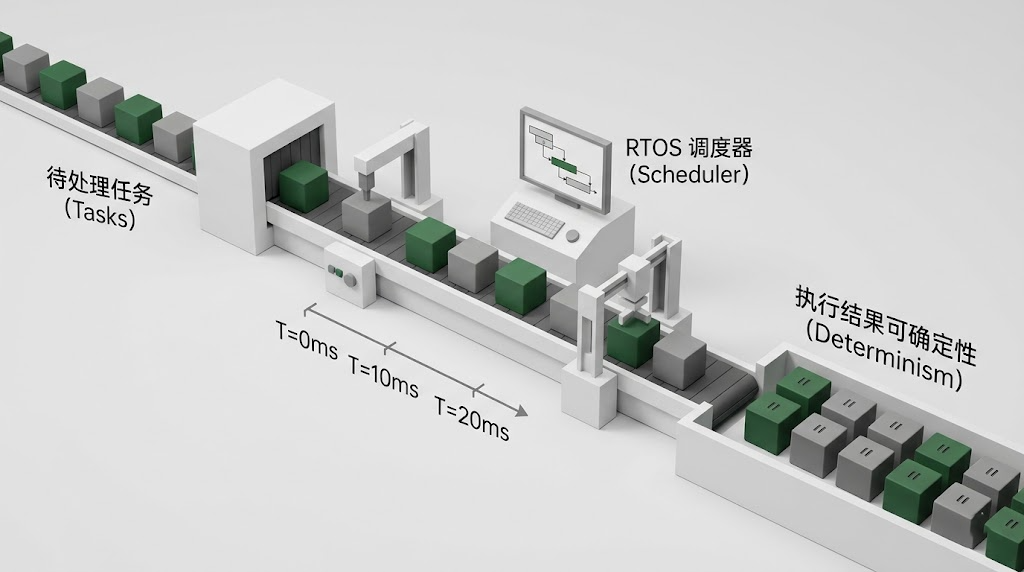

嵌入式系统通常运行在实时操作系统(RTOS)之上,如 FreeRTOS、RT-Thread 或 uC/OS。这里的实时性(Real-time)指的不是执行速度快,而是执行结果的可确定性(Determinism)。

我们需要深入剖析 RTOS 的任务调度算法。以基于优先级的抢占式调度为例,当高优先级任务就绪时,内核必须在确定的时间内完成上下文切换(Context Switch)。上下文切换涉及到当前任务 CPU 寄存器状态的保存(Push)与新任务状态的恢复(Pop)。在 ARM Cortex-M 架构中,这通常涉及 R0-R15 寄存器以及程序状态寄存器(xPSR)的操作。

我们还需要面对优先级翻转(Priority Inversion)这一经典问题。当一个低优先级任务持有了高优先级任务所需的互斥锁,而此时一个中优先级的任务抢占了低优先级任务,就会导致高优先级任务被无限期阻塞。我们必须通过优先级继承(Priority Inheritance)或优先级天花板(Priority Ceiling)协议来解决这一逻辑冲突。理解这些内核机制的底层原理,对于设计高可靠性的并发系统至关重要。

四、通信协议栈与工业总线的技术密度

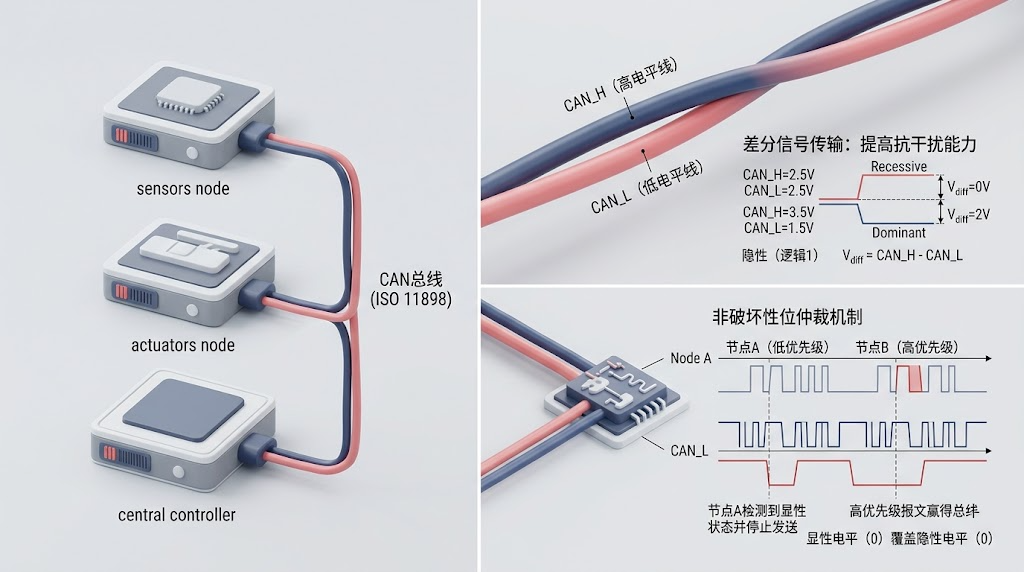

在嵌入式系统中,设备间的通信往往依赖于各种工业总线,如 CAN、RS-485、以太网等。以 CAN 总线为例,它的非破坏性位仲裁机制和差分信号传输使其在汽车和工业控制中具有极高的可靠性。

我们不仅要编写应用层的通信协议,还要理解链路层的帧结构。在 CAN 总线中,位填充(Bit Stuffing)机制用于保证信号的同步,CRC 校验用于保证数据的完整性。当总线出现错误时,硬件会自动进入错误被动状态甚至离线状态。我们作为工程师,必须能够通过分析错误计数器(TEC/REC)来诊断硬件链路是否存在物理损坏或电磁干扰。

而在嵌入式以太网开发中,我们则需要处理 TCP/IP 协议栈裁剪。在资源受限的任务中,我们无法运行完整的 Linux 网络栈,通常使用 lwIP 这种轻量级协议栈。我们需要手动配置零拷贝(Zero-copy)机制,通过 DMA(直接存储器访问)将网卡数据直接传输到内存缓冲区,避免 CPU 参与数据搬运,从而降低系统负载。这种对数据流向的精确控制,是提升嵌入式网络性能的关键。

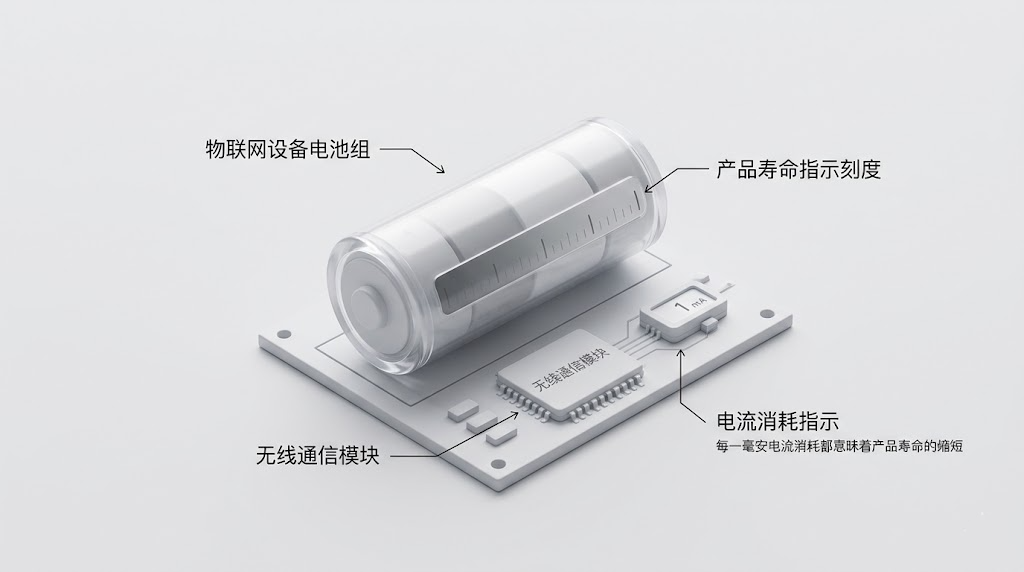

五、电源管理与低功耗设计的工程实践

与互联网开发完全不同,嵌入式开发必须严苛地考虑功耗。在电池供电的物联网设备中,每一毫安的电流消耗都意味着产品寿命的缩短。

我们必须利用 SoC 提供的各种低功耗模式(Sleep, Stop, Standby)。在系统空闲时,我们将 CPU 挂起,关闭不必要的外设时钟,并降低 LDO 的输出电压。我们甚至需要操作电源管理芯片(PMIC)来动态调整核心电压(DVFS)。

软件层面的低功耗设计同样复杂。我们需要设计一套基于事件驱动的机制,确保系统只在有任务处理时才唤醒。唤醒后的时钟恢复过程需要精确的时序控制,否则会导致外部晶振未稳定前外设就开始工作,进而引发通信乱码。这种对能量密度的敏感,是嵌入式工程师在硬件受限环境下的一种工程本能。

六、可靠性工程与异常处理机制

在工业或汽车领域,嵌入式系统的故障可能导致物理损害。因此,我们必须构建多层的异常处理机制。

硬件看门狗(Watchdog)是最后一道防线。我们必须在软件的主循环或关键任务中定期“喂狗”。如果系统因为死循环或死锁导致喂狗失败,看门狗电路将强制 CPU 复位。但仅有看门狗是不够的,我们还需要实现软件层面的容错逻辑。

例如,在 Flash 闪存操作中,由于掉电可能导致数据写入一半,我们必须实现日志式的文件系统或双备份机制,确保数据的一致性。在内存管理中,我们需要利用 MPU(内存保护单元)为不同的任务划定访问边界,防止某个任务的指针越界导致整个系统崩溃。这种对“失败”的预判和防御性编程,是嵌入式全栈开发中最能体现经验值的部分。

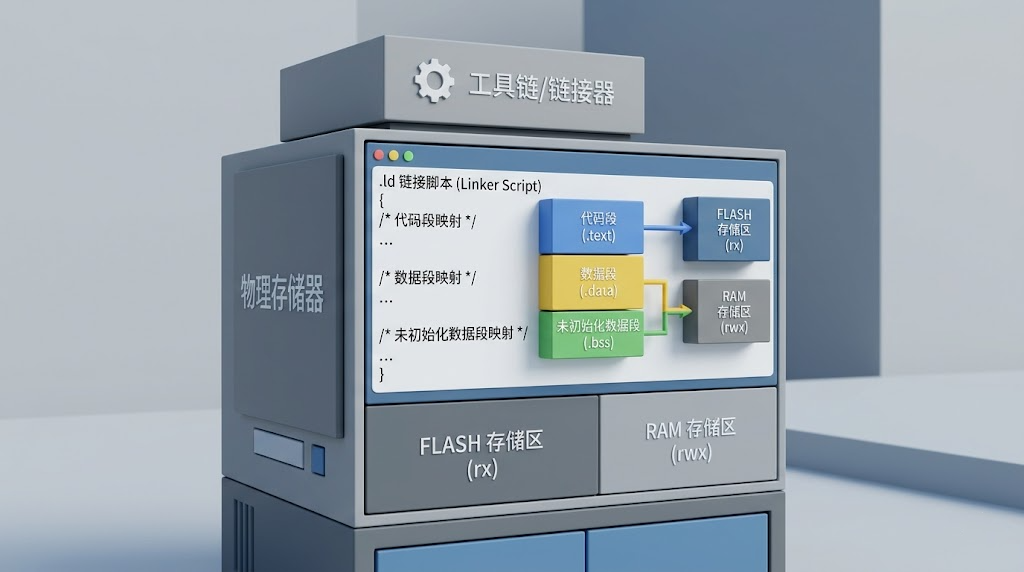

七、编译链与工具链的底层定制

嵌入式开发离不开对工具链的深度使用。我们需要理解链接脚本(Linker Script, .ld 文件)是如何将代码段(.text)、数据段(.data)和未初始化数据段(.bss)映射到物理存储地址的。

通过定制链接脚本,我们可以将关键算法函数放置在内部 SRAM 中运行,以消除从外部 Flash 取指的等待周期,显著提升执行速度。我们还需要掌握交叉编译(Cross-compilation)技术,在 x86 环境下构建目标架构(如 ARM, RISC-V)的可执行文件。

在调试阶段,我们依赖 JTAG 或 SWD 接口进行硬件仿真。通过断点、单步执行以及查看寄存器状态,我们可以精确定位硬件逻辑错误。这种从源代码到二进制指令,再到波形分析的全链路调试能力,构成了嵌入式工程师极高的技术护城河。

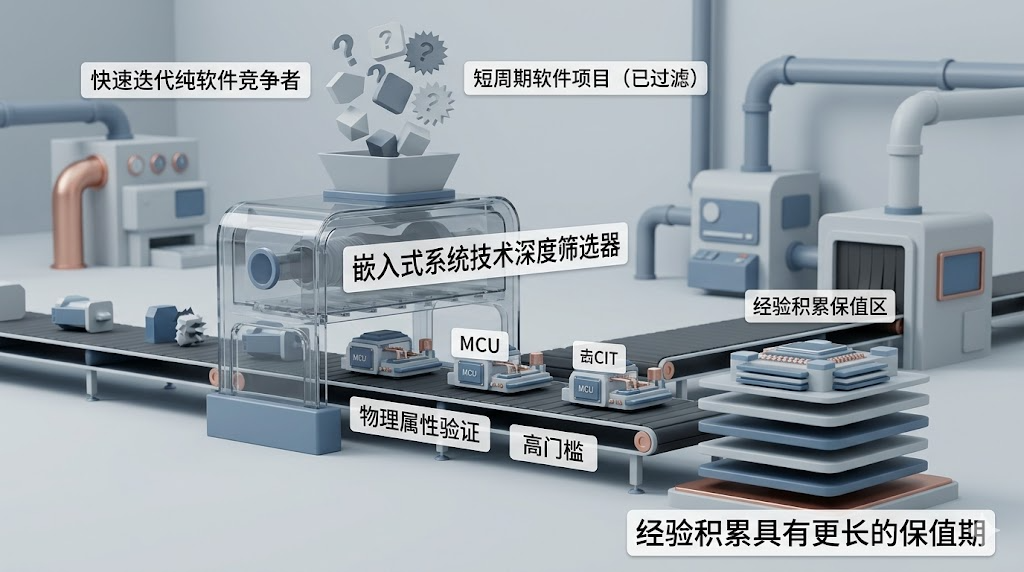

八、嵌入式“避风港”论调的现实审视

回到最初的问题:嵌入式开发真的是避风港吗?从技术深度来看,它确实因为高门槛而过滤掉了一部分竞争者。硬件的物理属性决定了它的迭代速度不会像纯软件那样疯狂,经验的积累具有更长的保值期。

然而,嵌入式开发也面临着自身的挑战。由于软硬件高度耦合,开发环境搭建复杂,调试周期长,开发者需要承担巨大的心理压力。一个硬件设计缺陷可能导致数月编写的软件完全失效,或者需要通过复杂的软件逻辑来绕过硬件 bug(Workaround)。

此外,随着国产化替代的浪潮,大量的国产芯片涌入市场,这些芯片的文档质量和生态完善程度参差不齐。我们作为工程师,往往需要阅读数千页的英文 DataSheet,在没有成熟社区支持的情况下,独立攻克芯片底层的技术坑。这种“开荒”的能力,才是决定我们能否在任何经济周期下都能生存的核心竞争力。

嵌入式开发不是一个可以躺平的避风港。它更像是一座高难度的技术堡垒。只有当你真正掌握了从物理层、驱动层到内核层、应用层的全栈知识体系,能够熟练地在示波器波形与汇编代码之间进行逻辑切换,你才拥有了真正的职业安全感。这种安全感不是来自行业的溢价,而是来自对技术底层逻辑的深度掌控和对物理世界规则的敬畏。对于想要深入探讨或寻找技术同道的开发者,可以关注 云栈社区 的相关讨论。