前段时间接了个棘手的活:给一台老设备升级功能。设备的主控是一颗有些年头的 ARM9 芯片。上手调试时,一个明显的体验落差就出来了:在 Keil 这类 IDE 里进行全速仿真时,完全没法实时查看变量变化,不像现在的 Cortex-M 芯片那样方便。客户给得实在太多,这风险也就显得没那么大了。

这个差异点,核心就在于调试架构的不同。现在的 Cortex-M 系列普遍支持 Real-Time Transfer (RTT) 技术。简单说,RTT 是一种高效、低侵入的调试方法,允许你在芯片全速运行时,实时观测内存和变量状态,几乎不影响程序执行。你在网上看到的用 J-Link 当串口调试助手输出 printf,或者 Keil 的 Watch 窗口里变量值自动刷新,底层依赖的就是 RTT。

以前遇到这种问题,我可能会想:“全速运行看不了就算了,打断点调试呗,估计是 J-Link 驱动没装好。” 但随着对计算机基础理解的深入,我发现这些差异背后,是调试技术的代际革新。搞清楚它,你收获的就不只是更新驱动,而是对嵌入式系统调试更本质的认识。

1. 老一代ARM7/ARM9的调试局限

以 ARM7TDMI、ARM9TDMI 为代表的经典内核,基于 ARMv4T/ARMv5TE 架构。它们的调试功能主要由一个叫做 EmbeddedICE-RT 的模块提供。

这套调试机制的核心设计思想是:调试器通过 JTAG 接口“操纵”CPU,让 CPU 替调试器去执行内存访问操作。

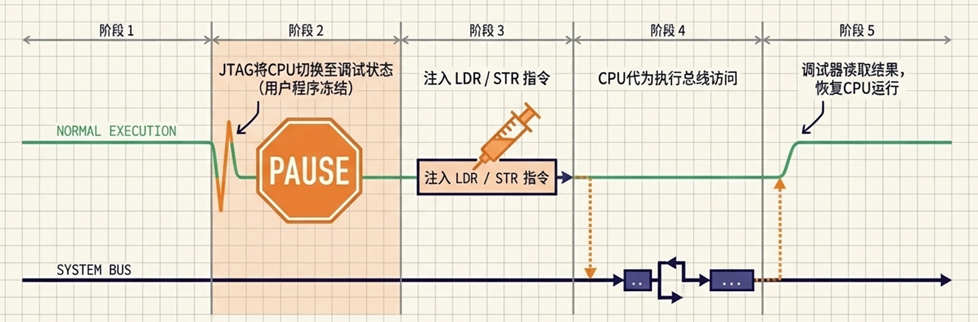

具体过程是怎样的呢?请看下面的时序图:

当调试器需要读写内存(比如查看一个变量)时:

- 首先通过 JTAG 扫描链将 CPU 切换到调试状态,此时用户程序被暂停;

- 向 CPU 的指令流水线注入一条 LDR (读内存) 或 STR (写内存) 指令;

- CPU 内核执行这条被注入的指令,完成实际的内存访问;

- 调试器再通过 JTAG 读取结果,然后恢复 CPU 运行。

可以看到,每次内存访问都会打断 CPU 的正常执行。这在专业上被称为侵入式调试。对于实时性要求高的系统,这种暂停会导致不可预测的时序紊乱,自然也谈不上在全速运行时持续、无感地获取数据了。

如果你的 ARM9 芯片支持全速数据读取,那说明芯片厂商比较良心,为你集成了更高级的调试组件。

2. Cortex-M 系列的调试变革

为了解上述痛点,ARM 在新架构(如 ARMv7-M, ARMv8-M)中引入了全新的调试系统——CoreSight。

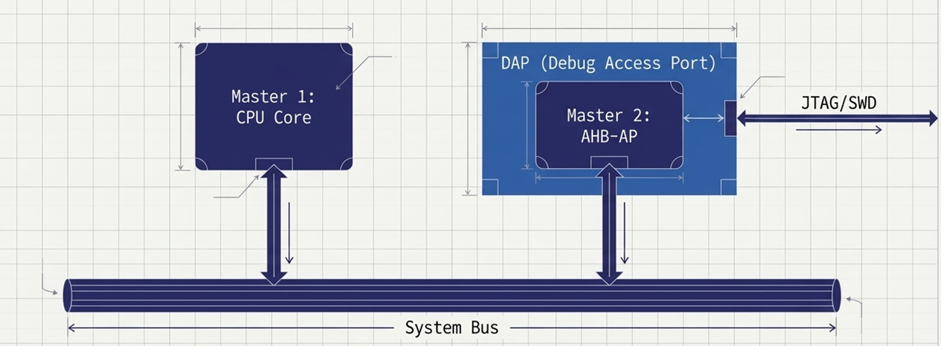

CoreSight 的核心是一个叫做 DAP(Debug Access Port) 的模块。搞过 ARM 调试器的小伙伴对“DAP”这个名字应该不陌生,很多调试器固件就叫 DAP-Link,没错,就是它。

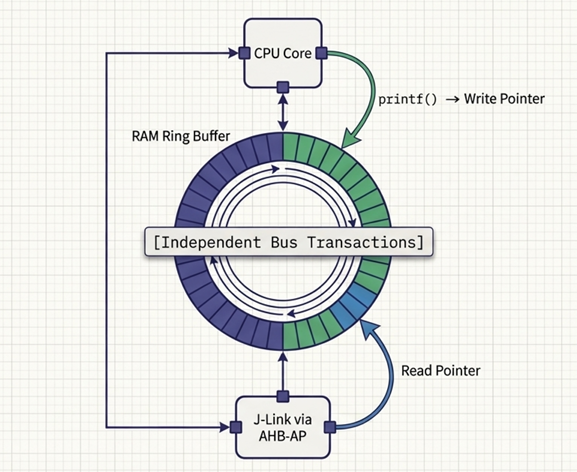

DAP 包含多个访问端口(AP),其中最常用的是 AHB-AP(也叫 MEM-AP)。AHB-AP 本身是一个独立的总线主控设备,它直接连接到芯片的系统总线(如 AHB 总线)上。

从上图可以清晰看出,AHB-AP 和 CPU 内核在总线层级上是平等的,两者都具备发起总线事务的能力。因此,调试器可以通过 DAP 直接控制 AHB-AP,无需 CPU 介入,就能在全速运行的同时,直接对内存、外设进行读写。这就为实现实时、非侵入的调试奠定了基础。这也是为什么 Cortex-M 单片机基本都能轻松实现 Watch 窗口变量实时刷新的原因。

3. Real-Time Transfer (RTT) 如何工作?

聊到这里,就不得不提 RTT 的具体实现了,它正是基于 CoreSight 的 DAP 和 AHB-AP 能力。

RTT 的本质,是利用内存中的环形缓冲区进行通信。基本原理是:在 MCU 的 RAM 里划出一块区域作为环形缓冲区,你的应用程序通过标准的 printf 等函数将数据写入缓冲区;同时,调试器(如 J-Link)在后台通过 AHB-AP 不停地读取这个缓冲区,并将数据上传到 PC 端的 IDE 或调试工具显示出来。

这样一来,就实现了类似串口 printf 的输出功能,而且速度更快、几乎不影响 CPU。当然,printf 只是最初级的玩法,你可以基于这个机制设计更复杂的数据上传和命令下发电路。

结语

所以,现在你明白了吗?你的 IDE 能否在全速仿真时实时查看变量,关键取决于芯片内核的调试架构。ARM9 等老架构受限于侵入式的调试访问,而 Cortex-M 等新架构凭借 CoreSight DAP 和独立的总线主控(AHB-AP),实现了非侵入式的实时数据传输。

技术的演进总是为了解决实际痛点。从“停下来看”到“边跑边看”,这背后是一整套计算机体系结构的升级。希望这次的分享能帮你更深入地理解手中的调试工具,而不仅仅是停留在“驱动有问题”的层面。如果你对这类底层技术原理感兴趣,欢迎到云栈社区与更多开发者一起交流探讨。