在进行数字集成电路设计验证时,对标准单元(Standard Cell)进行晶体管级的SPICE仿真是评估其性能和可靠性的关键步骤。本文将以一个具体的反相器单元为例,详细介绍使用HSPICE进行仿真的完整流程。

1. 从CDL网表提取晶体管级电路

首先,我们需要从标准单元库提供的CDL(Circuit Description Language)网表文件中,找到目标反相器的电路描述。以下是一个名为INV2_7TV50的反相器子电路定义,它由一个NMOS管和一个PMOS管构成:

.SUBCKT INV2_7TV50 I ZN VDD VSS VNW VPW

MM12 ZN I VSS VPW n50_ckt W=1.16u L=500.00n

MM13 ZN I VDD VNW p50_ckt W=1.81u L=450.00n

.ENDS

2. 编写SPICE测试平台(Testbench)

接着,我们需要编写一个SPICE测试平台文件(例如test.sp),将上述反相器电路实例化,并为其添加电源、输入激励和负载,以构成一个完整的可仿真电路。

* spice test for INV2_7TV50

.OPTION POST INGOLD=2

.LIB 'hsp/d18_v3e_bcd_v1p4_rev1.lib' tt

.SUBCKT INV2_7TV50 I ZN VDD VSS VNW VPW

XMM12 ZN I VSS VPW n50_ckt W=1.16u L=500.00n

XMM13 ZN I VDD VNW p50_ckt W=1.81u L=450.00n

.ENDS

XINV2 I ZN VDD VSS VDD VSS INV2_7TV50

CL ZN 0 10fF

VDD VDD 0 DC 5

VSS VSS 0 DC 0

VIN I 0 PULSE(0 5 1n 100p 100p 10n 20n)

.TRAN 10p 40n

.END

测试平台关键部分解析:

- 模型库引入:

.LIB 'hsp/d18_v3e_bcd_v1p4_rev1.lib' tt 语句引入了工艺角为tt的晶体管器件模型库。由于n50_ckt和p50_ckt在库中是以子电路(subckt)形式定义的,因此在实例化时需要使用X作为前缀。

- 单元实例化:

XINV2 I ZN VDD VSS VDD VSS INV2_7TV50 将我们定义的反相器子电路实例化到测试平台中。

- 负载与电源:

CL ZN 0 10fF 在反相器输出端ZN上挂接了10fF的容性负载,用以模拟实际后级电路的输入电容。VDD VDD 0 DC 5 和 VSS VSS 0 DC 0 分别定义了5V的电源电压和地。

- 输入激励:

VIN I 0 PULSE(0 5 1n 100p 100p 10n 20n) 定义了一个脉冲电压源,产生一个从0V跳变到5V、延迟1ns开始、上升/下降时间为100ps、脉冲宽度10ns、周期为20ns的方波信号。

- 仿真控制:

.TRAN 10p 40n 指令要求HSPICE执行瞬态仿真,输出步长为10ps,总仿真时长为40ns。这类仿真对于验证数字电路的时序和开关特性至关重要。

3. 运行仿真与查看结果

在命令行中,使用以下命令启动HSPICE仿真:

hspice -i test.sp

仿真完成后,会在当前目录下生成一系列结果文件,例如:

test.tr0:包含瞬态仿真波形数据。test.st0:包含仿真状态信息。test.ic0:包含初始条件信息。test.pa0:包含参数分析信息。

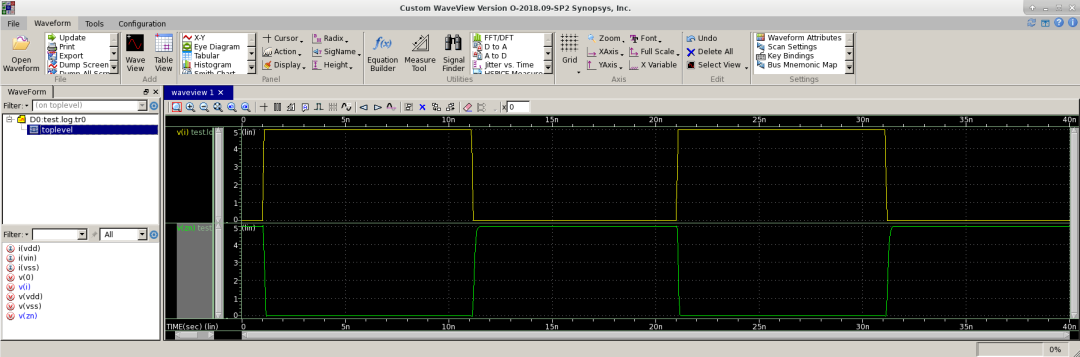

我们可以使用HSPICE自带的波形查看器wv(或其它兼容工具)打开test.tr0文件,直观地观察输入(I)与输出(ZN)的电压波形,从而分析反相器的传输延迟、上升/下降时间等动态特性。

通过上述步骤,我们完成了一个标准单元反相器从电路网表提取、测试平台构建到最终性能波形观测的完整HSPICE仿真流程。掌握这一方法,是进行更复杂数字模块或算法电路功能与性能验证的基础。 |