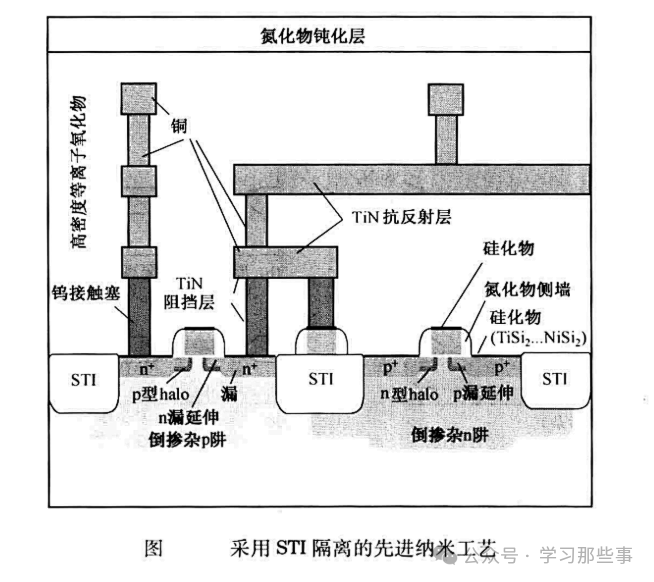

先进纳米CMOS工艺在继承基本CMOS架构基础上,通过引入浅沟槽隔离(STI)、倒掺杂阱(双阱)、高掺杂源漏延伸、自对准硅化物及大马士革铜互连等关键技术,实现了对亚100纳米节点的精准控制与性能跃升,成为延续摩尔定律的核心驱动力。

浅沟槽隔离(STI)以低温工艺替代传统LOCOS,通过高密度等离子体化学气相沉积(HDP)填充高深宽比沟槽,结合化学机械抛光(CMP)实现全局平坦化,有效抑制鸟嘴效应并提升有源区密度。其精度优势在45纳米以下节点尤为显著,成为纳米级器件隔离的标准方案。

倒掺杂阱(双阱)工艺通过n阱与p阱的独立优化,实现nMOS与pMOS器件性能的精准匹配。通过高能离子注入与低温推进技术,阱区掺杂峰值可精确控制在250-600纳米深度,横向扩散受限下器件间距得以缩小。同时,它结合抗穿通(APT)注入与体效应抑制技术,提升了器件对称性与跨工艺代兼容性,满足数模混合电路对阱区特性的严苛要求。

漏区延伸技术则通过高浓度掺杂(峰值达1×10²⁰~2×10²⁰原子/cm³)与氮化物侧墙工程,形成缓变结结构以降低结泄漏与热载流子效应。它配合离轴砷注入、深磷注入及halo掺杂技术,实现了沟道长度的精确控制与短沟效应的有效抑制。在3纳米以下节点,更通过三维结构(如FinFET、GAA)进一步优化电场分布,提升器件可靠性。

自对准硅化物(Salicide)工艺通过钛、钴、镍等难熔金属与硅的低温反应,在多晶硅栅及源漏区形成低电阻硅化物层(如TiSi₂、NiSi),将薄层电阻降至50Ω/□以下,显著降低RC延迟。而Ti/TiN薄膜在接触孔中既作为粘附层又兼具氧化阻挡功能,配合钨插塞填充技术解决了高深宽比接触的空洞问题,提升了互连可靠性。抗反射涂层(ARC)与有机ARC的应用则有效抑制光刻过程中的反射与散射,保障亚波长级图形的高精度转移,配合EUV光刻与多重曝光技术,实现7纳米及以下节点的特征尺寸控制。

大马士革铜互连工艺通过双大马士革(Dual Damascene)结构实现插塞与导线的同步沉积,避免了铝刻蚀的等离子体损伤与副产物残留问题。结合低k介质材料(如SiOCH)与铜的优异导电性,可将互连电阻降低25%~30%,同时减少线间电容与串扰噪声,提升电路速度并降低功耗。此外,铜的高电流密度耐受性有效抑制电迁移效应,延长了器件寿命,成为先进制程互连体系的标准方案。

这些技术的融合创新,使纳米CMOS工艺在性能、功耗、集成度三方面持续突破,为5G通信、人工智能、高性能计算等前沿领域提供了坚实的工艺基础,同时推动了三维集成、异构集成等新兴技术的发展,持续拓展摩尔定律的边界。

45nm以下节点的CMOS工艺选择与挑战

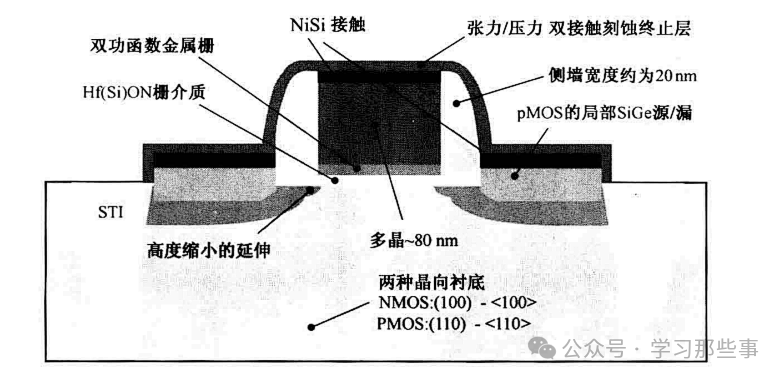

在45纳米以下CMOS工艺的极限挑战中,器件与互连的协同优化成为突破物理边界的关键。器件层面,阈值电压控制与载流子迁移率提升的矛盾尤为突出——栅耗尽效应随尺寸缩小加剧,驱动电流显著下降,这促使业界转向金属栅与高k介质组合方案。

Intel率先采用后栅工艺,通过高ε介质如HfO₂与金属栅(如钨/钛氮化物)降低栅泄漏电流,同时结合功函数调谐技术实现阈值电压精准控制。当前研究聚焦于金属栅材料创新,如钌、钼等难熔金属,及其与高k介质的界面工程,通过引入超薄界面层(如SiO₂或Al₂O₃)减少界面态密度,提升器件可靠性。

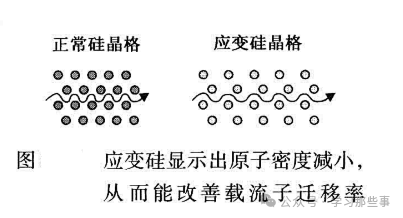

此外,应变硅技术通过SiGe缓冲层或嵌入式eSiGe结构引入压应力,显著提升pMOS空穴迁移率,而张应力则通过碳掺杂或氮化硅应力层优化nMOS性能。结合晶向工程(如(110)衬底)进一步平衡双极型器件特性,可实现驱动电流提升40%以上。

三维结构创新方面,FinFET与GAA(环栅)架构通过多栅控制增强电场调制能力,有效抑制短沟效应与泄漏电流。在3纳米节点以下,纳米片与纳米线结构成为主流,配合叉片式(forksheet)FET等创新设计,实现了沟道厚度精确控制与寄生电容的降低。这些结构通过并联沟道设计提升驱动电流,同时结合高迁移率通道材料(如SiGeSn合金)与应变工程,持续突破迁移率极限。

互连层面,低k介质与空气间隙技术成为降低寄生电容的核心手段。超低k介质(k<2)如碳掺杂SiCOH与多孔SiO₂通过减少分子极性来降低介电常数,而空气间隙技术通过去除层间介质实现k≈1,但需解决机械强度与可靠性挑战。当前研究聚焦于空气间隙与低k介质的复合应用,结合混合键合技术实现高密度互连。

铜互连方面,超薄阻挡层(如TaN/Ru)与无阻挡层工艺研究旨在降低接触电阻。而钴、钌等替代金属因其抗电迁移特性成为7纳米以下节点的候选材料,配合低k介质优化可实现互连延迟降低与功耗控制。

这些技术的融合创新不仅延续了摩尔定律,更推动了三维集成、异构集成等前沿方向的发展。例如,通过硅通孔(TSV)与混合键合实现芯片堆叠,结合先进封装技术提升系统集成度。同时,量子器件与神经形态计算等新兴领域对超低功耗、高精度器件的需求,正驱动CMOS工艺向更精细的物理极限与更智能的设计范式演进,持续拓展半导体技术的边界。

半导体制造工艺的演进是支撑整个数字世界的基石。欢迎在云栈社区分享你对前沿工艺技术的见解与思考。