在游戏、影视和显示领域,4K 分辨率已成为标配。今天,我们将探讨如何利用 FPGA 平台实现 4K 视频的输入、输出与实时处理。

从 HDMI 1.4 到 HDMI 2.0:瓶颈与突破

目前,大多数基于 HDMI 的 FPGA 图像处理方案通常遵循以下两种思路:

- 直接将 FPGA I/O 管脚配置为 TMDS 接收/发送模式。

- 通过外部的 HDMI PHY 收发芯片,实现并行视频数据与 TMDS 信号之间的转换。

这些方案在 HDMI 1.4 时代已经相当成熟,能够实现最高 4K@24Hz 或 1080p@120Hz 的视频输入输出。这样的性能足以满足多数中低速应用场景,例如工业检测或嵌入式显示屏。

然而,若要实现更流畅的 4K@60Hz 视频传输,就必须跨越到 HDMI 2.0 标准。

挑战:应对 18 Gbps 的带宽压力

HDMI 2.0 标准要求高达 18 Gbps 的带宽,这远超过传统 FPGA I/O 所能承受的速率。在这种高带宽设计中,高速串行收发器(如 GTH/GTY)成为不可或缺的关键。

在这方面,AMD Artix™ UltraScale+™ FPGA 表现突出。其内部集成的 GTH 收发器可支持最高 6 Gbps 的速率,完全能够胜任 4K@60Hz 的传输需求。这意味着,我们终于可以在单块 FPGA 上,完整地实现 HDMI 2.0 的 4K 视频链路。

架构设计:构建简洁高效的视频直通系统

本项目的目标是构建一个简洁高效的 4K 视频直通参考设计。简单来说,其流程为:从相机或笔记本电脑输入 HDMI 视频 → FPGA 处理 → 输出到显示器,从而实现高分辨率画面的实时显示。

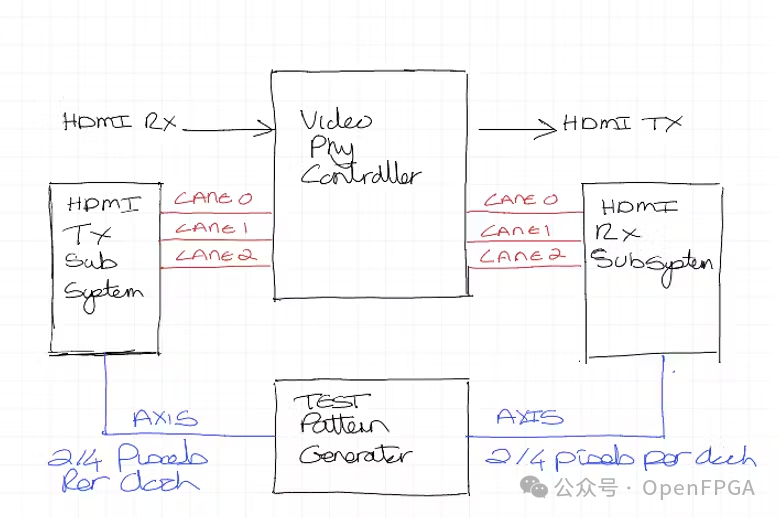

整个系统由以下几个关键模块组成:

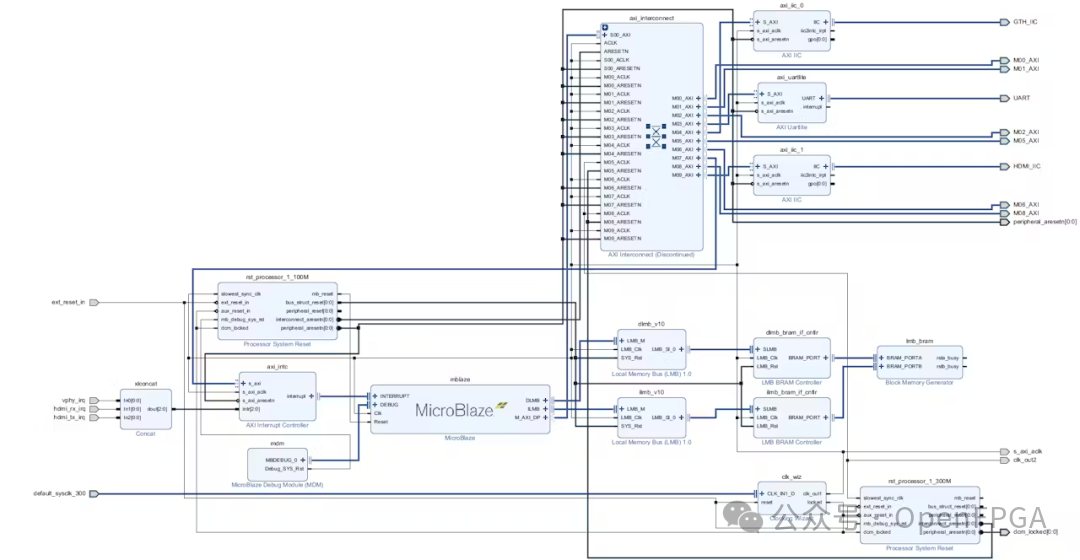

- AMD MicroBlaze™ 软核处理器:负责初始化与配置各个 IP 核;通过串口菜单提供简易的系统控制界面;控制时钟发生器和视频参数。

- HDMI RX 1.4 / 2.0 子系统:接收来自外部源(如相机/笔记本)的 HDMI 信号,并将 TMDS 信号解码为 FPGA 内部可处理的视频流格式。

- HDMI TX 1.4 / 2.0 子系统:将处理后的视频流重新编码为 TMDS 信号,并输出到 HDMI 显示设备(如 4K 显示器)。

- 视频物理层控制器(PHY Controller):负责管理 HDMI 子系统与 FPGA 内部 GTH 收发器之间的接口,确保数据传输与时钟同步。

- 视频测试模式生成器(TPG):当没有外部视频输入时,可自动生成测试图案,便于验证 HDMI 输出链路是否工作正常。

实践:基于 AMD 官方参考设计的实现与调整

整个方案的实现基于 AMD 官方的 HDMI 参考设计,并在此基础上进行了调整与优化,包括增加了对 HDMI 2.0 帧率与分辨率的支持,通过 MicroBlaze 实现灵活的软件可配置控制,并充分利用 Artix UltraScale+ 的 GTH 特性以实现稳定的高速传输。

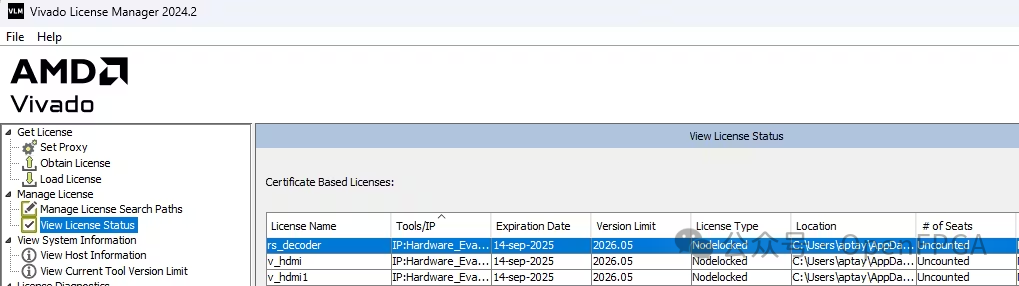

许可证准备

在开始设计前,需要确保 Vivado 软件拥有有效的许可证。如果没有,可以通过官网申请试用。

创建参考设计

-

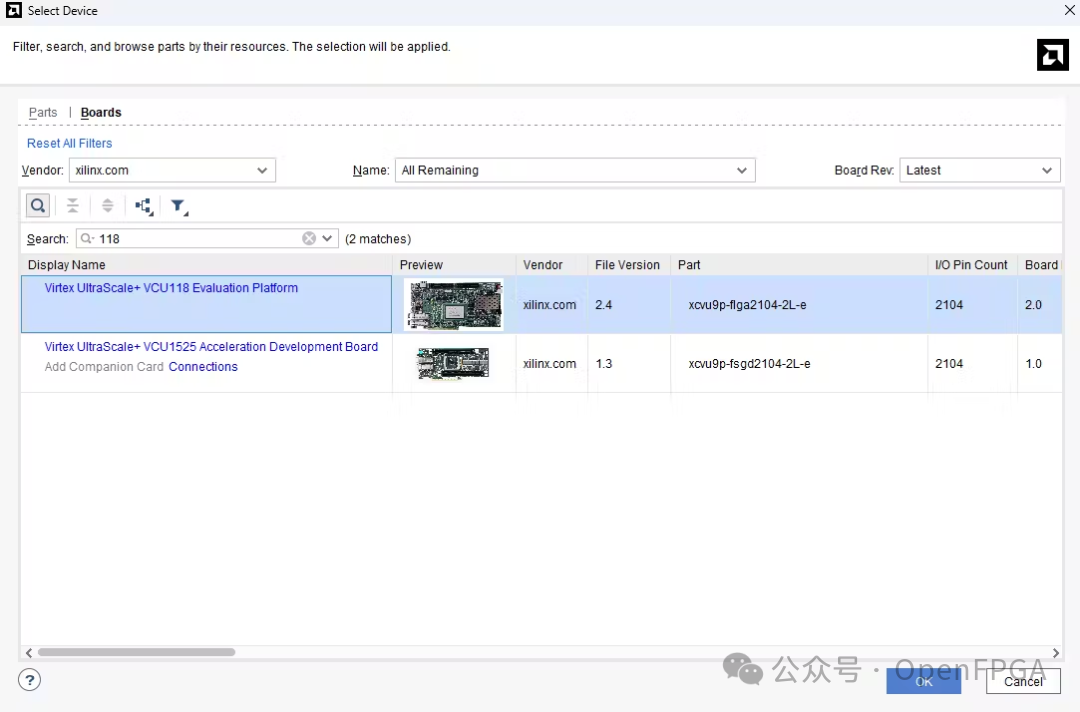

在 AMD Vivado™ 设计套件中,首先创建一个针对 VCU118 评估板的新项目。

-

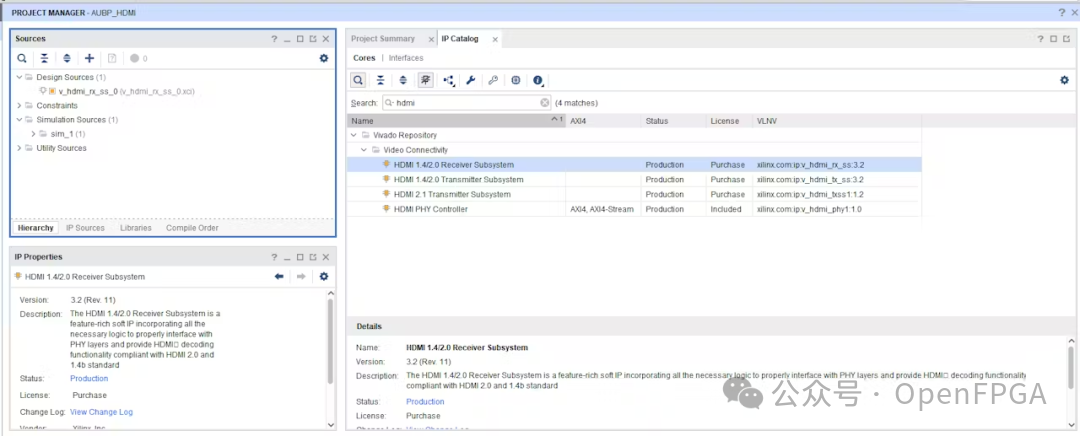

项目打开后,在 IP Catalog 中找到并添加 HDMI 1.4/2.0 Receiver Subsystem IP 核。

-

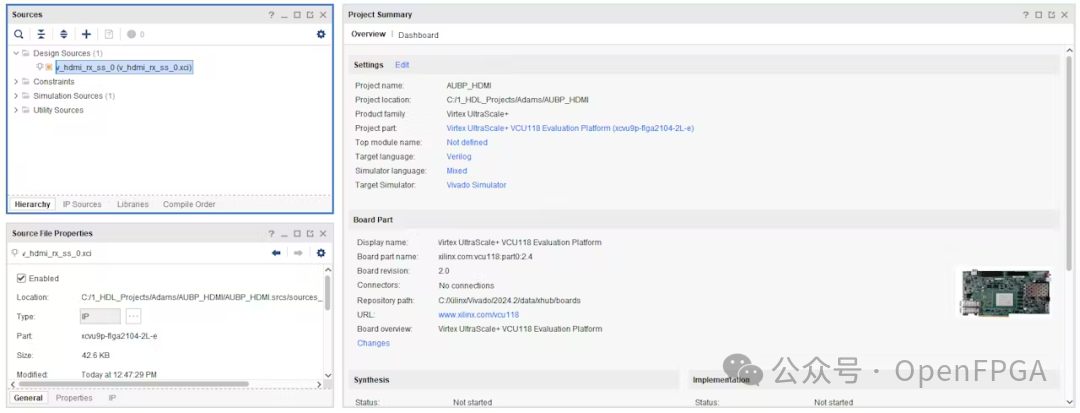

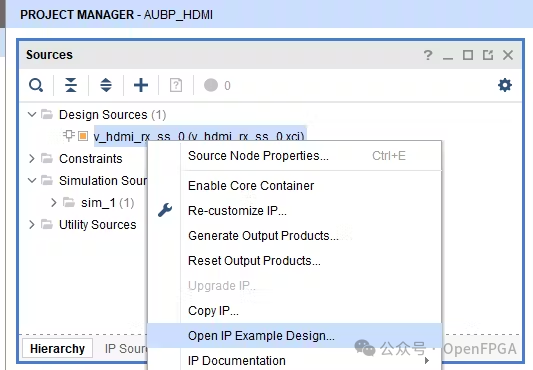

在 Sources 面板中选中该 IP 核。

-

右键单击选定的 IP,然后选择 Open IP Example Design。

-

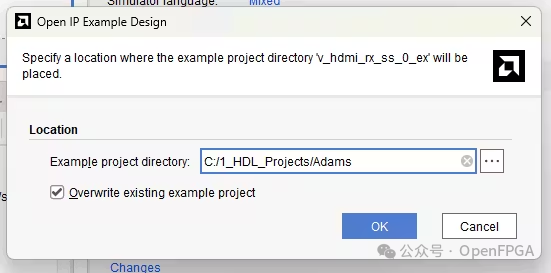

在弹出的对话框中,选择存储示例项目的位置。

-

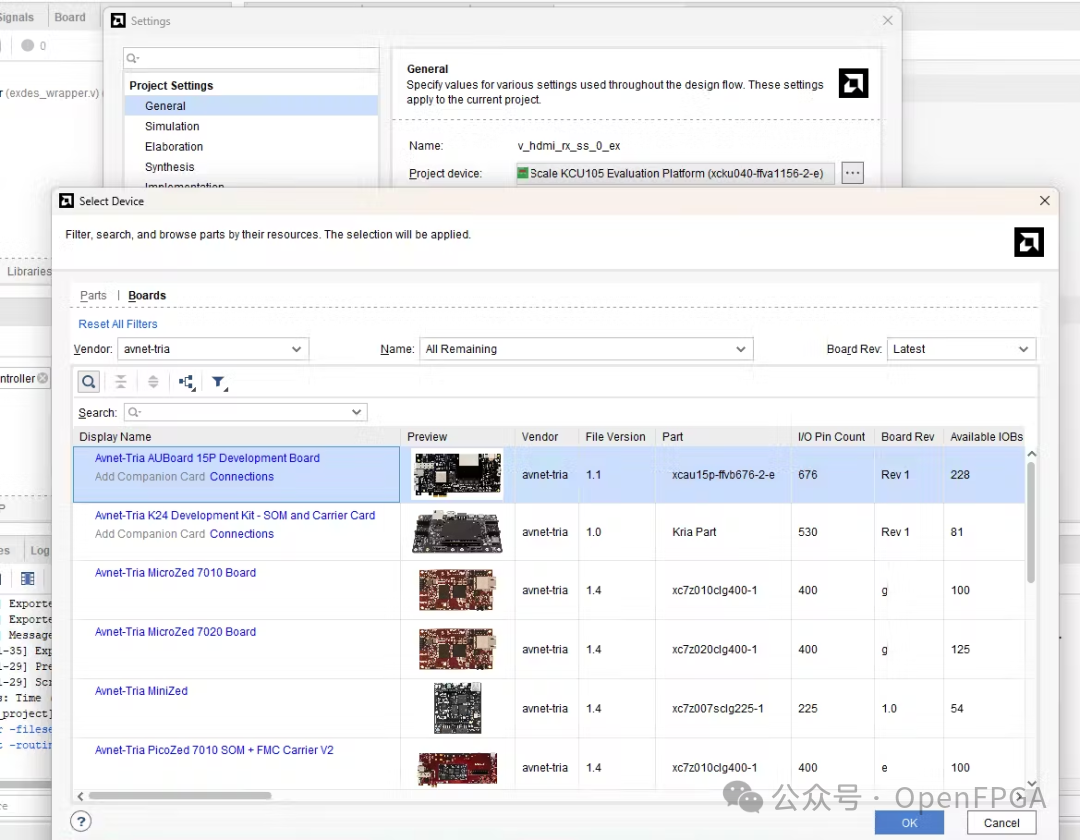

示例设计会针对 VCU118 打开。我们需要将其目标板更改为自己的开发板(例如 AUBoard-15P)。

-

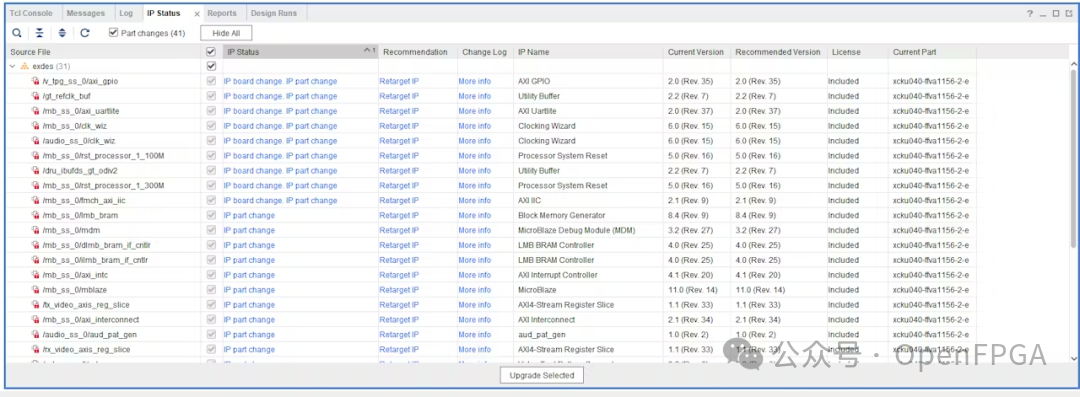

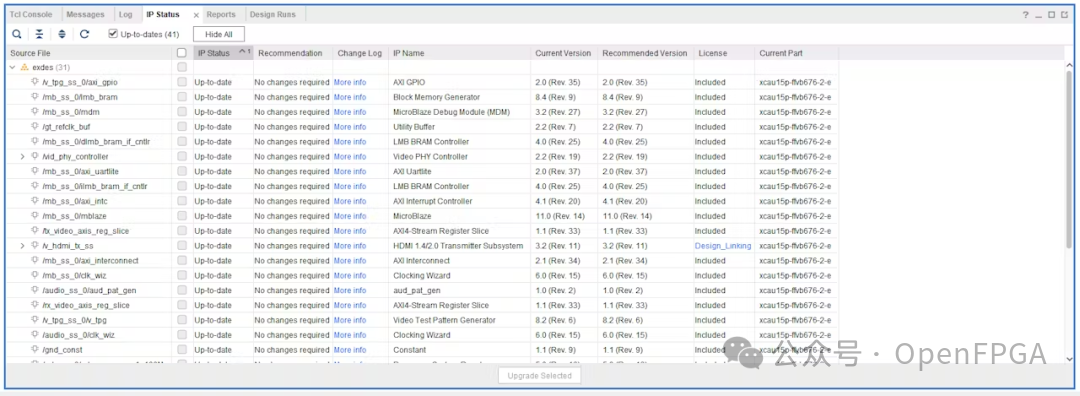

更换 FPGA 芯片后,部分 IP 会被锁定,需要通过 Report IP Status 工具进行更新。

-

更新选定的 IP 并重新运行 IP 状态报告,确认所有 IP 状态均为最新。

-

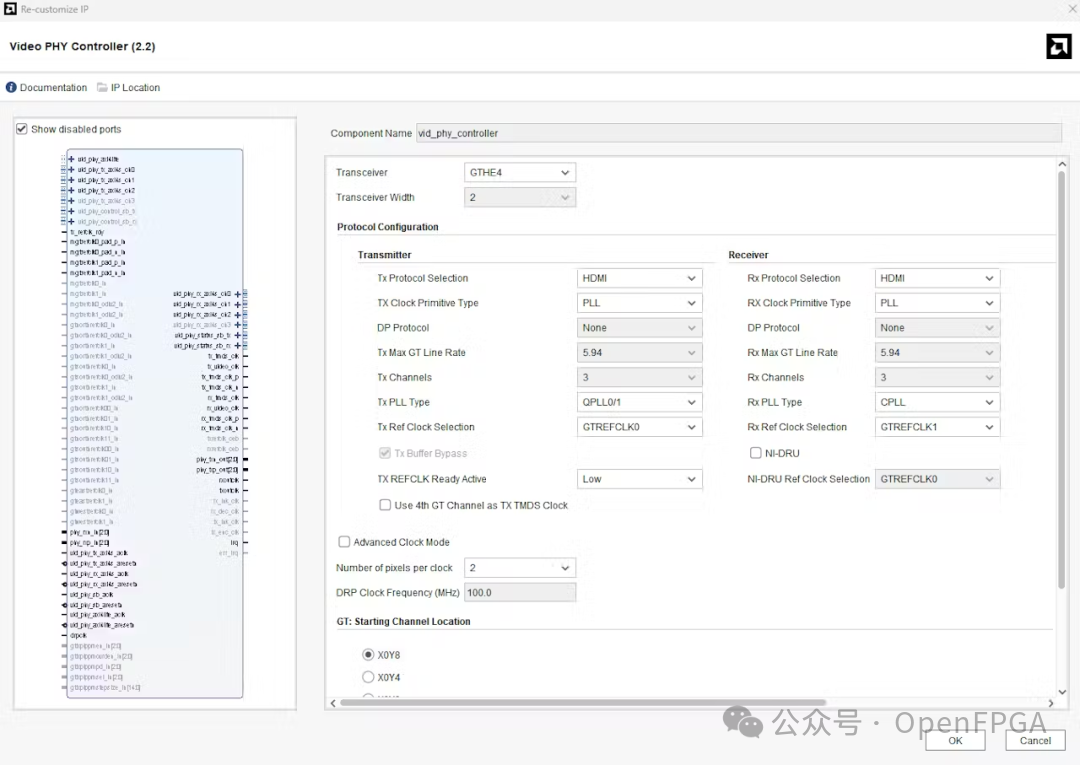

接下来,需要对 Video PHY Controller 进行修改,以适配 AMD Artix™ UltraScale+™ 设备上的 GTHE4 收发器。请确保将时钟原语类型设置为 PLL。

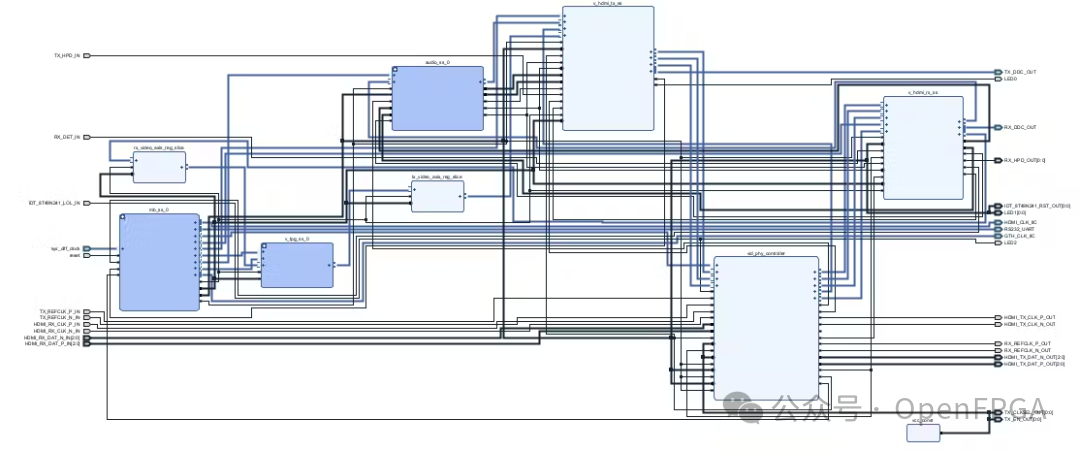

完成上述步骤后,设计的顶层架构应如下图所示。视频数据通过 TPG(测试模式生成器)从 HDMI Rx 传输到 HDMI Tx。

为了支持最高的分辨率和帧率,视频像素以每时钟 2 像素或每时钟 4 像素的速率进行传输(具体取决于模块配置)。本设计中使用了 DisplayPort 转 HDMI 转换器作为外部发送路径,并使用 TMDS 重定时器作为接收器。

在 FPGA 内部,Video PHY Controller 与 GTH 收发器相连,为 HDMI 发送端和接收端各提供 3 条数据通道。这些通道与 HDMI 子系统相互连接,构成了完整的视频收发链路。

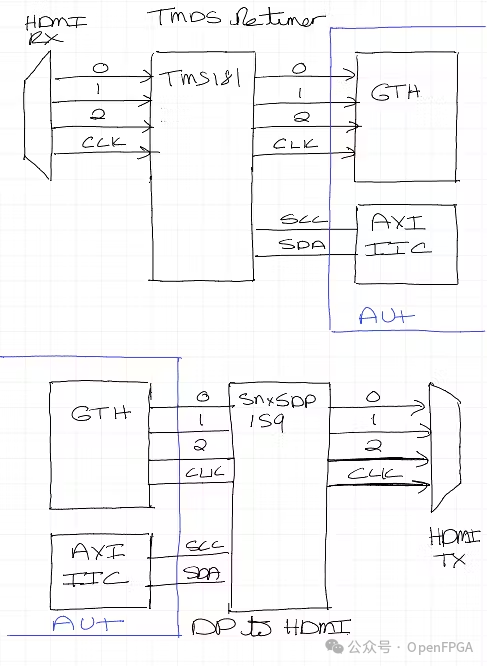

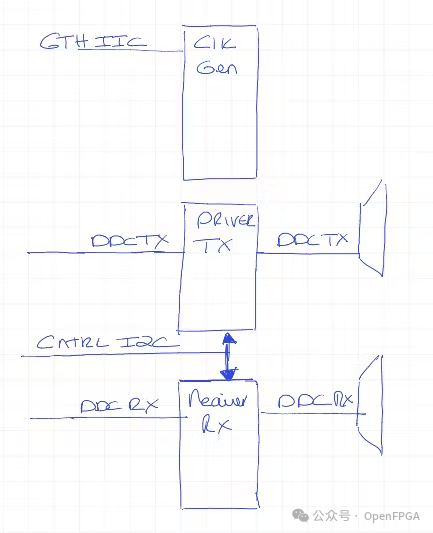

HDMI 解决方案需要多个 I2C 接口。一些用于连接 HDMI Tx 和 Rx 的 DDC(显示数据通道),这些接口可能直接来自 HDMI Tx/Rx 子系统。另外还需要 I2C 接口来配置 SN65DP159RGZT 和 TMS181(驱动和均衡芯片),以改善输入和输出的 GTH 信号质量。

此外,我们还需要第二个 AXI I2C 连接到板上的时钟发生器芯片,该芯片负责提供 GTH 收发器所需的参考时钟。本次设计中所用板卡的 I2C 网络连接关系如下图所示。

在 AMD MicroBlaze™ 处理器系统模块内,需要添加第二个 AXI I2C IP 核,并将其信号连接到外部引脚。

修改相应的约束文件后,就可以对设计进行综合与实现了。

软件开发与应用程序创建

-

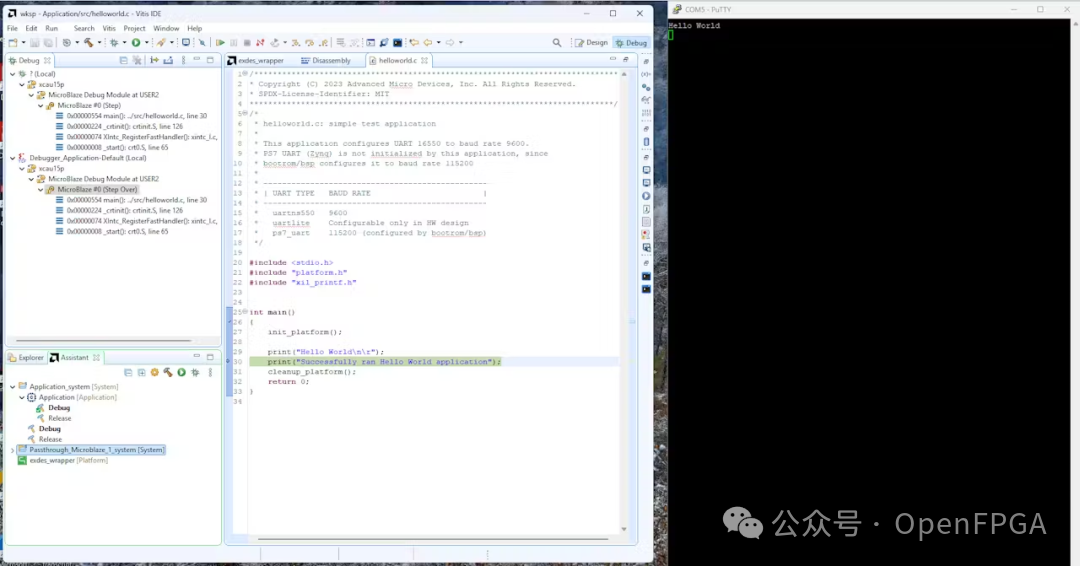

从 Vivado 导出硬件平台描述文件(XSA)。然后,在 AMD Vitis™ 统一软件平台中创建一个简单的 Hello World 应用程序。编译并运行该程序,以验证我们能够在 MicroBlaze 处理器上成功生成并执行代码,这属于基本的计算机基础操作。

-

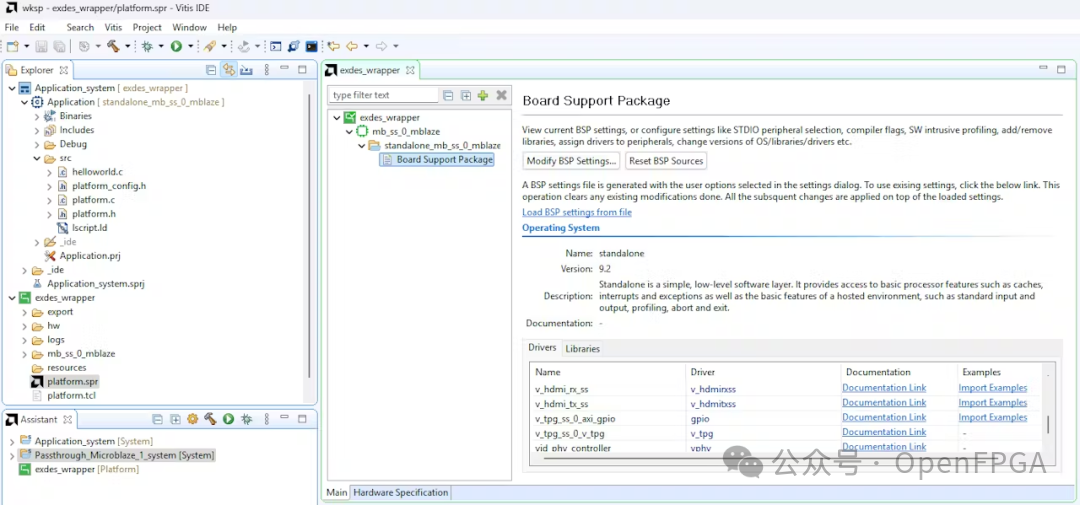

确认系统可行后,开始为 HDMI 直通功能创建应用软件。在平台工程中,打开 .spr 文件并选择 Board Support Package (BSP)。在 BSP 设置中,找到 v_hdmi_rx_ss 驱动程序,然后选择 Import Examples。

-

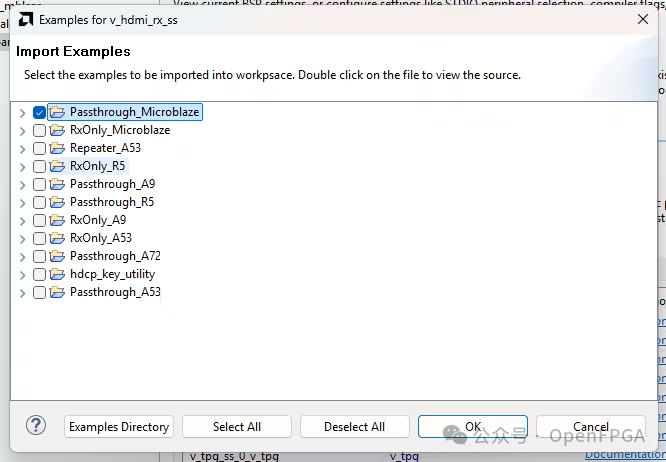

这将提供一系列应用示例。在本例中,我们选择 Passthrough_MicroBlaze。

-

应用程序创建好后,需要对主示例代码进行一些修改,以确保正确配置我们板卡上使用的时钟发生器芯片。主要的修改是调整条件编译,改变需要编程的 I2C 时钟发生器类型。默认软件预期编程 Si5324 设备,而我们的开发板使用的是瑞萨 8T49N24 时钟发生器。

int I2cClk(u32 InFreq, u32 OutFreq)

{

int Status;

//#if (!defined XPS_BOARD_ZCU104)

#if (defined XPS_BOARD_ZCU104)

/* Free running mode */

if (InFreq == 0) {

Status = Si5324_SetClock((XPAR_IIC_0_BASEADDR),

(I2C_CLK_ADDR),

(SI5324_CLKSRC_XTAL),

(SI5324_XTAL_FREQ),

OutFreq);

if (Status != (SI5324_SUCCESS)) {

xil_printf("Error programming SI5324\r\n");

return 0;

}

}

/* Locked mode */

else {

Status = Si5324_SetClock((XPAR_IIC_0_BASEADDR),

(I2C_CLK_ADDR),

(SI5324_CLKSRC_CLK1),

InFreq,

OutFreq);

if (Status != (SI5324_SUCCESS)) {

xil_printf("Error programming SI5324\r\n");

return 0;

}

}

#else

/* Reset I2C controller before issuing new transaction.

* This is required torecover the IIC controller in case a previous

* transaction is pending.

*/

XIic_WriteReg(XPAR_IIC_0_BASEADDR, XIIC_RESETR_OFFSET,

XIIC_RESET_MASK);

/* Free running mode */

if (InFreq == 0) {

Status = IDT_8T49N24x_SetClock((XPAR_IIC_0_BASEADDR),

(I2C_CLK_ADDR),

(IDT_8T49N24X_XTAL_FREQ),

OutFreq,

TRUE);

if (Status != (XST_SUCCESS)) {

print("Error programming IDT_8T49N241\r\n");

return 0;

}

}

/* Locked mode */

else {

Status = IDT_8T49N24x_SetClock((XPAR_IIC_0_BASEADDR),

(I2C_CLK_ADDR),

InFreq,

OutFreq,

FALSE);

if (Status != (XST_SUCCESS)) {

print("Error programming IDT_8T49N241\r\n");

return 0;

}

}

#endif

return 1;

}

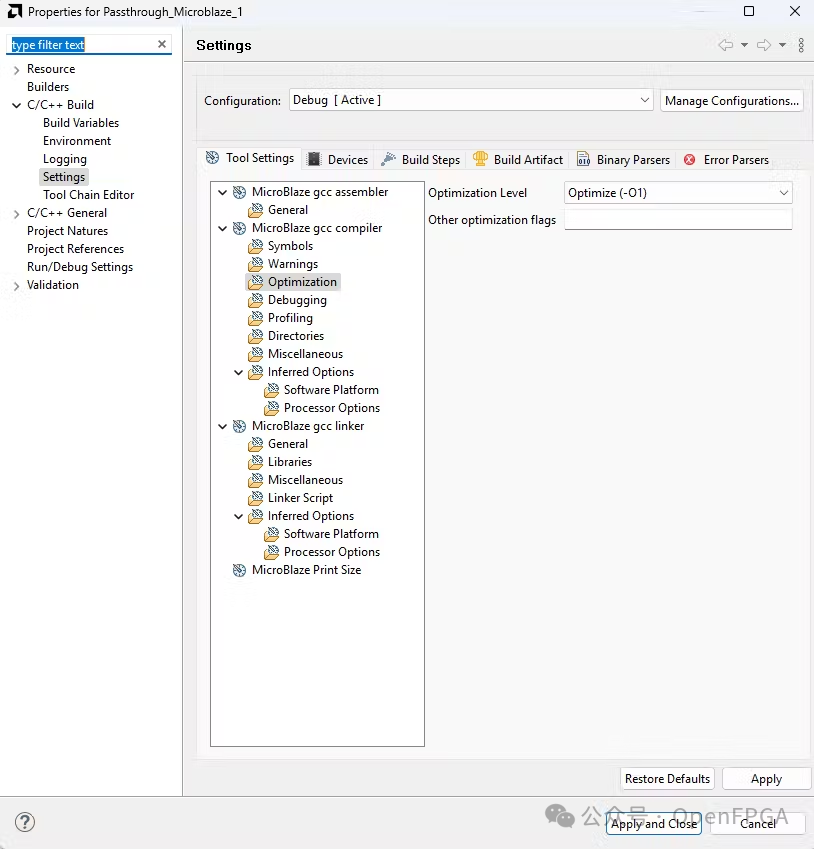

- 为了确保软件应用程序能够适配 MicroBlaze 处理器提供的 256KB 局部内存,需要将编译器的优化级别设置为 O1。

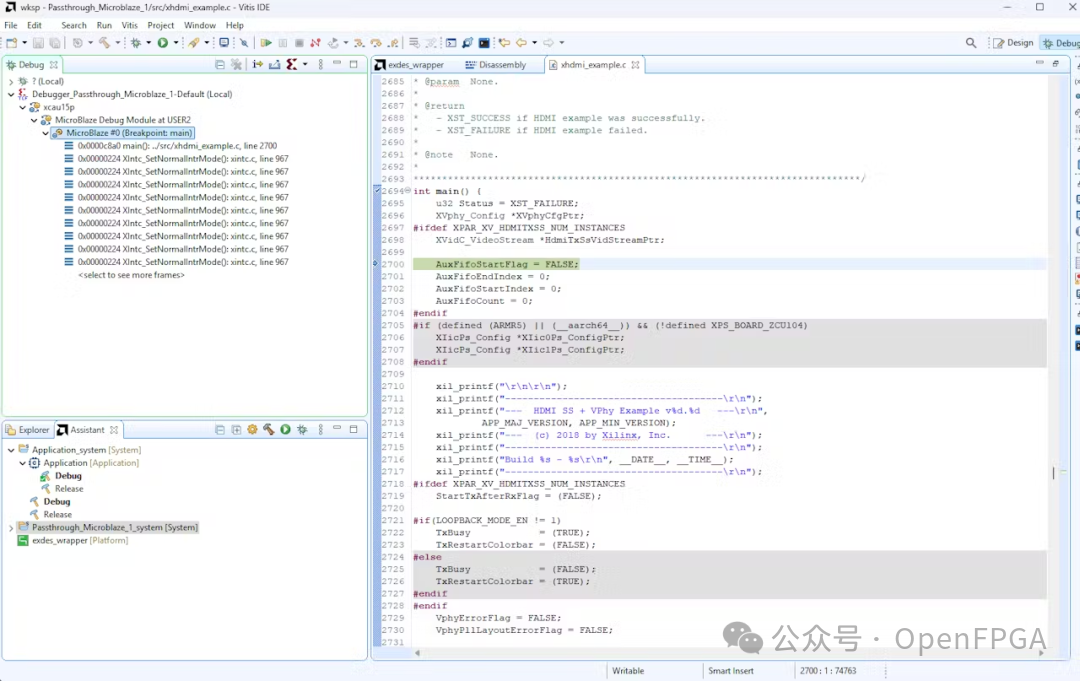

完成这些更改后,即可构建应用程序并在开发板上进行调试。完整的源代码可以在相关的 开源项目 仓库中获取。

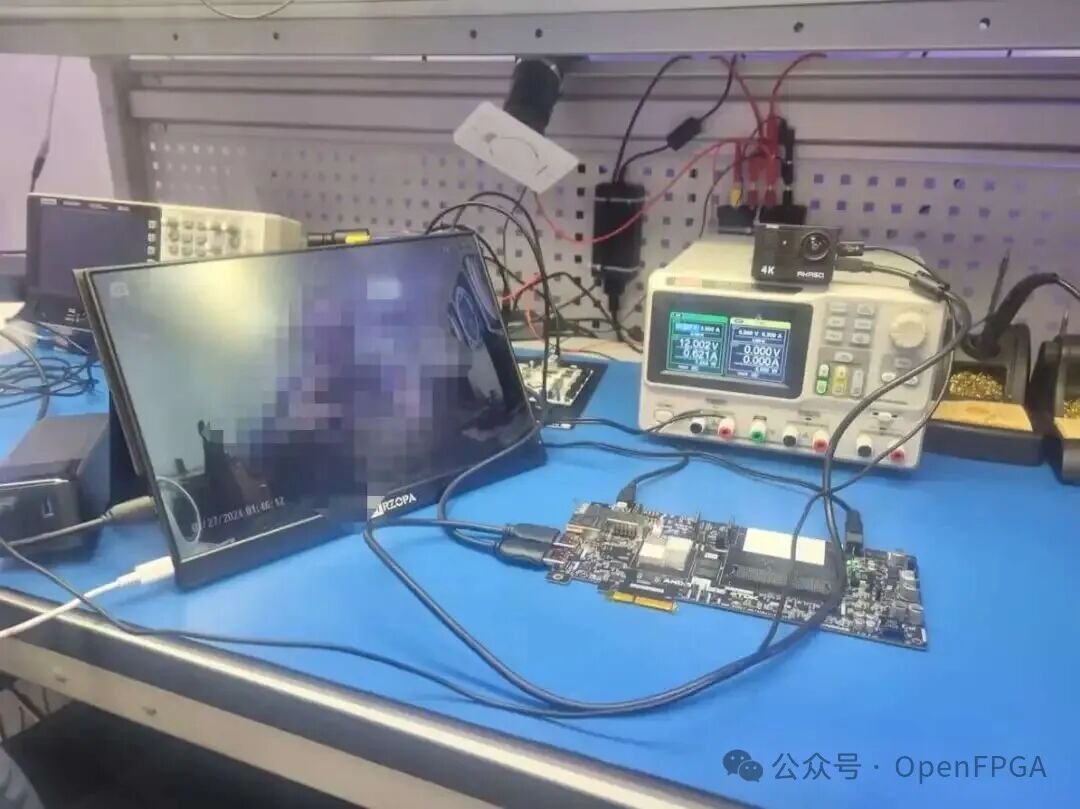

下板测试与验证

测试环境搭建相对简单。我们需要一个 HDMI 信号源和一个 HDMI 显示设备。初始测试使用了支持 4K 的显示器、一台小型 1080p 显示器作为接收端,以及一台可切换输出模式的 4K 运动相机作为信号源。

将应用程序下载到 FPGA 开发板并运行调试。

运行应用程序,将 HDMI 源和接收器连接到开发板,并将信号源分辨率设置为 1080P。此时,显示器上应能正确显示传输的图像。

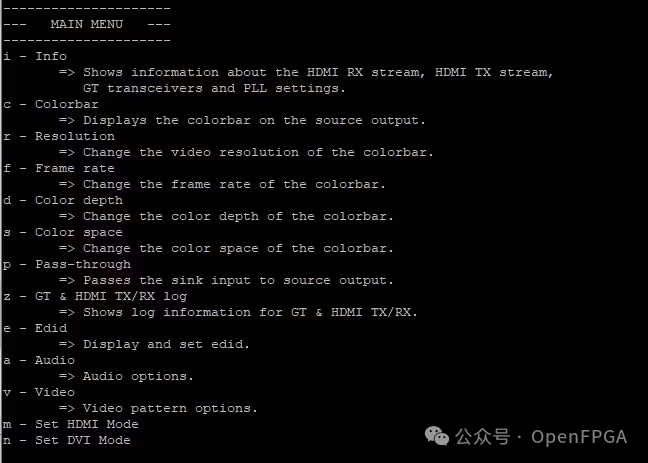

应用程序会通过板载 UART 输出一个交互菜单。通过此菜单,可以控制运行在 MicroBlaze 处理器上的应用程序,并提取关于图像处理流水线的配置和性能信息。

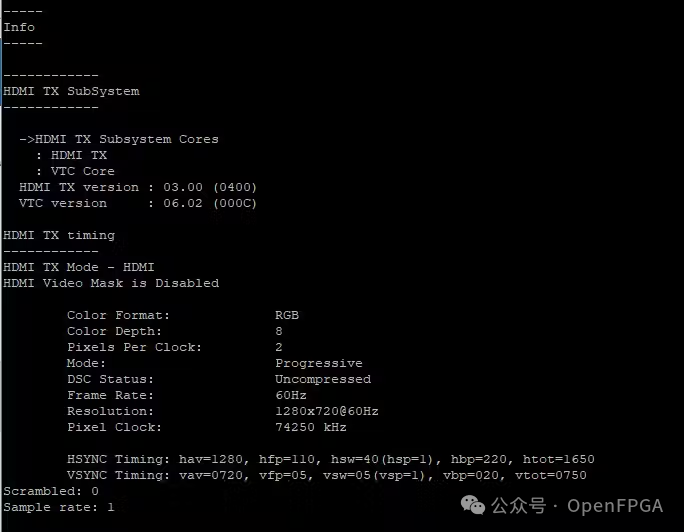

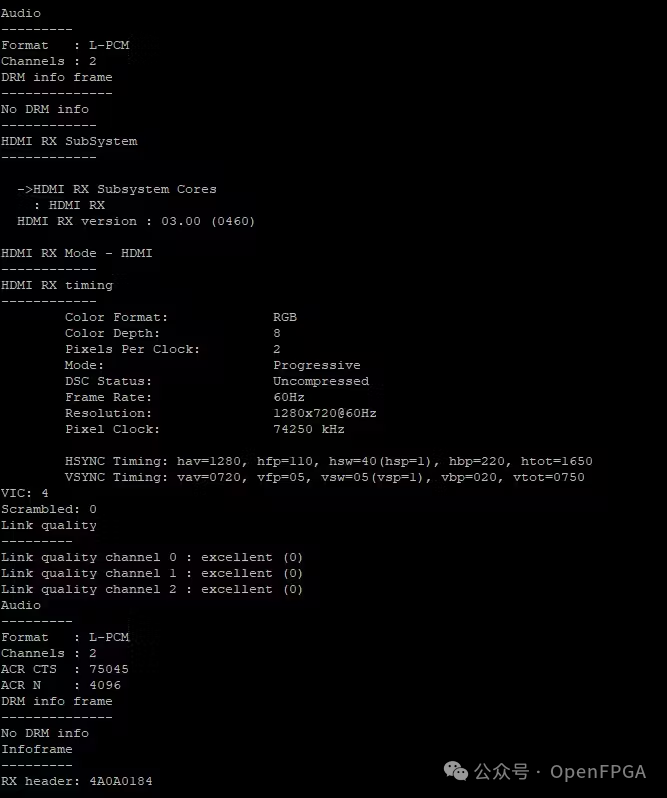

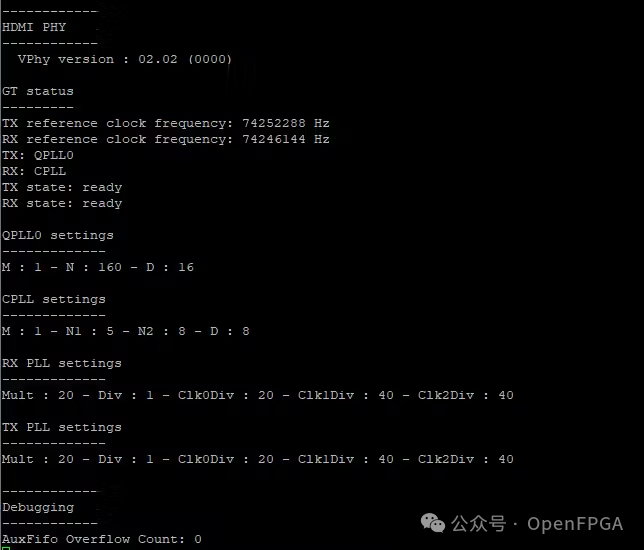

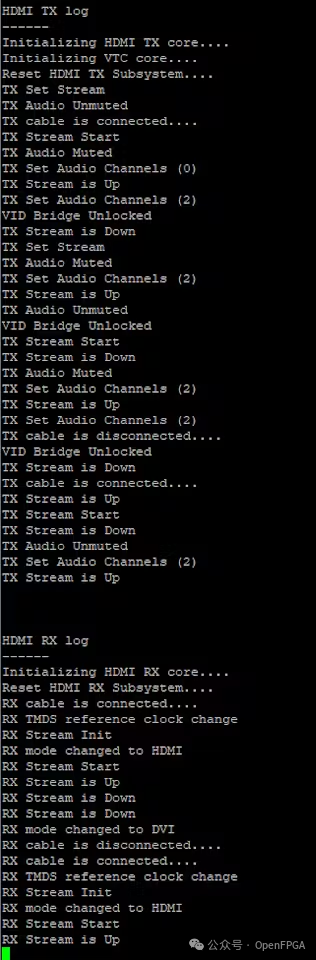

按下 i 键,终端将显示 HDMI TX 和 RX 子系统的详细信息。

我们还可以通过终端提取 GTH 收发器及 HDMI 链路的运行日志。

最后,将 HDMI 接收器更换为支持 4K 的显示器,即可看到系统更新并输出 4K 分辨率。

总结与展望

这套设计成功在单片 AMD Artix UltraScale+ FPGA 平台上实现了稳定的 4K@60Hz 视频输入输出直通功能,为高性能视觉系统、视频采集卡、专业显示控制器等应用提供了有力的硬件支撑。

过去,4K 视频处理常被视为 GPU 或专用 ASIC 的领域。如今,借助现代 FPGA 强大的可编程逻辑与高速收发器,复杂的 4K@60Hz 视频系统已能在单芯片上灵活实现。未来,在此基础上可以进一步扩展功能,如视频叠加、AI 视觉检测、实时色彩空间转换或 HDR 动态调节等,这些都可以通过定制的硬件逻辑实时完成,满足更苛刻的应用需求。完整的参考设计已开源,可供开发者在云栈社区等平台进一步交流与探讨。

参考设计仓库:

https://github.com/ATaylorCEngFIET/4K-at-60Hz