在 FPGA 项目里,有一句话几乎人人都听过:

“逻辑没问题,时序过不了。”

《高性能 FPGA 系统:时序设计与分析》这本书,关注的正是 FPGA 工程中最核心、也最折磨工程师的部分——时序。

它不是一本教你“怎么写 RTL”的书,而是一本回答:

为什么设计在低频能跑,高频就崩?

约束到底该怎么写,工具到底在分析什么?

时序收敛到底是“调参数”,还是“改架构”?

这本书在 FPGA 技术书里的定位

一句话概括:这是一本专门讲“FPGA 为什么跑不快,以及怎么让它跑快”的工程书。

它的特点非常明确:

- 以 Xilinx FPGA 为主要背景

- 聚焦时序参数、约束、分析、收敛

- 内容高度贴近 ISE / Xilinx 时序分析工具

- 面向追求性能而不是“能用即可”的工程师

如果你做过这些事,这本书基本对口:

- 拉高主频

- 做大规模并行 / 深流水

- 和 DDR、ADC、SerDes 打交道

- 被 Timing Report 折磨到怀疑人生

从设计流程开始,而不是直接丢公式

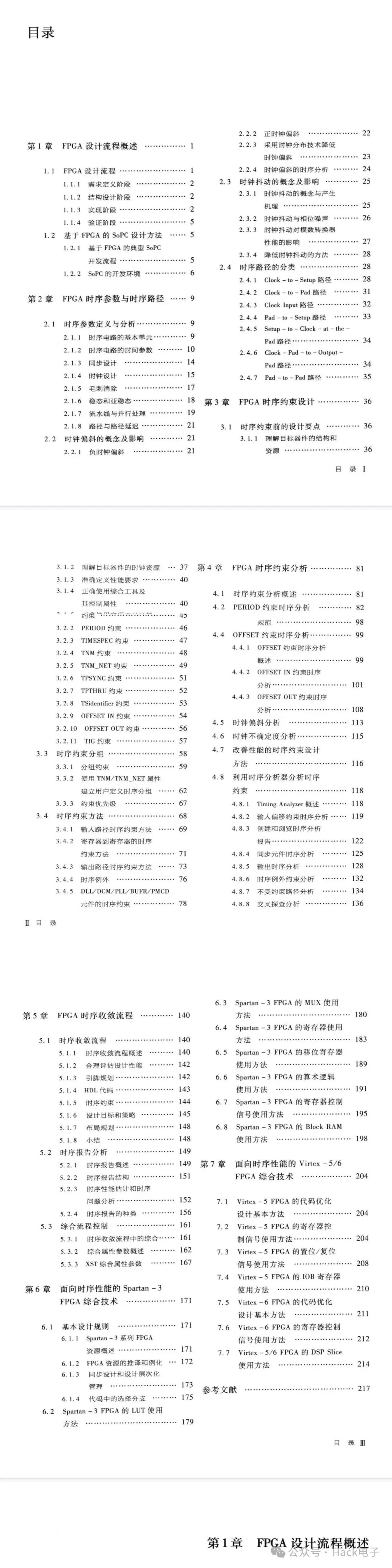

1️⃣ FPGA 设计流程:时序不是最后一步

第一章并没有直接进入时序公式,而是先把一个观点讲清楚:时序不是实现阶段才考虑的,而是从需求和结构阶段就决定了上限。

书中从工程流程角度拆解:

- 需求定义阶段:性能目标是否可实现

- 结构设计阶段:是否为时序友好架构

- 实现阶段:综合与布局布线的影响

- 验证阶段:时序是否真的被验证

同时引入 SoPC(System on Programmable Chip)的整体设计视角,而不是孤立看某一段逻辑。想系统掌握这些底层逻辑与工程原则,需要持续学习和交流。

时序基础:工程师必须“真的懂”的那部分

2️⃣ FPGA 时序参数与路径,不只是 setup / hold

第二章是全书的基础,但并不“基础”。它系统梳理了:

- FPGA 时序电路的基本单元

- 建立时间、保持时间的工程含义

- 同步设计的真正约束条件

- 流水线与并行对时序的本质影响

特别值得一提的是:

- 稳态与亚稳态并不是理论问题,而是实际系统可靠性问题

- 很多“偶现 bug”本质上都是时序边缘问题

3️⃣ 时钟的非理想性:工程现实 vs 理想模型

书中对时钟偏斜(Skew)和时钟抖动(Jitter)的讨论非常工程化:

- 正偏斜 vs 负偏斜,对时序的不同影响

- 时钟分布结构如何影响偏斜

- 抖动的来源、相位噪声的关系

- 为什么高性能系统里,时钟质量直接决定性能上限

这部分内容,对做高速接口和高频设计的人非常重要。

4️⃣ 时序路径分类:看懂报告的前提

很多工程师看 Timing Report,只看一行:Slack < 0 ❌,但并不知道这条路径属于哪一类。

书中详细拆解了 FPGA 中常见的时序路径类型,例如:

- Clock-to-Setup

- Pad-to-Setup

- Clock-to-Pad

- Pad-to-Pad

这些分类,是正确约束、正确分析的前提。

时序约束:不是“让工具闭嘴”

5️⃣ 约束之前,你应该先想清楚的事

第三章一开始就强调:约束不是用来“消警告”的,而是用来“描述真实系统”的。

在写约束之前,你需要理解:

- 目标器件的结构和资源

- 时钟资源的连接方式

- 性能目标是否合理

- 关键路径在哪里

这一章非常强调工程判断力,而不是死记语法。

6️⃣ Xilinx 时序约束:工程师常用的那一套

书中系统讲解了 Xilinx 约束体系中常见内容:

- PERIOD

- FROM-THRU-TO

- OFFSET IN / OUT

- TNM / TNM_NET

- 时序例外(False Path / Multi-cycle)

并且强调:

- 约束分组的重要性

- 约束优先级的实际影响

- 什么时候该“严格”,什么时候该“放行”

时序分析:读懂工具在“想什么”

7️⃣ Timing Analyzer 到底在干嘛?

第四章是很多工程师最需要、也最容易忽略的一章。它从原理层面解释:

- 周期约束是如何被分析的

- 偏移约束在分析中扮演什么角色

- 时钟偏斜和不确定度如何被引入

- 工具是如何计算 Slack 的

并通过 Timing Analyzer 的使用,教你:

- 如何定位关键路径

- 如何发现未约束路径

- 如何交叉探查 RTL 与物理实现

时序收敛:不是靠“多跑几次”

8️⃣ 时序收敛是一个工程流程

第五章明确指出:时序收敛不是工具问题,而是设计问题。

它从工程角度总结:

- 代码风格对时序的影响

- 综合策略对结果的影响

- 逻辑结构与布局的关系

- 哪些修改“治标”,哪些“治本”

这对反复调主频、调参数的工程师,非常有现实意义。

面向性能的综合:器件相关,但方法通用

最后两章以:

- Spartan-3

- Virtex-5 / Virtex-6

为例,讨论面向性能的综合技术。

虽然器件较老,但方法论仍然适用:

- 如何让综合器“理解你的意图”

- 如何利用器件结构提升时序

- 为什么同样的 RTL,不同系列结果差异巨大

这本书最适合谁?

非常适合:

- ✅ FPGA 工程师(中高级)

- ✅ 做高频、高速接口的设计人员

- ✅ 被时序问题反复折磨的人

- ✅ 想从“能跑”进阶到“跑得快”的工程师

不太适合:

- ❌ 只想学 HDL 语法的初学者

- ❌ 完全不关心性能的应用型设计

一句话总结

如果你已经写了不少 FPGA 代码,却仍然搞不定时序、看不懂报告、调不动主频,这本书值得你认真翻一遍。

资源信息

通过网盘分享的文件:高性能FPGA系统:时序设计与分析 (崔嵬,王巍编著).pdf

链接: https://pan.baidu.com/s/1rD-ppn9JB21jIO-f9cdS1w?pwd=open

提取码: open

说明:本文分享的学习资源仅供技术交流与学习使用,请支持正版书籍。版权归原作者及出版社所有,任何商业用途引发的责任均与分享者无关。

希望这份对《高性能 FPGA 系统:时序设计与分析》的解读能为你理清思路。FPGA 时序设计是一个需要深厚理论基础和丰富实战经验的领域,持续学习和与同行在如云栈社区这样的平台上交流,是突破瓶颈的有效途径。