在嵌入式开发中,GPIO(通用输入输出口)是最基础且使用最频繁的接口之一。无论是检测一个按键是否按下,还是控制一个LED灯的亮灭,都离不开对GPIO的操作。虽然从名称上看,GPIO的核心功能就是输入和输出,但根据其内部电路结构以及输入输出特性的不同,它可以被细分为八种工作模式。理解这些模式对于正确配置外设、实现稳定可靠的电路设计至关重要。

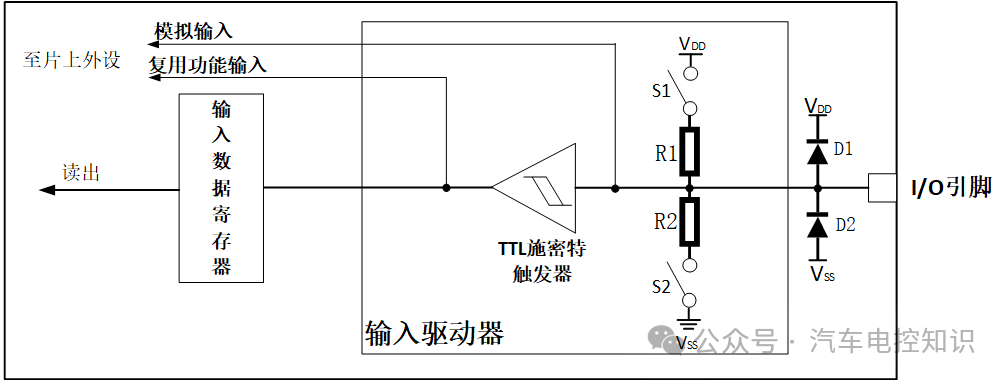

1. 输入模式的内部结构

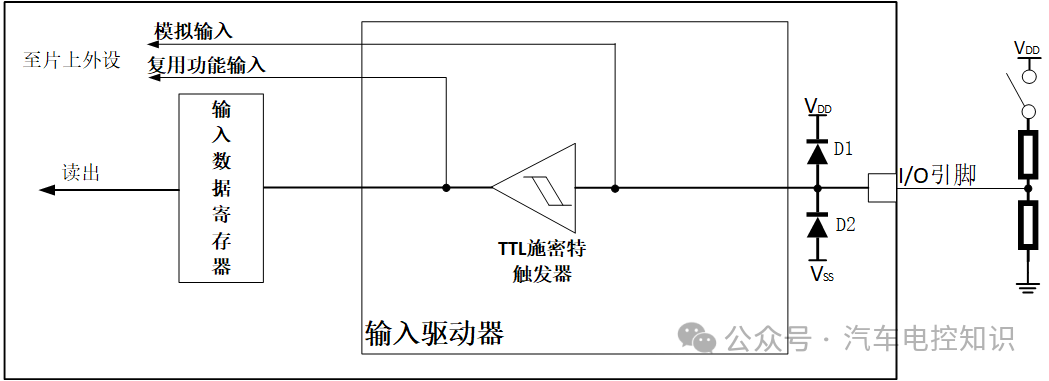

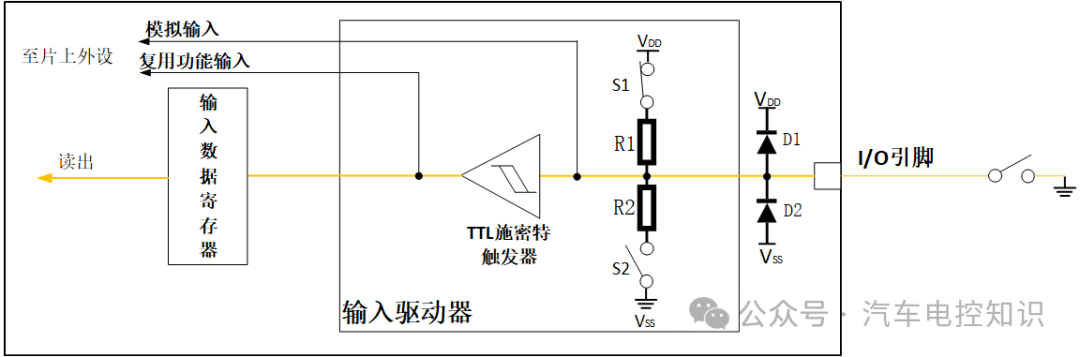

GPIO的输入和输出路径在芯片内部是相对独立的。在深入了解各种输入模式之前,我们有必要先剖析一下输入部分的内部结构。

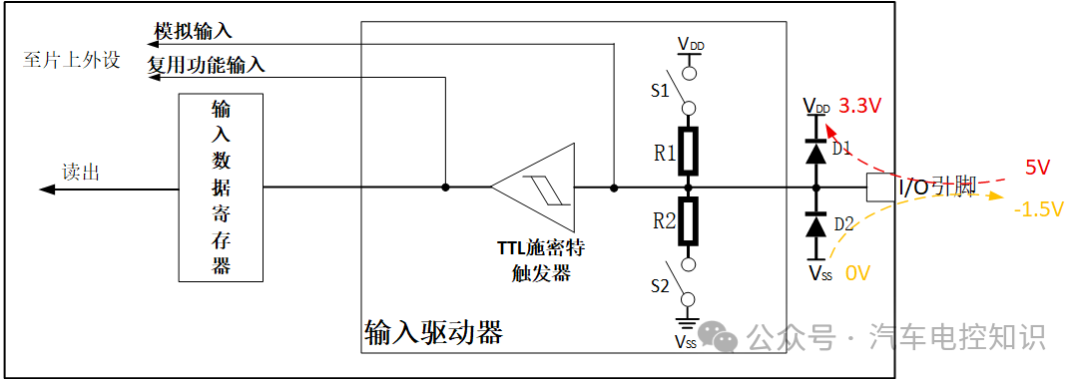

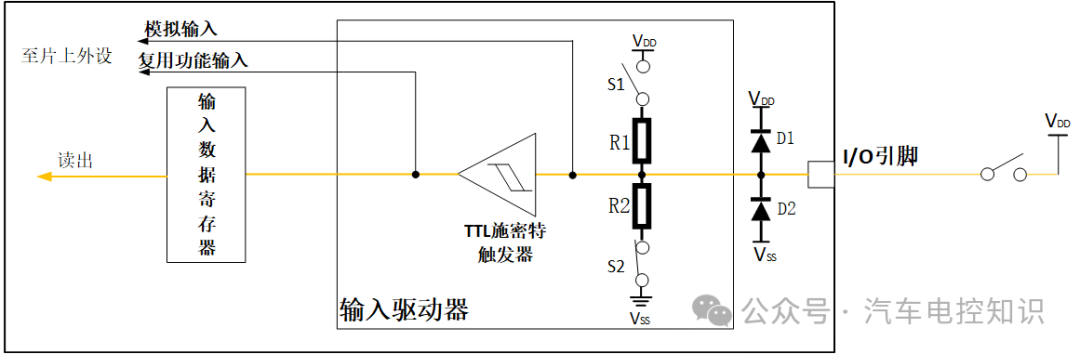

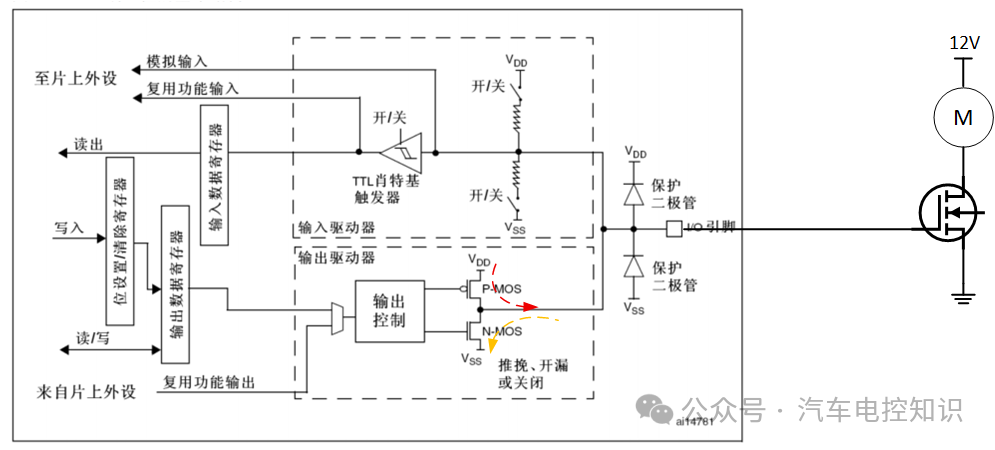

如上图所示,信号从GPIO引脚进入后,首先会经过两个保护二极管,它们分别连接到电源VDD和地VSS。这两个二极管构成了过压和负压保护电路。

假设主芯片的工作电压VDD是3.3V。如果外部输入了一个5V的高电平信号(过压),上方的二极管D1将会导通。由于硅二极管D1的导通压降约为0.7V,因此I/O引脚上的实际电压将被钳位在 3.3V + 0.7V = 4V。

反之,如果外部输入了一个-1.5V的负压信号(低于0V),下方的二极管D2将会导通。同样地,I/O引脚电压将被钳位在 0V - 0.7V = -0.7V。

通过这两个保护二极管,外部输入的电压范围(例如-1.5V~5V)被钳制在一个更窄、更安全的范围(-0.7V~4V)内,有效防止过压或负压损坏内部脆弱的CMOS电路。

信号通过保护二极管后,会经过可选的上拉或下拉电阻,然后送入一个TTL施密特触发器。触发器输出的稳定数字信号最终被存入输入数据寄存器,供CPU读取。

施密特触发器的输入端和输出端还分别引出了两条路径:一条通往模拟输入,另一条通往复用功能输入。这里我们重点探讨施密特触发器的作用,它是数字输入抗干扰的核心。

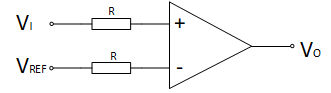

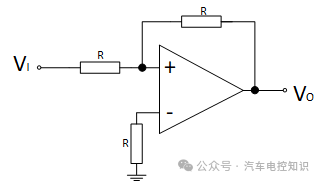

施密特触发器的基本原理源于电压比较器。一个普通的单限电压比较器如下图所示:

如上图,该比较器有一个参考电压VREF。当输入电压VI < VREF时,输出电压VO为低电平;当VI > VREF时,VO为高电平。由于只有一个阈值(VREF),故称为单限比较器。它可以将正弦波、三角波等转换为方波。

例如,对于3.3V系统,将VREF设为1.5V。当VI < 1.5V时,判定为低电平,输出0V;VI > 1.5V时,判定为高电平,输出3.3V。

这种设计在理论上是可行的,但在实际环境中,信号往往混杂着噪声干扰,导致波形在阈值电压附近产生抖动。如果使用单限比较器,这种微小的抖动就会导致输出电平的频繁翻转,从而产生采样错误和误动作。

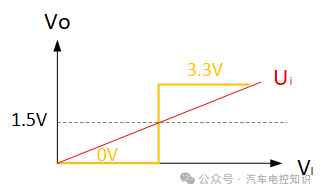

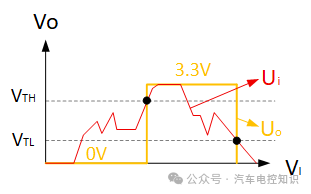

而施密特触发器在普通比较器的基础上,通过正反馈机制形成了两个不同的阈值:上阈值电压(VTH) 和 下阈值电压(VTL)。

两者之间的电压差构成了“滞后电压”或“回差电压”(ΔV = VTH - VTL)。只要噪声的幅度不超过这个滞后区间,输出状态就能保持稳定,不会因为信号在阈值附近的微小波动而频繁变化。

如上图所示,输入电压Ui从低电平开始上升,虽然在上升过程中有抖动,但只要Ui < VTH,输出Uo就一直保持低电平。只有当Ui超越VTH时,Uo才会翻转为高电平。

同理,当Ui从高电平下降时,即使因为抖动而低于VTH,只要未触及VTL,Uo仍保持高电平。直到Ui < VTL时,Uo才会翻转为低电平。

因此,施密特触发器本质上是一种具有滞回特性的比较器。它为GPIO口采样数字信号提供了强大的抗干扰能力,有效避免了因信号微小波动引起的误触发,这是嵌入式系统稳定性的重要基础,深刻体现了计算机基础中信号处理与噪声抑制的思想。

1.1 输入浮空模式

浮空输入模式下,芯片内部既不连接上拉电阻,也不连接下拉电阻。外部信号直接进入施密特触发器,经转换后送入输入数据寄存器。

这种模式适用于那些本身具有强驱动能力、或已在外部电路设置了明确上拉/下拉的信号源。例如,由另一块MCU或数字芯片直接驱动的信号线。浮空输入可以避免内部电阻对信号造成不必要的负载影响,确保接收信号的纯净性。

然而,浮空输入在实际项目中应用较少。对于常见的按键、拨码开关等无源器件,如果一端悬空,使用浮空模式会导致引脚在未按下时处于不确定的“悬浮”状态,极易受到电磁干扰而产生误触发。因此,对于此类器件,通常需要启用内部上拉或下拉电阻。

1.2 输入上拉模式

输入上拉模式,即在芯片内部通过一个电阻将引脚连接到VDD(电源),而没有下拉电阻。

在此模式下,当外部没有信号驱动时,引脚会被内部电阻“拉”至高电平(VDD)。当外部信号(如按键按下接地)将引脚主动拉低时,MCU便能检测到一个明确的下降沿或低电平状态。这种模式非常适合检测低电平有效的输入信号,例如一端接地的按键。

1.3 输入下拉模式

输入下拉模式与上拉模式相反,内部通过一个电阻将引脚连接到VSS(地),而没有上拉电阻。

在此模式下,引脚默认被拉低至地电平。当外部信号(如按键按下接电源)将引脚拉高时,MCU可检测到上升沿或高电平。这种模式适用于检测高电平有效的输入信号,例如一端接VCC的按键。

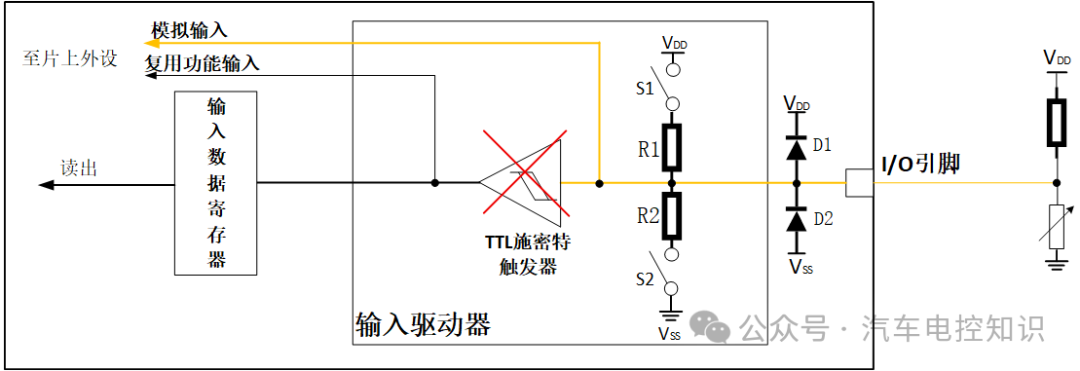

1.4 模拟输入模式

当需要从GPIO引脚采集模拟信号(如电压值)时,就需要使用模拟输入模式。在此模式下,内部的上拉和下拉电阻被断开,同时施密特触发器被关闭。模拟信号在施密特触发器之前就直接被引至芯片内部的ADC(模数转换器)模块。

这种模式专用于采集连续变化的模拟量,例如使用ADC读取电位器的电压、温度传感器(如NTC、PT100)的输出、或电池电压等。

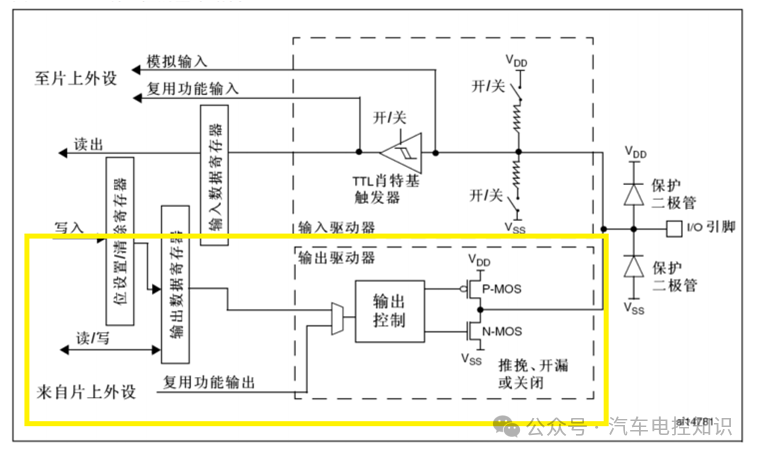

2. 输出模式的内部结构

输入和输出路径虽然独立,但它们最终共享同一个物理引脚,因此存在关联。例如,CPU输出一个电平时,理论上可以通过输入寄存器回读该电平;而在进行输入采样时,必须确保输出部分被禁用,否则内部输出的电平会干扰外部信号的正确读取。

下图展示了GPIO模块的完整框图,下半部分即为输出控制电路。

输出过程如下:CPU将需要输出的数据写入“输出数据寄存器”。该寄存器的值被送到“输出控制”电路,该电路通过控制一对P-MOS管和N-MOS管的通断,来决定最终输出到引脚的电平是高(VDD)还是低(VSS)。

2.1 开漏输出模式

在开漏输出模式下,P-MOS管始终保持关闭(断开)状态,输出仅由N-MOS管控制。

- 当N-MOS管导通时,引脚被拉低至VSS(低电平)。

- 当N-MOS管关闭时,引脚由于P-MOS管也关闭而处于“高阻”状态,电平由外部电路决定。

开漏输出的特点是只能主动输出低电平,无法主动输出高电平。高电平需要依赖外部上拉电阻来提供。这种模式非常适合用于需要“线与”逻辑的总线(如I2C),或者驱动一些低电平有效的器件(如LED阴极接地,阳极通过限流电阻接VCC,MCU引脚开漏输出低电平时LED点亮)。

2.2 推挽输出模式

推挽输出模式则充分利用了P-MOS和N-MOS这一对管子。

- 输出高电平时:P-MOS导通,N-MOS关闭,引脚直接连接到VDD。

- 输出低电平时:P-MOS关闭,N-MOS导通,引脚直接连接到VSS。

推挽结构能够提供较强的拉电流(电流从IO口流出)和灌电流(电流流入IO口)能力,可以主动而明确地输出高、低电平,驱动能力较强。它适用于直接驱动需要明确电平控制的数字器件,如LED(无需外部上拉)、数码管段选/位选、晶体管或MOS管的栅极等。

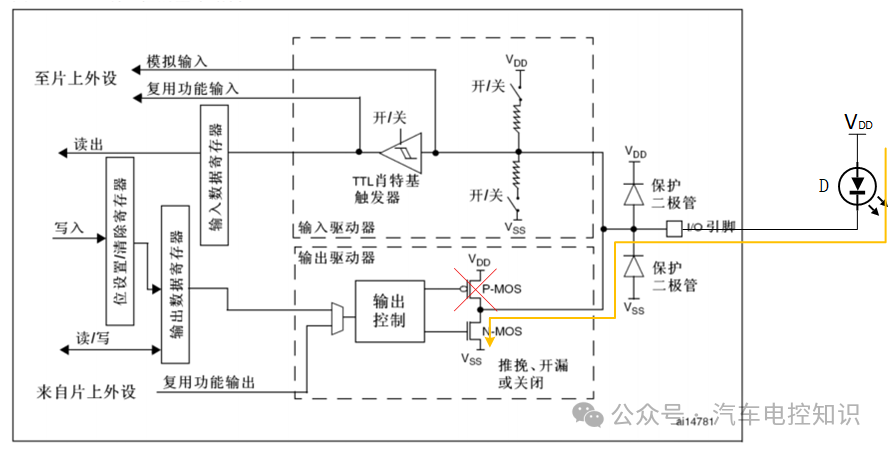

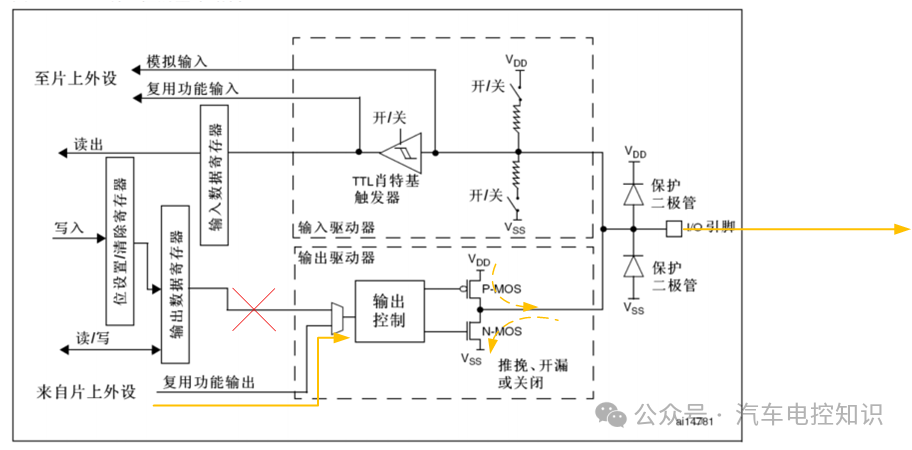

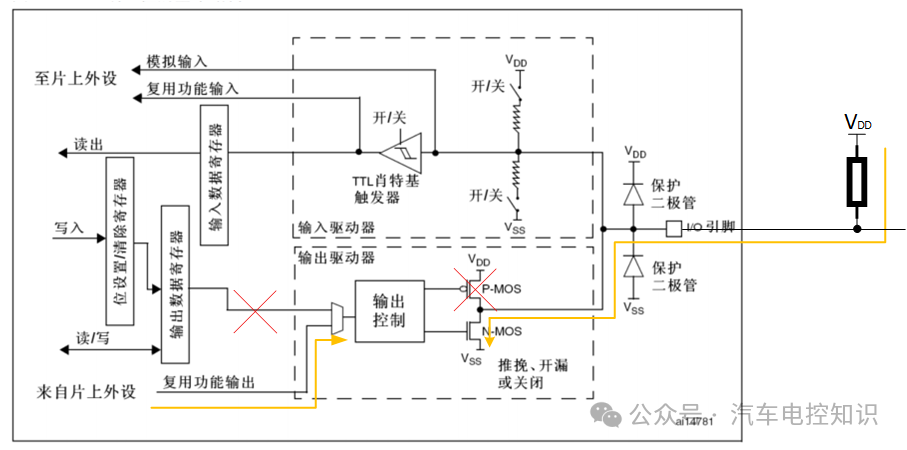

2.3 推挽复用功能输出模式

其输出原理与普通推挽输出完全相同,区别在于控制信号源。普通推挽输出的信号来自CPU写入的“输出数据寄存器”,而推挽复用功能输出的信号则直接来自芯片内部的某个片上外设。

为了提高引脚利用率,现代MCU的引脚通常是多功能的(复用)。一个引脚除了可作为通用GPIO,还可以被配置为UART、SPI、定时器PWM等特定外设的功能引脚。当配置为此模式时,该引脚的电平将由对应的外设硬件自动控制,无需CPU频繁干预。这种模式适用于需要高速、稳定输出的数字通信场景,如UART_TX、SPI_MOSI、定时器PWM输出等。

2.4 开漏复用功能输出模式

同理,开漏复用功能输出的原理与普通开漏输出一致,其控制信号同样来自片上外设,而非输出数据寄存器。

这种模式主要用于那些协议本身要求或适合使用开漏输出的外设,最常见的例子就是I2C总线(SDA和SCL线),它利用开漏输出配合上拉电阻来实现“线与”功能和多主设备仲裁。在复杂的网络/系统通信中,这种硬件级的支持简化了软件设计并提高了可靠性。

3. 总结

综上所述,以STM32为代表的现代微控制器其GPIO通常支持上述八种工作模式:

- 输入类(4种):浮空输入、上拉输入、下拉输入、模拟输入。

- 输出类(4种):开漏输出、推挽输出、开漏复用输出、推挽复用输出。

在实际开发中,我们需要根据外设的特性和电路设计,通过配置相应的寄存器来灵活选择正确的模式。例如,读取按键用上拉/下拉输入,驱动LED用推挽输出,ADC采集用模拟输入,I2C通信用开漏复用输出。正确理解并应用这些模式,是进行稳定可靠的嵌入式硬件和软件设计的基础。希望这篇详解能帮助你在云栈社区的嵌入式学习道路上更进一步。