半导体制造已进入“晶圆代工2.0”时代,制造、封装与测试的深度整合成为新的竞争焦点。在这种背景下,2.5D封装正迅速成为支撑AI芯片高性能需求的核心技术之一。

近期的产业动向印证了这一趋势。SK海力士计划投资38.7亿美元在美国建设一条2.5D封装量产线,预计2028年下半年正式投入运营。与此同时,台积电也在对现有的8英寸和12英寸晶圆厂进行重大升级改造,将主要生产90纳米及以上制程的芯片工厂,重点升级为安装支持CoWoS和CoPoS等先进封装技术的生产线。

这些密集的资本投入,标志着先进封装已从制造配角跃升为半导体竞争的核心赛道。

2.5D封装,有多重要?

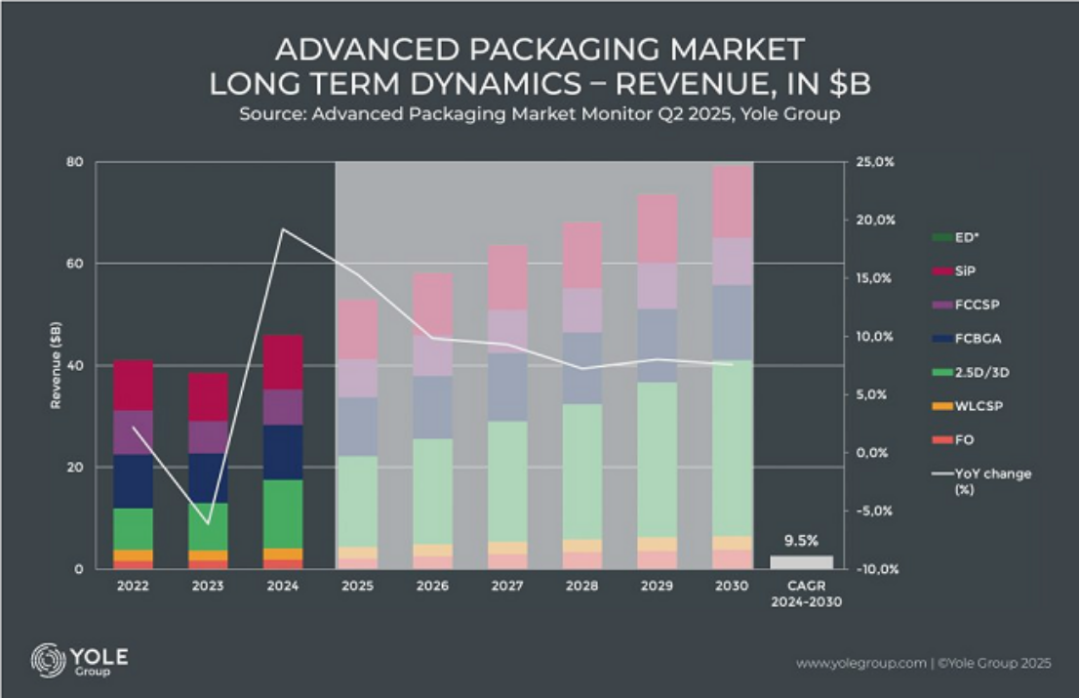

随着人工智能技术的快速发展,先进封装的重要性已超越单纯的制程工艺,成为半导体行业最热门的领域。Yole集团的数据显示,全球先进封装市场规模预计到2030年将达到约800亿美元,并以9.4%的年复合增长率持续增长。

技术的演变并非一蹴而就。从1950年代的点对点封装,到1970年代的周边穿孔封装,再到2010年后的2.5D与3D晶圆级封装,互连密度、I/O带宽和集成复杂度在持续提升。

那么,究竟什么是2.5D封装?

简单来说,它是一种通过硅中介层(Silicon Interposer)或嵌入式桥接技术(如英特尔的EMIB)将多个芯片水平连接起来的技术。与传统的2D封装相比,它允许在单一封装内集成更多的功能单元,例如CPU、GPU、高带宽内存(HBM)和I/O模块。而与复杂的3D堆叠相比,它又避免了过高的制造难度和热管理挑战。这种“折中”的状态,恰恰为对带宽和延迟极度敏感的AI芯片提供了完美的平衡。

AI芯片的一个显著特点是需要高带宽和低延迟的芯片间通信。例如,在训练深度学习模型时,GPU需要与HBM快速交换海量数据,而传统的封装技术往往受限于互连带宽和功耗。2.5D封装通过在芯片间引入高密度互连通道,显著提升了数据传输效率,同时保持了相对可控的制造复杂度。这使得它特别适合AI加速器和数据中心处理器等高性能应用场景。

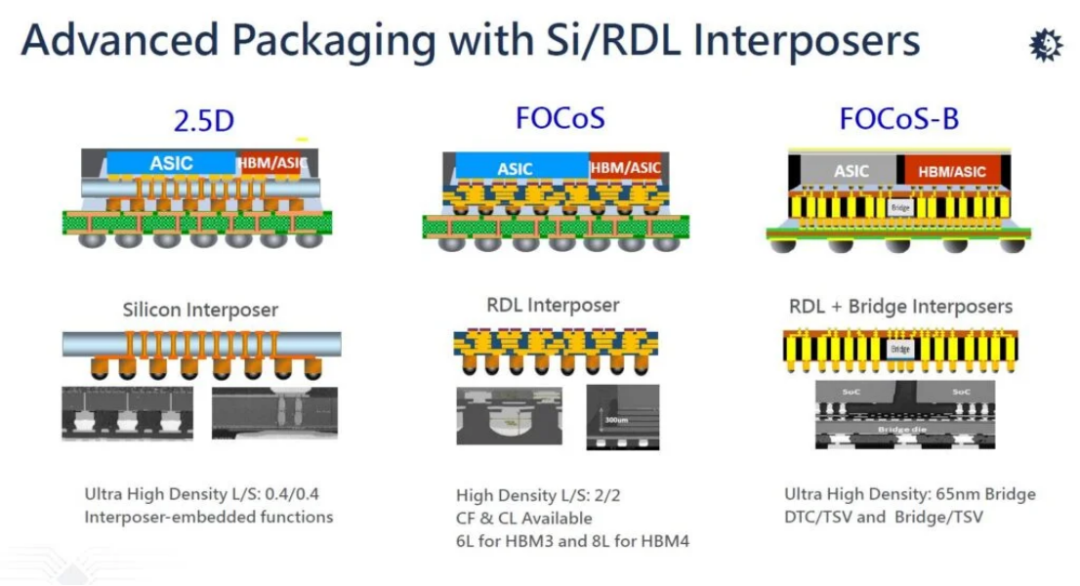

目前,用于整合AI Chiplet(例如GPU以及存储器)的主要先进封装技术有两种。一种是硅中介层方案,如台积电的CoWoS,先将芯片通过Chip on Wafer(CoW)工艺连接至硅晶圆,再与基板整合;另一种是RDL中介层方案,如FOCoS(Fan Out Chip-on-Substrate),将芯片置于RDL介面上进行整合。

若RDL Interposer上内埋有桥接结构,则称为FOCoS-Bridge或FO-Bridge封装。例如AMD的MI250加速器,就是将GPU跟HBM整合在RDL Interposer上面,利用内埋的桥接结构提供更精细的线路来连接GPU跟HBM。

台积电的CoWoS严格来说也属于2.5D先进封装技术,它由CoW和oS组合而来:先将芯片通过Chip on Wafer(CoW)的封装制程连接至硅晶圆,再把CoW芯片与基板(Substrate)连接,整合成CoWoS。英特尔在2.5D上则拥有多个方案:EMIB 2.5D、Foveros-S 2.5D、Foveros-B 2.5D。

当前,HBM是使用2.5D封装的典型代表,诸如AMD、NVIDIA等企业已推出多款基于2.5D硅中介层的产品。

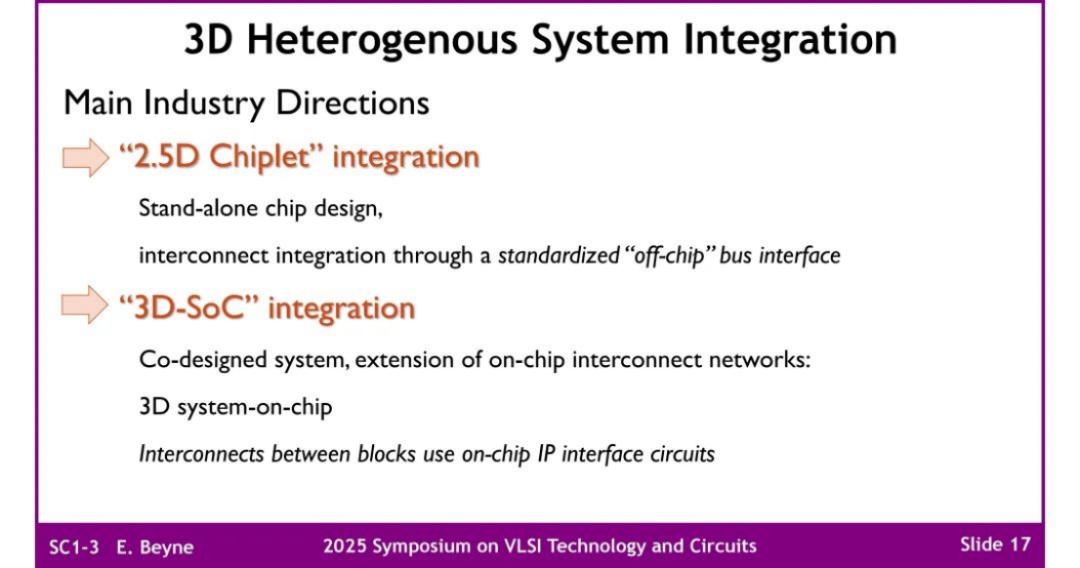

展望未来,行业的发展路径正在逐渐清晰。IMEC认为,互连层级与系统分区是3D集成的核心逻辑。未来主要有两大发展方向:2.5D芯粒集成通过标准化总线接口实现独立芯片互连;3D-SoC则通过协同设计,将片上互连网络延伸至3D空间,从而大幅提升互连密度。

2.5D封装的关键在于中介层。 台积电CoWoS技术的硅中介层尺寸从2016年的约1287mm²演进至当前的约2831 mm²,可支持8个HBM3堆叠,并计划在2026年扩展至约4719mm²以兼容12个HBM4堆叠。

随着HBM接口带宽的不断提升,中介层的复杂度也在增加。目前典型中介层最多有四层金属,但已有产品采用多达十层的设计。联电先进封装总监指出:“在HBM4之后,就需要八到九层金属层。”层数的增加会推高成本,同时带来机械强度与翘曲控制的挑战。

当前绝大多数中介层为无源结构,仅提供互连功能。但由于硅中介层由半导体材料制成,未来有望集成晶体管,发展为有源中介层,用于电源管理、I/O或光器件集成,尤其适用于AI和高性能计算场景。

为了避免高昂的成本,业内主要有两种探索方向:一种方法是寻找比硅更便宜的材料,例如有机中介层,其在材料和制造成本方面都更具优势;另一种方式是,使用硅桥接器代替完整的硅中介层,每个桥接器的尺寸都小得多,从而可以提高良率并降低成本。

在国内,相关企业也在积极布局。盛合晶微是国内最早实现12英寸Bumping量产的企业之一,具备2.5D/3D IC超高密度微凸块的大规模量产能力。在基于TSV硅中介层的2.5D集成方面,其技术能力与全球领先企业不存在代差。

长电科技推出的XDFOI高密度扇出型封装平台,具备2.5D封装能力,可支持4nm节点Chiplet产品封装。通富微电则在2.5D/3D封装领域取得突破,其TSV工艺成本较海外低40%。华天科技也布局了2.5D封装技术,其12英寸晶圆级TSV产线良率已达到85%。

3D封装是下一步

2.5D封装可视为一个重要的过渡阶段,而3D封装才是下一阶段的终极目标,其最大的优势在于将芯片间的互连距离大大缩短,从而实现更高的带宽和能效。3D封装通过垂直堆叠实现芯片立体集成,其核心技术包括硅通孔(TSV) 和混合键合(Hybrid Bonding)。

TSV技术通过贯穿硅片的垂直导电通道连接堆叠芯片,例如三星的X-Cube技术就基于TSV实现了SRAM与逻辑芯片的3D堆叠,从而缩短信号路径以提升速度和能效。混合键合技术(如台积电SoIC的Cu-Cu键合)则通过金属直接键合消除微凸点间隙,实现10μm以下的互连间距,其带宽密度可达1TB/s/mm²,较传统微凸点技术提升10倍。

为了支持这一产业转型,上游设备商也在积极行动。ASML已经向客户交付了第一台专为先进封装应用开发的光刻机“TWINSCAN XT:260”,可用于3D芯片、Chiplets芯粒的制造与封装。该设备采用i线光刻技术,生产速度高达每小时270块晶圆,是现有先进封装光刻机的4倍。

此外,泛林集团也在去年9月宣布,已开发出用于先进半导体封装的新型沉积设备“Vector Teos 3D”。该设备面向AI和HPC芯片制造,旨在解决异质集成和3D垂直堆叠过程中出现的各类技术难题。这些底层设备的创新,为整个先进封装产业的持续演进提供了坚实的支撑。

结语

除了自建先进封装产能的SK海力士,越来越多的企业正抓住市场机遇,加快扩产步伐。

日月光在2025年9月宣布新建K18B厂房,以应对未来先进封装产能的扩充需求。全球第二大OSAT企业Amkor(安靠)也宣布将其在美国亚利桑那州皮奥里亚市的先进封测设施占地面积几乎翻倍,以扩大产能。

国内封装大厂同样动作频频。长电科技保持全年85亿元资本支出计划,重点投向先进封装的技术突破;华天科技则宣布其2.5D/3D封装产线已完成通线。

全球先进封装产能的密集落地与扩张,清晰地印证了这一领域的战略重要性。在AI浪潮的驱动下,封装技术已不再是幕后环节,而是直接决定芯片性能上限和市场竞争力的关键。这场围绕互连密度、带宽与集成度的竞赛,核心在于谁能更快地实现技术突破并规模化落地。对于整个半导体产业而言,深入理解从2.5D到3D的封装技术演进,不仅是把握技术脉络的需要,更是洞察未来市场格局的关键。想了解更多关于计算机系统架构和底层技术原理的深度讨论,欢迎访问云栈社区的相关板块进行交流。