本文分享一种通过分析CAN波形的幅度和脉宽信息来精确定位错误帧来源的实用方法。掌握这种方法,能帮助工程师高效诊断复杂的网络通信问题。

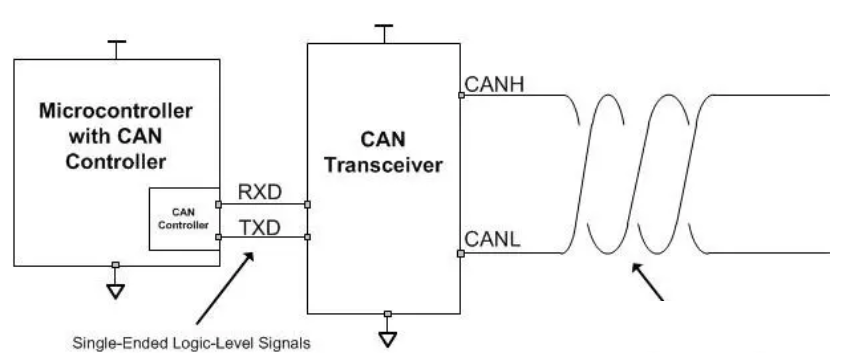

我们先从最基础的部分讲起。一个典型CAN节点的电路结构如下图所示。MCU内置了CAN控制器,负责将MCU的数据封装为符合CAN协议规范的帧格式,同时也负责帧校验和错误帧的处理。控制器封装好的逻辑报文通过TX、RX引脚送到CAN收发器,由它将逻辑电平信号转换为真正的总线差分波形。

01 CAN物理层

那么,CAN收发器具体做了什么工作呢?

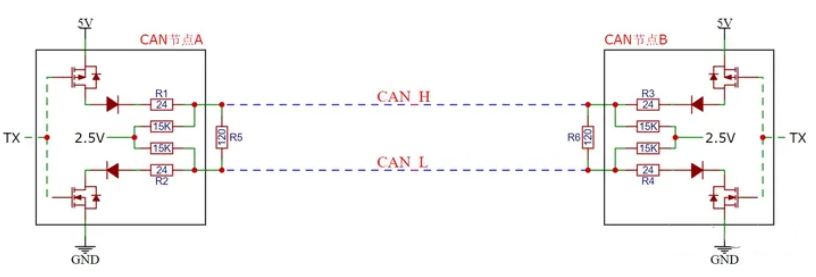

一个典型的双节点CAN网络的物理层等效电路如上图所示,两颗120Ω终端电阻并联后,总线呈现约60Ω的电阻。图中黑框内是节点A和B的CAN收发器(Transceiver),它仅负责电平转换。当总线静默时,收发器内部的2.5V电源通过15KΩ电阻将CAN-H和CAN-L都上拉到2.5V,总线这个状态称之为隐性。

当节点A想要驱动总线时(TX=0),它会同时导通内部的上下两个MOS管。此时整个网络的电流流向为:节点A的5V电源→二极管→24Ω电阻→两颗并联的终端电阻→另一24Ω电阻→二极管→回到节点A的地。总线这个状态称之为显性。CAN总线上的电压实际上就是终端电阻的分压。

从节点B的视角来看,CAN-H的电位变为约3.5V,CAN-L变为约1.5V,从而在总线上拉出了H-L ≈ 2V的差分电压。这个电压大于0.7V的判断阈值,因此节点B就认为收到了一个显性(RX=0)。建议大家动手计算一下分压值以加深理解,这在后续分析中很有用。

反直觉知识点①:总线无人驱动时(即各节点都处于隐性状态),CAN标准定义此时的TX/RX逻辑电平为1;当总线有节点驱动显性(即主动拉开差分电压)时,对应的TX/RX端逻辑电平为0。这种“反逻辑”类似于I2C等开漏(OC)门的驱动逻辑。这么做可能有两个原因:一是对地逻辑的抗干扰能力通常更强,NPN型器件载流能力强且回流路径短;二是为了数学上的严谨性:1x1x1x1...1x0 = 0,即任意一个节点驱动显性0,总线就是显性0;只有所有节点都输出隐性1,总线才是隐性1。但这种设计带来的一个隐患是:电路设计时需要特别注意上下电时序,避免出现MCU已下电(导致TX引脚被内部下拉至低电平)但CAN收发器仍供电的情况。如果难以避免,可以尝试使用单3.3V供电的CAN收发器(如MAX3051),其逻辑电平和驱动电平共用一路3.3V电源,能有效规避电源时序问题。

反直觉知识点②:理论上,即使CAN_L对地短路,或CAN_H短路到12V,由于60Ω终端电阻的存在,总线在隐性时CAN-H与CAN-L之间电压基本仍重合,显性时也能正常拉开压差,可以维持基本通信,但丢包率可能会显著上升。大家可以通过计算总线电压来理解,使用示波器也很容易诊断此类问题。另外,如果你观察到CAN通信的差分电压波形不是以2.5V为中心对称的,也有可能是多条CAN线的交叉错接所致,例如CAN1_L错误地接到了CAN2_L上。

反直觉知识点③:在一个CAN网络中,配置1到4颗120Ω终端电阻通常都能工作。电阻过少会导致离终端电阻最远的节点抗扰度变差;电阻过多则可能导致显性差分电压无法达到接收阈值。

反直觉知识点④:除了线路最远端,任何稍长的CAN分支都可以考虑串接1K~4.7KΩ的支线电阻,通过跑一点电流来改善该分支节点的抗扰度。只要分支长度不是特别长,大致在1Mbps速率以内的总线中,终端电阻主要作用是提供电流通路以增强抗扰,与严格的阻抗匹配或反射抑制关系不大,对双绞线的要求也并非极其严格。

02 CAN链路层

接下来看链路层,也就是CAN控制器的作用。

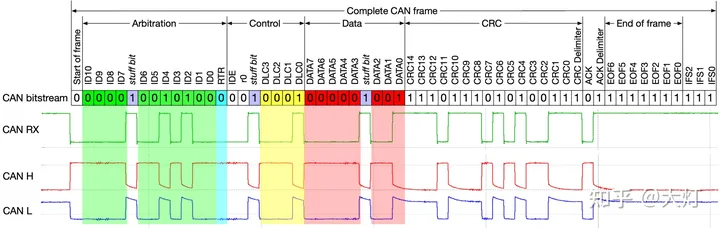

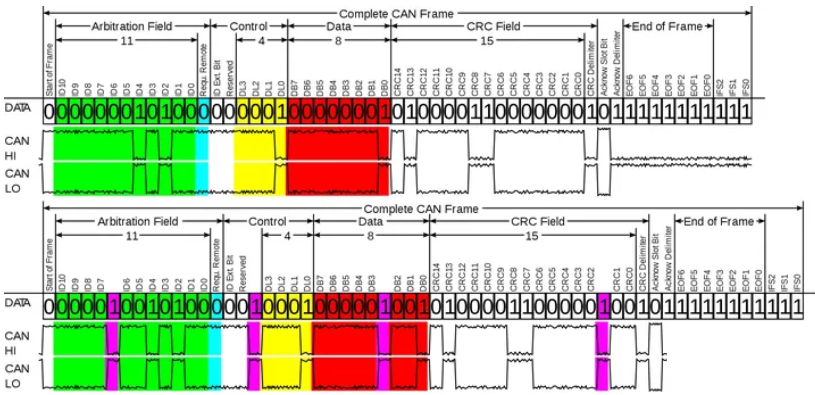

回顾完物理层,我们来看CAN帧的标准格式。当发送节点的MCU将TX由1变为0时,CAN收发器将CAN-H拉高、CAN-L拉低;接收节点检测到H-L>0.7V的压差后,其CAN收发器的RX输出由1变为0。下图展示了一个节点接收CAN波形后解码出的RX逻辑信号。

一帧CAN报文中包含几个关键字段:仲裁段、控制段、数据段、CRC段、ACK段。

仲裁段包含了CAN报文ID的大部分比特。称之为“仲裁”,是因为这一段实际具备优先级仲裁功能。假设A、B两个节点在同一时刻抢占总线发送报文,节点A要发送二进制ID为001的报文,B要发送010。当A、B节点都在发送第一位(显性0)时,总线同时被两个节点驱动为显性,双方回读总线也都是显性,此时彼此还未意识到对方的存在。当节点A发送第二位的0,节点B发送第二位的1时,总线只有节点A在驱动显性0,节点B不驱动却检测到总线被他人驱动为显性。此时,节点B会认为CAN线上有比自己这帧010优先级更高的数据正在传输,于是节点B会主动停止发送,让节点A独占总线完成发送。之后,节点B再携带这帧数据重新参与总线仲裁。

反直觉知识点①:CAN是一个对等网络,没有主从关系,所有报文均为广播,节点本身也没有固定优先级,只有报文ID的优先级。可以理解为:CAN节点是“由事件驱动的”。例如刹车制动器,它能发送高优先级的“刹车被踩下”报文,也会发送低优先级的“刹车油位正常”报文。这些报文根据ID的大小在总线上自由竞争优先级,而非刹车制动器这个节点拥有绝对高的话语权。这个特性要求设计人员必须提前规划好所有报文的优先级和发送周期(即制定“通信矩阵”),才能保证整个CAN网络有序运行。如果你的CAN网络中有大量功能相同的节点,且每个节点只发送一帧报文,那么ID数值大(优先级低)的节点在总线繁忙或受干扰需重发时,很可能长期“插不上话”。可以尝试将时间戳融合到ID中,确保各节点的最新数据拥有最高优先级,旧数据则自然会在仲裁中被淘汰。

反直觉知识点②:在A、B节点同时驱动第一个显性0时,总线被两个节点共同驱动,其电压会显著高于单个节点驱动时的2V。在示波器上,你可以在仲裁段的起始部分观察到一个明显的电平“凸台”。随后,当节点A成功抢占总线后,电压会回归正常的2V水平。

反直觉知识点③:各节点间的时钟同步是通过将每个比特位划分为16~20份数字切片来实现的,这个划分的份数(即采样点数)不宜设置得过多或过少。

控制段包含几个重要的控制位。这里以常用位举例:IDE位指示是否使用扩展ID。若IDE位为隐性1,则会在其后续上18位扩展ID,形成共11+18=29位的标识符。例如,0x9E是一个11位标准ID,而0x0151则是一个29位扩展ID。R0位在CAN协议中是保留位,在CAN-FD协议中被用作FD帧格式的标志位FDF。当这一位为隐性1时,后续报文将按照FD帧格式进行解码。DLC指示了后续数据段的长度,例如1000表示后面有8个字节的数据。需要注意的是,CAN-FD协议仅在数据段切换为高速率(如2Mbps/8Mbps),报文前后的其他段(仲裁、控制、CRC等)仍保持基础速率(如500kbps)不变。

反直觉知识点①:CAN与CAN-FD除了数据段波特率不同,帧格式也有区别,CAN-FD多了BRS、ESI等控制位。例如,FDF(也叫EDL)位用于指示是否按FD帧格式解码,BRS位用于指示是否需要切换至高波特率。这意味着,一个FD帧也可以全程使用500kbps的基础速率,不进行速率切换。

反直觉知识点②:在标准CAN(ISO11898-1)中,要求接收方不解读R0位的显隐性,因此传统的CAN控制器无法识别FD帧。标准CAN网络中一旦出现FD帧,会因为多出的BRS、ESI等控制位而被认定为格式错误。同样地,在CAN 2.0时代,R0/FDF位无实际意义,导致一些设备错误地将发送出去的CAN帧的R0位置为隐性1。这类设备在纯CAN网络中工作正常,但一旦接入CAN-FD网络,其报文会被解读为FD帧,进而因为缺少必要的控制位而被判定为格式错误。所以,CAN-FD并非真正意义上的向下兼容CAN,因为旧式CAN设备不具备识别R0/FDF位的能力,一旦进入FD网络就可能持续引发通信中断。

反直觉知识点③:关于DLC指示的长度。在标准CAN中,DLC可以是0000到1000之间的二进制值,可直接按8421码换算为0~8字节的数据长度。而在CAN-FD中,1001到1111之间的值被解读为离散的数据长度:12, 16, 20, 24, 32, 48, 64字节。

CRC段对从帧头开始到数据段结束的所有数据进行校验,CAN协议使用了较为特殊的CRC15多项式。有兴趣的可以手动计算验证。CAN-FD则根据数据长度不同,采用了CRC17或CRC21,此处不展开。

ACK段由成功接收到该帧的CAN节点回复确认(Acknowledge)。注意,发送节点在ACK位一定发送的是隐性1,而由接收节点回应一个显性0,双方无缝衔接,才在总线上呈现出一个完整的比特位。

反直觉知识点①:总线上任何节点,只要认为当前帧结构正确,都会在ACK位回复显性0,无论它是否需要这帧报文的数据。为什么不需要的节点也要回复ACK?因为如果等MCU软件处理后再决定是否回复,会造成这一位的延迟,从而扰乱严格的总线时序。因此,协议设计为仅由硬件保障链路层格式正确即可,纯数字逻辑实现可实现无延迟响应。

反直觉知识点②:发送节点如果发现自己发出的这一帧没有收到任何ACK回应,也会认为总线出错。在连续重发16次后,该节点会进入“被动错误(Passive error)”状态。

03 真实CAN波形

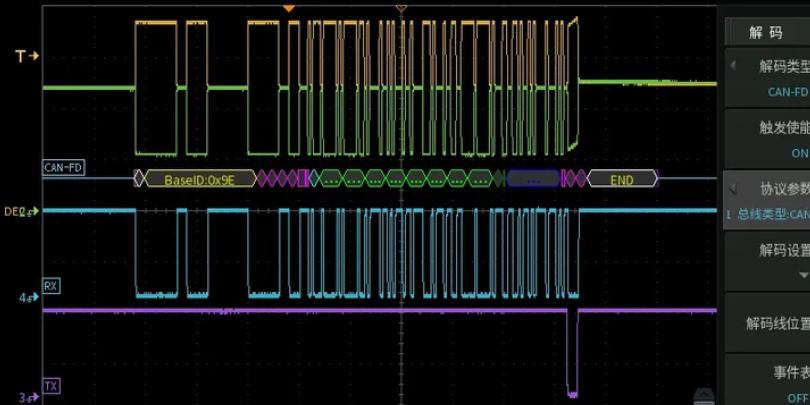

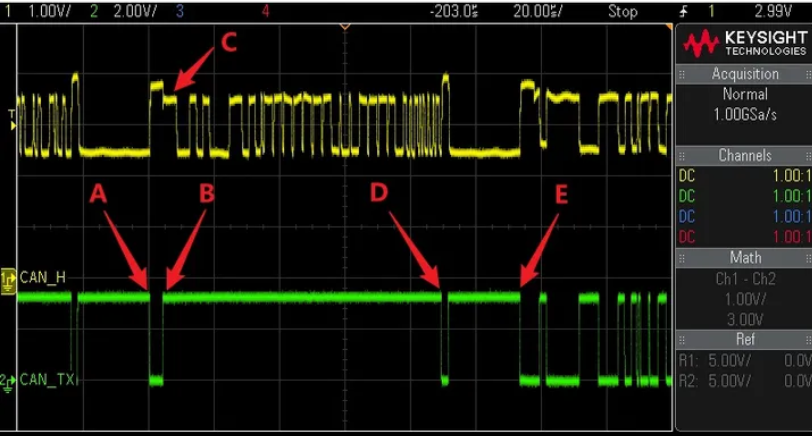

来看一个两节点通信的实际案例:若节点A发送ID为0x9E的报文到总线,节点B收到的总线波形及其逻辑侧波形如下:

图中,黄线为CAN-H,绿线为CAN-L,蓝线为节点B的逻辑侧RX信号,紫线为节点B的逻辑侧TX信号。可以看到,作为接收方的节点B,当总线被拉出显性差分电压时,其收发器将RX拉低至0并送给MCU。当节点B需要回应ACK时,MCU将TX拉低至0,其CAN收发器随即在总线上拉出一个略有歪斜的显性位(歪斜通常由测量点寄生电感导致)。而RX在ACK位置出现的0,实际上是收发器在TX=0驱动总线显性之后,自身回读到的结果。

再看一个更接近真实车载环境的波形,该CAN网络上节点数大于4个:

图中,黄色是CAN_H信号(高电平代表显性0),绿色是我们挂接示波器的这个节点的逻辑侧TX信号(低电平代表显性0)。箭头A~D标识了一帧完整的CAN报文。在箭头A到B的过程中,我们挂示波器的这个节点正与另一个节点进行优先级仲裁。根据之前讲到的物理层分压原理,两个节点同时驱动总线时,电压会明显高出一截。在箭头C标识的这个比特位,我们的节点本想发送隐性1,但却发现总线是显性0,这说明有另一个节点正在发送优先级更高的报文。于是,我们的节点会主动退出发送,转变为接收节点,并在箭头D点(校验成功后)回应ACK。等待该报文结束后,我们的节点再次参与总线仲裁,并成功抢占总线开始发送,如箭头E所示。

注意观察波形幅度:在箭头A~B之间,差分电压略高于2V,这是正常现象,表明有两个节点在同时驱动总线显性。但从纯数字逻辑看,因为H-L>0.7V,CAN控制器均视为显性0,在A~B之间还无法感知对方存在,直到箭头C点之后才“察觉”到竞争。而在箭头D点的ACK位,因为除了原始发送节点之外的所有节点都在同时驱动ACK,所以总线电压比A~B之间双节点驱动时还要高。

04 错误帧

终于讲到错误帧了。这里有一个关键概念需要明确:错误帧并不是由某个节点“发出”的,而是由某个接收节点认为总线传输出现错误时,主动驱动总线以打断发送方,从而在总线上呈现出的一个特殊帧结构。也就是说,一个错误帧的形成,一定涉及一个发送节点和至少一个认为其出错的接收节点。

05 位填充规则

位填充规则是CAN协议可靠性的核心机制,简单概括为四个字:逢五补一。

当发送节点需要发送连续5个显性0时,它会主动插入一个无意义的隐性1;当需要发送连续5个隐性1时,则会插入一个无意义的显性0,如上图中紫色标出的比特位。如果发送节点漏插了这个填充位,或者填充位在传输中被干扰成了相反电平,接收节点就会判定发生“填充错误”,并向总线输出“主动错误标志”——即连续6个显性0,以此故意破坏当前帧的格式。发送节点感知到总线错误后,便会停止发送该报文的剩余部分。这个设计非常巧妙:连续6个显性0本身就违反了“逢五补一”的规则,被直接用作错误标志反馈给发送节点。

举例来说:

- 假如原始数据是

0x00(二进制0000 0000),发送节点在发出前5个0(0000 0)后,会自动插入一个1,再发送后续的000,最终在总线上变为0000 01000,共9比特。接收节点同样会在第5个0之后期待一个无效的1,并在解码时将其剔除。

- 假如原始数据是

0000 0100,其第6位自带一个1。发送节点在处理前5个0(00000)时,依然会先插入一个1,再发送后续的100,总线上成为0000 01100,长度也是9比特。

06 回读确认与错误帧形成

发送节点在发送每一个0或1时,都会回读总线状态以确认是否与自己的发送相符(例如在仲裁段抢优先级失败后,会等待下一帧再尝试发送)。如果发送进行到数据段,理论上此时总线应只有自己在发送,但若在发送过程中突然发现回读的0/1与自己发送的不同(例如受到干扰),发送节点就会立即输出“主动错误标志”——连续6比特显性0,主动抛弃后续报文,并通知接收节点此帧有误。

此时,接收节点在收到第6个连续的显性0时,同样会因为该序列违反“逢五补一”的位填充规则,而向总线输出自己的“主动错误标志”。 因此,在总线上我们会看到连续12比特的显性0,前6个来自发送节点,后6个来自接收节点。

正常情况下,总线上连续显性位的长度不应超过5比特(在500kbps下为10us)。因此,使用示波器设置脉宽大于11us的触发模式,可以很容易地定位到错误帧出现的位置,不一定非要依赖带协议解码功能的示波器。

07 升维打击:结合幅度与电流分析

CAN总线波形的幅度和节点电流信息可以为我们提供更多维度的诊断依据,实现“升维打击”。

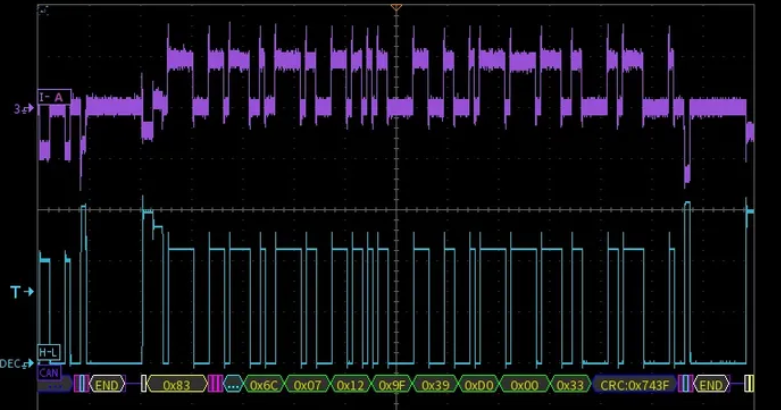

我们先来看一帧正常报文(假设来自节点A,其内部包含终端电阻)。下图中,蓝线为H-L的差分电压,紫线是节点A CAN-H引脚上的电流(规定输出为正,输入为负)。

先看蓝色的总线电压波形。从0x83到END之间是一帧正常波形。注意观察帧头部分有多个电压台阶,帧尾ACK位的电压也特别高,这都属于正常现象。可以理解为:当多个节点同时驱动总线时,60Ω终端电阻上的分压会高于单个节点驱动时的2V。从这些台阶的数量,我们可以推断网络上至少有5个节点。为什么?

观察报文中部的数据区幅度,这肯定是只有一个节点(节点A)成功抢占总线后的波形。往前看,帧头处有两个明显的台阶:第一个高台阶可以认为是A、B、C三个节点同时抢占总线导致的;随后节点C因优先级仲裁失败退出,剩余A、B两个节点继续抢占,形成第二个稍低的台阶;最后节点A成功胜出,开始发送中间的数据段。帧尾的ACK位电压比三节点驱动时的第一个比特位还要高,说明至少有4个节点在同时驱动ACK。加上发送节点A本身,因此网络至少有5个节点。

再看紫色的电流波形。已知节点A自身有终端电阻,网络另一端还有另一颗终端电阻。波形中部的数据区显然是节点A在驱动总线,差分电流流经网络对端的终端电阻形成回路,因此在节点A的引脚上观测到了输出的正向电流。在前一个电压台阶(双节点驱动)的位置,电流约为0,这是因为A、B两个带终端电阻的节点在同时驱动,总线电压被拉开,但电流在节点A处基本平衡。再往前一个台阶(三节点驱动),节点C的电流流入了节点A和B的终端电阻,因此在节点A的引脚上测到了输入的负向电流。最后在帧尾ACK位,至少有4个节点同时驱动,流入节点A和B终端电阻的负向电流变得更大。

08 错误帧实战分析

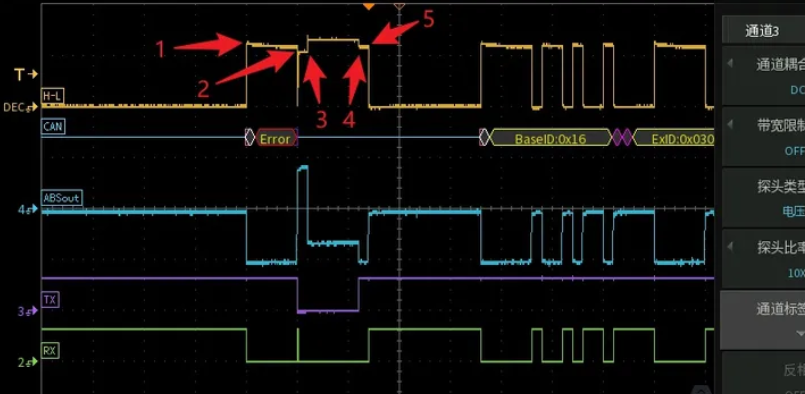

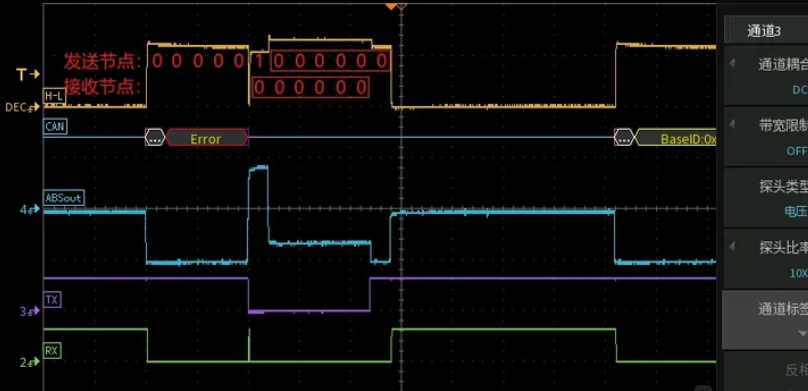

这是一个两节点网络案例:一个节点发送,另一个节点接收,双方都有终端电阻。发送节点使用TJA1042收发器,接收节点使用单3.3V的MAX3051收发器。错误在帧头部分就发生了,这类错误通常源于节点间时钟偏差过大或采样点设置不合理。

我们将示波器的差分探头和电流探头接在接收端。下图黄色为H-L差分电压,蓝色为接收节点的输出电流,RX是收发器转换出的逻辑波形,TX是接收节点的发送逻辑。

已知总线速率为500kbps,每个比特位宽2us。注意上图中紫色TX线在箭头2~4之间出现了连续2us * 6 = 12us的显性0,这说明我们挂示波器的这个接收节点在此刻向外输出了一个“主动错误标志”。那么,必然是接收节点在此之前就认为总线出现了错误。

向前查看,箭头1~2之间,总线差分电压和RX逻辑侧都只有约10us(即5个比特位)的显性0,且帧起始前都是长的隐性1。这能有什么错误?一种可能是遇到了罕见的“过载帧”;另一种可能是接收节点错误地将对方发送的正确报文误判为错误帧——它将这10us的显性正确识别为5个比特,但由于自身时钟问题,可能将其“数”成了6个比特。采样点设置不当且硬同步(帧头同步)机制不完善的国产MCU更容易出现此类帧头误报错。

不论原因如何,我们可以推演一下波形形成过程:在箭头2~3之间,发送节点本打算发送一个隐性位,但此时接收节点已开始输出“主动错误标志”,将总线强行拉为显性。发送节点回读发现自己想发隐性但总线为显性,从而触发错误。但由于总线在此之前已出现连续6个显性(违反了位填充规则),发送节点也会在箭头3~5之间输出自己的“主动错误标志”。这就形成了黄色总线波形上那个独特的7比特“凸”字形结构。中间的凸台对应总线被两个节点同时驱动的时刻,因此电压升高一个台阶。

另一个关键细节:凸台的左肩和右肩高度不一致。左肩是接收节点MAX3051驱动的电平,由于其驱动能力弱于发送节点的TJA1042,因此总线电平略低。这个特性可以用来区分总线上不同型号或驱动的设备。

蓝色电流线显示:箭头1~2间的负向电流是发送节点驱动总线,电流流经接收节点内部终端电阻所致;箭头2~3间的正向电流是接收节点驱动主动错误第一个比特产生的;3~4凸台期间两个节点都在驱动显性,但电流仍为负,说明发送节点的驱动能力更强,网络整体电流仍由发送节点灌入接收节点;4~5间的负向电流是发送节点驱动、流经接收节点终端电阻的电流。

下图标出了两个节点的发送比特流,红框内为“主动错误标志”。

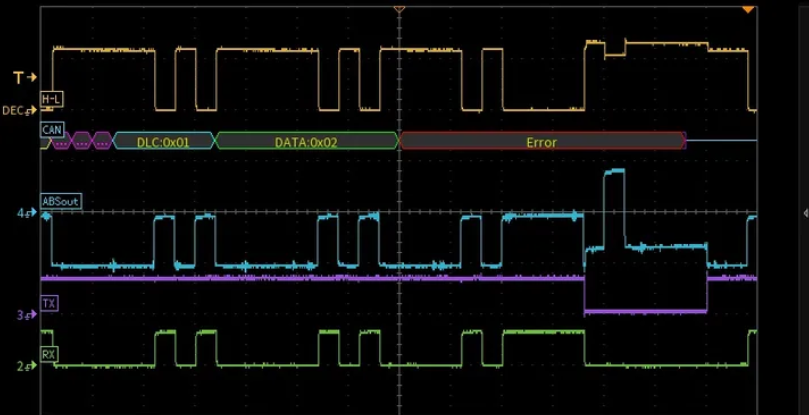

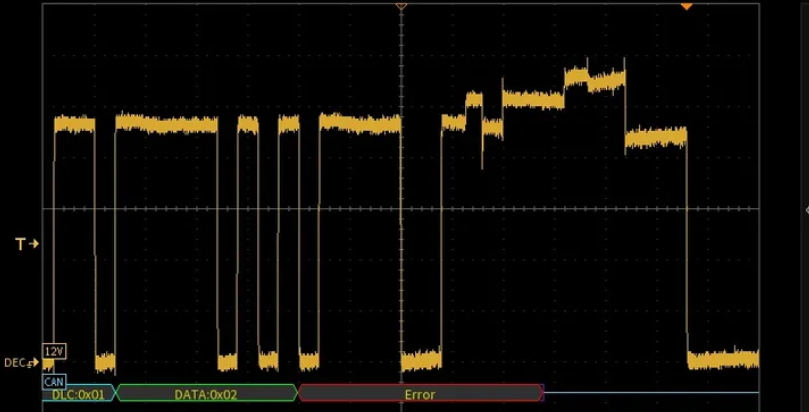

仍然是这个两节点网络和那款同步机制不佳的国产MCU,我们再看另一个错误帧:

这一帧的DLC=0x01,即只有1字节数据。数据区之后就是CRC区,而“主动错误标志”就发生在此区域。观察波形并未发现位填充错误,那么很可能我们挂示波器的这个接收节点认为发送节点的CRC校验值有误。但注意黄色波形在“主动错误标志”中间出现了一个“凹坑”,这意味着发送节点本意是想继续发送隐性位,并不认为自己有错,直到发现这一位被接收节点的“主动错误标志”覆盖为显性后,才感知到“位错误”,从而抛弃后续报文。

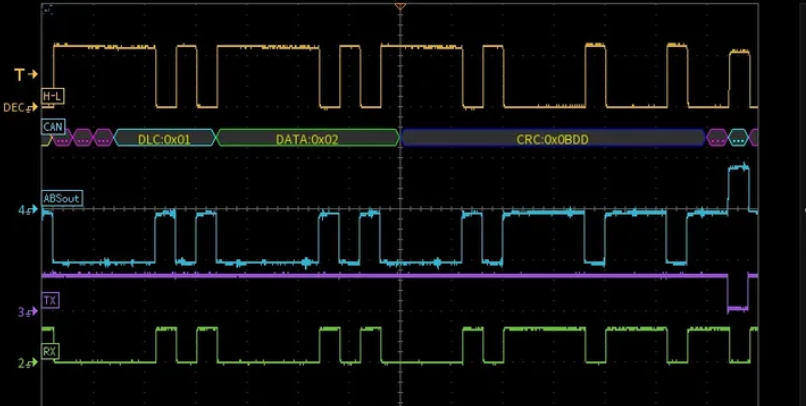

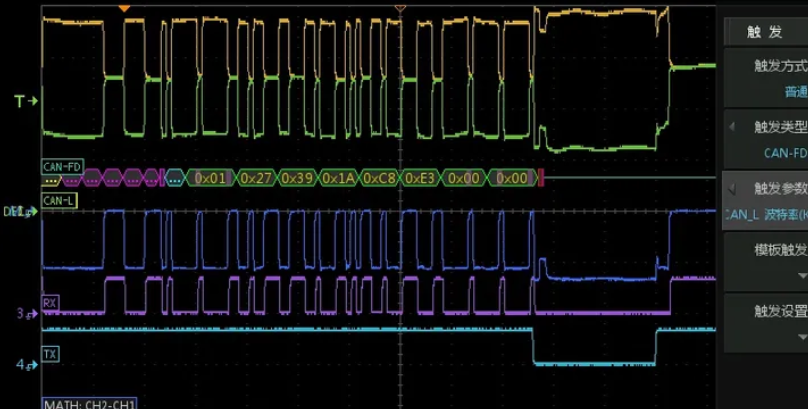

问题最终定位为:过小的采样点配合过大的再同步补偿宽度(SJW)导致时钟误差逐步累积,而这颗国产MCU的重新同步机制存在缺陷,将正常报文错读了一位,进而计算出错误的CRC。通过调整采样点和SJW宽度,显著减少了此类错误的发生频率,得到正常波形如下:

我们再尝试仅从差分波形来分析一个错误帧:

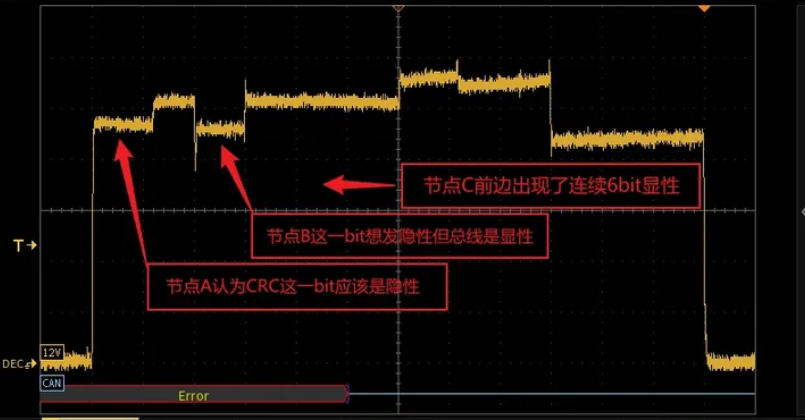

错误发生在CRC区域。放大细节,看看各节点的行为:

以每个电压台阶为起点,向前画出12us的方框(对应一个主动错误标志的长度),可以分离出每个节点输出的错误标志。分析可知:这是一帧由节点B发送的报文,节点A认为其CRC计算错误,节点C也“凑热闹”发出了错误标志,三者共同形成了这个长达12比特的“主动错误标志”波形。那么,节点A为何会认为CRC错误?大概率是因为它在接收数据段时就读错了一个比特位。波形看起来很好也会读错?是的,我们无法判断节点A所在物理位置的信号质量,可能其连接分支上没有终端电阻,导致振铃很大。我们只能基于协议逻辑推断节点A的行为。此外,采样点偏差确实会导致节点对噪声格外敏感。

09 CAN-FD错误排查

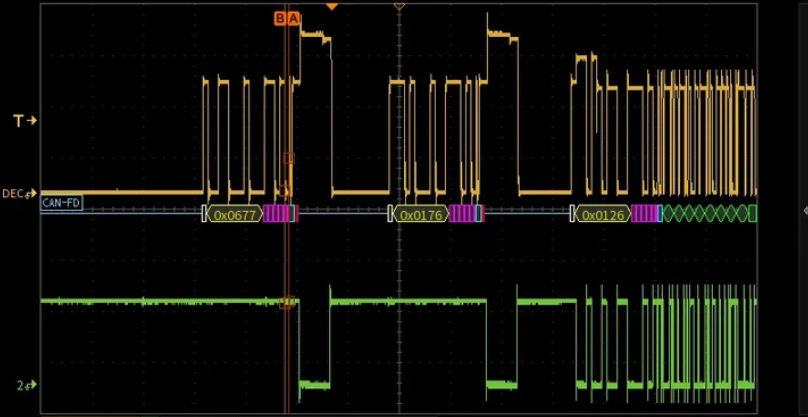

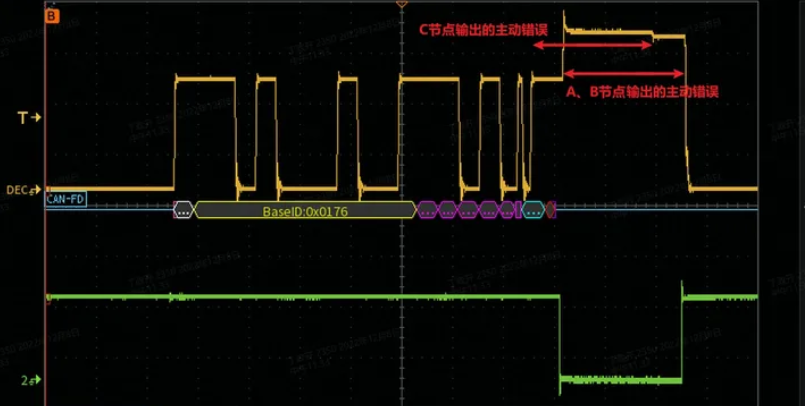

来看一个A、B、C三节点CAN-FD网络的错误案例,节点C发送,节点A、B接收。黄色为H-L差分电压,绿色为节点B的逻辑TX信号。0x0677和0x0176标识了两个错误帧的位置。FD数据区波特率设置为2Mbps。

放大0x0176帧的细节:

- 标尺A与B之间的时间长度约为0.8us,由一个2Mbps的FD比特位(0.5us)加上CAN-FD协议规定的发送延迟补偿(TDC,约300ns)组成。

- 之后出现了6个连续的高速率(2Mbps)显性位(

0.5us * 6 = 3000ns),电平高度与之前相同。这违反了FD速率下的“逢五补一”规则。

- 紧接着,出现了连续的

2us * 6 = 12us的显性位,这是标准速率的“主动错误标志”。

- 在标尺B线之后约12us的位置,可以观察到一个电压跌落的小台阶(见更下方的分解图)。

综合以上,可以推断:节点C所在位置可能干扰过大或分支线路过长,导致节点C自己回读下图框出的那个比特位失败,从而主动向总线输出“主动错误标志”(连续6比特,2Mbps下为3us,但错误标志本身以500kbps速率发送,故为12us)。其他设备(A、B)在接收到第6个高速率显性位(总计3us)时,也检测到了填充规则违反,于是同样向总线叠加500kbps的12us主动错误标志。随后,节点C的错误标志先结束,其他节点的错误标志稍晚结束,共同构成了完整的错误帧形态。

关键点:“逢五补一”规则是跟随当前波特率变化的,6个连续的高波特率显性或隐性位都会触发填充错误。但填充错误被触发后,节点输出的“主动错误标志”总是以500kbps的基准速率发送,固定为6比特(12us)长度。

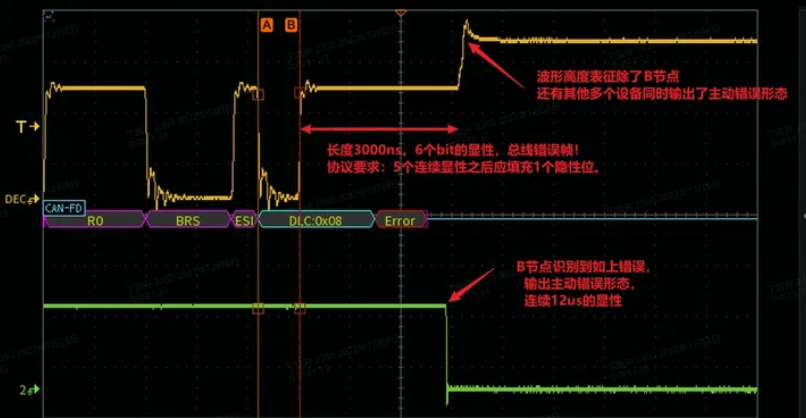

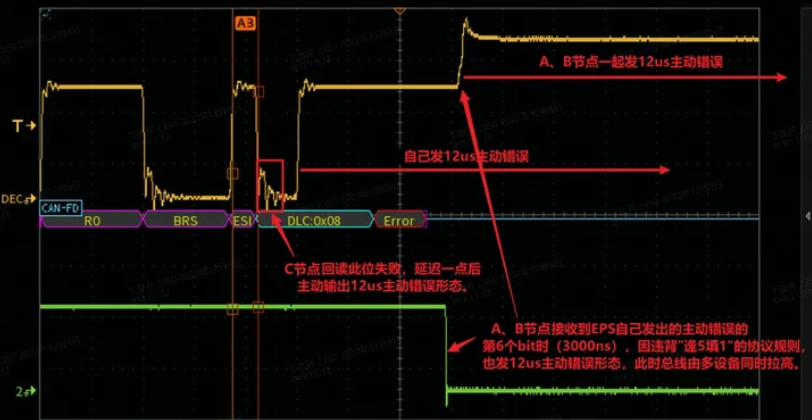

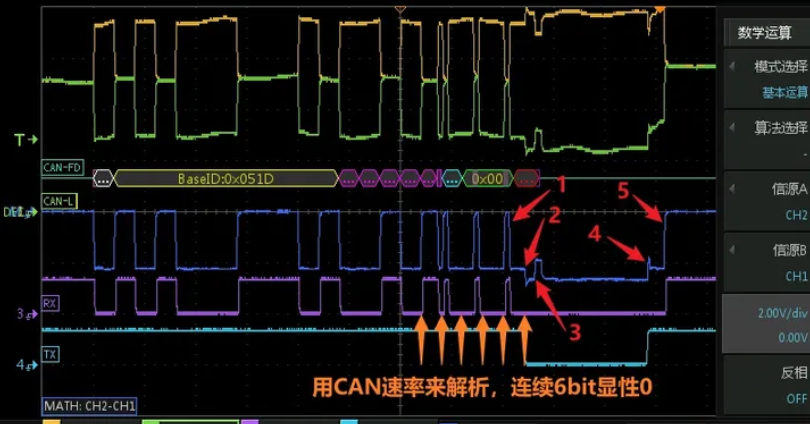

再来一个案例:由于节点B的采样点设置错误,导致它将节点A发送的CAN-FD报文误当作标准CAN报文来解析,从而引发错误。

下图黄色为CAN_H,绿色为CAN_L,蓝色为L-H反向差分电压(便于观察),紫线为节点B的逻辑RX,青线为节点B的逻辑TX。

注意看数据0x00前后的数据段,这一段是CAN-FD的2Mbps速率。节点B由于采样点设置错误,读错了BRS(波特率切换)标志位,仍然按照标准的500kbps(即每比特2us)去采样节点A发出的2Mbps速率数据。图中用黄色箭头标出了节点B对RX信号的采样点(间隔2us),可以看到这恰好对应了6个连续的显性0,违反了“逢五补一”规则。因此,接收节点B在箭头2~4之间发出“主动错误标志”,打断通信。在箭头2~3之间,发送节点A恰好也在发送显性位,因此尚未察觉异常。箭头3之后,节点A本想发送隐性位(波形出现“凹坑”),却回读到总线仍为显性,此时它判断发生“位错误”,也开始输出“主动错误标志”。箭头4处节点B释放总线,箭头5处节点A释放总线。

如果数据内容恰好能满足位填充规则,这类错误可能会在传输很多数据后才出现,但最晚也会被CRC校验拦截:

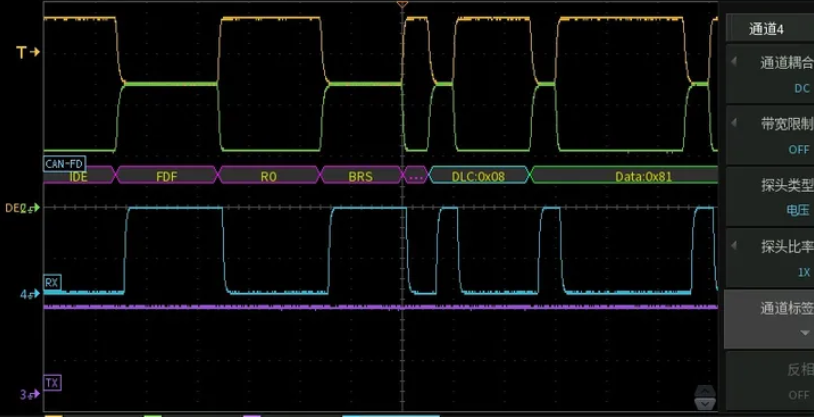

补充知识:CAN-FD网络要求各个节点的采样点必须高度一致。由于速率更高,其对时序的敏感性远高于标准CAN网络(标准CAN允许一定的采样点范围)。上例中BRS位为何会被读错?这里有一个反直觉的点:CAN-FD的采样点设置会影响发送节点的驱动波形! 使用示波器可以清晰地测量出FD报文中各比特位的实际宽度。

看下图,CAN-FD报文控制段中的BRS位,其宽度明显短于前面的FDF、R0等位。如果收发双方采样点不匹配,极易读错。因为CAN-FD的速率切换正是在BRS这一位的采样点位置发生的。例如,在一个采样点设置为80%的2Mbps CAN-FD网络中,BRS位的宽度计算为:2us * 80% + 0.5us * 20% = 1.7us,而不是完整的2us。如果接收节点的采样点设置大于85%(2us * 85% = 1.7us),就可能完全错过BRS位的电平变化,从而导致上述解析错误。

总结

以上就是利用示波器进行“升维”分析,以破解CAN/CAN-FD错误帧及BusOff故障的实战经验分享。总结一下诊断思路:

- 结合先验信息与排除法:结合已知的报文ID与发送节点的对应关系,逐个拔除非关键节点,同时用示波器观察“主动错误标志”的形态变化,可以模糊定位错误源头。

- 监测关键信号:如果能引出疑似问题节点的TX引脚信号,观察其在错误帧过程中的行为,那么“哪个节点认为哪个节点出了什么错”就会变得非常清晰。

- 电流检测法:测量CAN节点的驱动电流,可以清楚地判断在错误标志期间是谁在主导驱动总线,从而锁定故障设备。

- 波形台阶分析法:如果上述方法难以实施,可以仔细分析错误标志期间电压波形的台阶变化,以12us为单位进行拆分,也能推断出大部分错误的原因和参与方。

- 关注单比特异常:额外关注那些仅持续一个标准比特宽度的电压台阶,可以帮助排除部分节点的嫌疑。

通过综合运用这些基于波形物理特性的分析方法,工程师可以超越简单的协议解码,更深入地洞察CAN总线故障的本质,从而实现高效、精准的故障诊断。希望这些来自实战的经验能对你在云栈社区的嵌入式开发与调试工作有所帮助。