市面上超过90%的32位通用微控制器(MCU),其核心都源于同一个家族——ARM Cortex-M系列。从几元钱的消费电子产品到高可靠的工业控制器,再到金融级的安全芯片,Cortex-M几乎覆盖了嵌入式开发的全部场景。

然而,面对M0、M3、M4、M7、M33等诸多型号,许多开发者在芯片选型时往往陷入困惑。选型过高会造成成本和功耗的浪费,选型不足则可能导致项目性能瓶颈或实时性不达标。本文将从架构定位、核心特性、性能差异和适用场景四个维度,为你彻底解析Cortex-M系列,建立清晰的选型逻辑,助你在未来的嵌入式开发项目中精准决策。若你在选型过程中有更多心得,欢迎到云栈社区的嵌入式板块与同行交流探讨。

一、Cortex-M在ARM生态中的定位

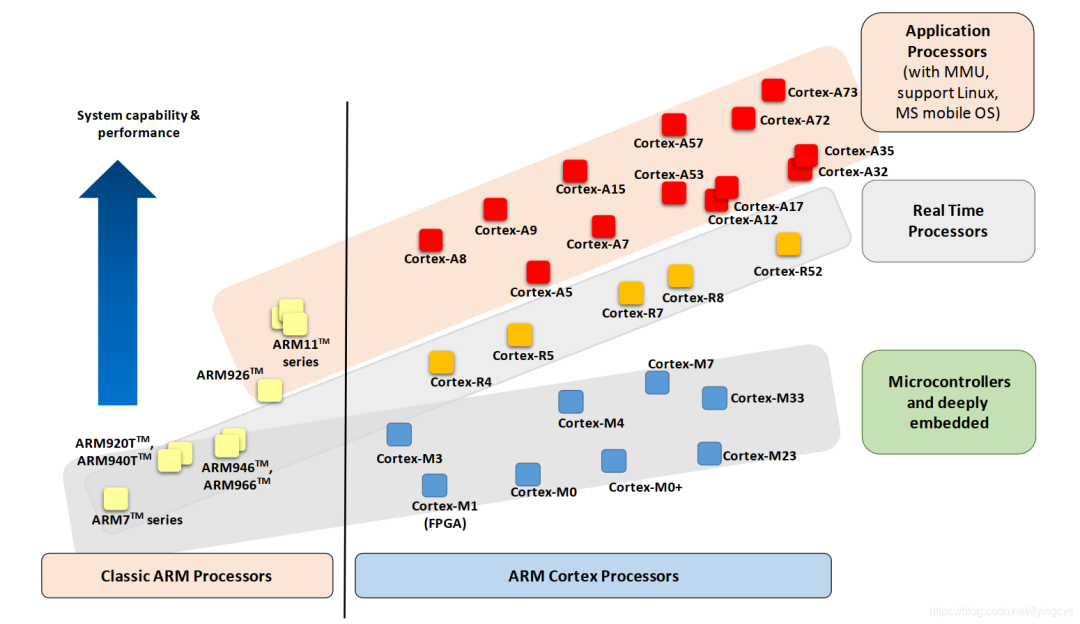

从ARM官方的处理器路线图可以清晰看出其产品线的演进与划分。ARM处理器主要分为经典的ARM7/9/11系列和当前主流的ARM Cortex系列。而Cortex系列根据目标应用场景,清晰地划分为三大分支,三者功能边界明确,几无重叠:

- Cortex-A系列(应用处理器):性能最高的分支,内置MMU内存管理单元,能够运行Linux、Android等完整操作系统。主要面向智能手机、平板电脑、边缘计算设备等需要高算力的场景。

- Cortex-R系列(实时处理器):主打极致的实时性与高可靠性,中断响应延迟极低。专为汽车电子(如ABS、安全气囊)、工业伺服驱动、航空航天等对确定性和容错性要求严苛的领域设计。

- Cortex-M系列(微控制器内核):本文的重点。该系列专为低功耗、低成本、高实时性的深度嵌入式场景而生,无MMU单元,通常运行裸机程序或RTOS(实时操作系统)。它是目前通用嵌入式MCU市场的绝对主流,也是国内芯片厂商的必争之地。

简而言之,Cortex-A负责“智能算力”,Cortex-R负责“极致实时”,而Cortex-M则致力于实现“嵌入式控制的全场景覆盖”。

二、从架构到场景:各型号核心差异解析

Cortex-M系列的演进始终围绕 “控制性能、算力扩展、安全能力” 三大核心方向展开。

1、Cortex-M0:极致的成本与功耗控制

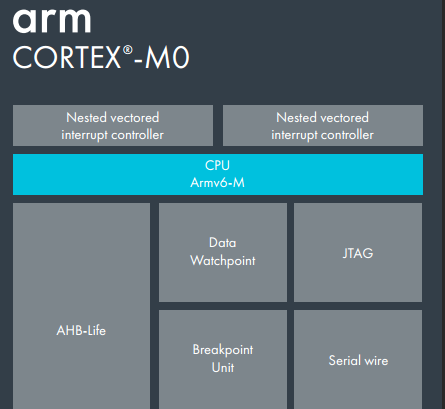

Cortex-M0是ARM为替代传统8/16位MCU(如8051、AVR)而推出的入门级内核,采用Armv6-M架构,是Cortex-M系列中门数最少、功耗和成本最低的型号。

- 核心性能:标称算力约0.84 DMIPS/MHz,主流产品最高主频通常不超过50MHz。采用3级流水线,仅支持精简的Thumb-1指令集和极少量Thumb-2 32位指令。中断数量支持1-32个,无原生的DSP和FPU单元,可选MPU内存保护单元。

- 核心优势:极致的成本与功耗。内核门数仅约12K,使得芯片厂商能以极低的成本量产。其睡眠功耗可低至微安级,完美适配电池供电的简单控制场景。

- 典型适用场景:遥控器、简单的传感器数据采集、LED驱动、消费电子中的辅助控制单元、玩具等纯IO控制场景,是替代传统8位MCU的理想选择。

- 选型避坑:仅适用于纯逻辑控制,切勿用于需要一定算力的场景,如电机控制、信号处理或浮点运算,否则极易出现算力不足的问题。

2、Cortex-M3、M4、M7:性能攀升的“黄金一代”

这三位基于Armv7-M架构的成员,共同推动了32位MCU对8/16位MCU的全面普及,实现了从通用控制到高端算力的场景覆盖。

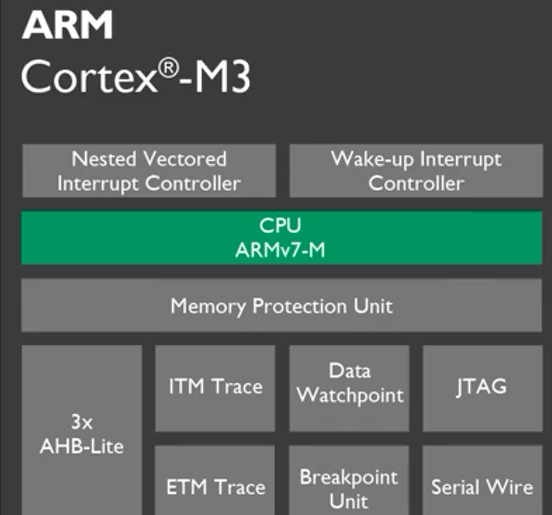

Cortex-M3:经典的通用控制核心

Cortex-M3是无数嵌入式开发者的入门内核,基于Armv7-M架构,在性能、成本和易用性之间取得了绝佳平衡。

- 核心性能:标称算力约1.25 DMIPS/MHz,主流产品最高主频可达200MHz。采用3级流水线,支持完整的Thumb-1与Thumb-2 16/32位混合指令集。NVIC嵌套向量中断控制器支持多达1-240个中断,中断延迟低至12个时钟周期,实时性出色。自带位带操作,可选MPU。

- 核心优势:生态极其完善,开发门槛低,指令集兼容性强。在满足绝大多数工业控制、通用嵌入式需求的同时,保持了优秀的功耗控制。

- 典型适用场景:工业PLC、智能家居主控、汽车车身控制、通用数据采集、消费电子主控等中等复杂度的场景。最具代表性的产品莫过于STM32F103系列,堪称嵌入式领域的“国民神板”。

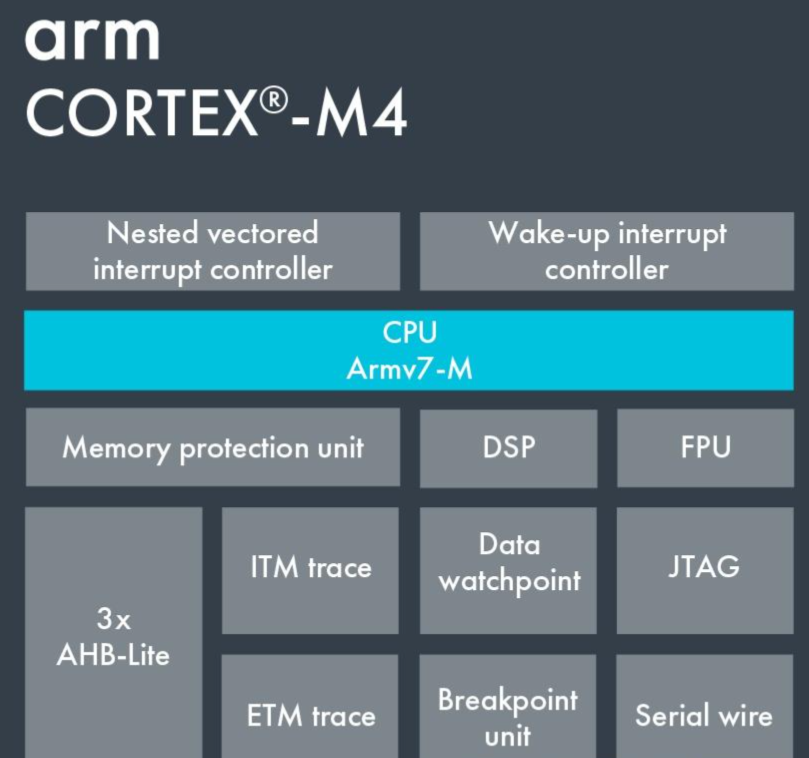

Cortex-M4:控制与轻量级算法的融合

Cortex-M4基于Armv7E-M架构(E代表DSP扩展),是M3的指令集超集,100%兼容M3代码,核心升级在于补强了算力。

- 核心性能:基础算力与M3一致(约1.25 DMIPS/MHz),主频可达250MHz。最大亮点是新增了硬件DSP指令集(支持单周期MAC、SIMD指令)以及可选的单精度FPU浮点运算单元。这使得信号处理、浮点运算的效率相比软件模拟有数量级的提升(10倍以上)。

- 核心优势:在保留M3全部控制优势的基础上,无缝增添了轻量级算法处理能力。开发者无需更换开发框架,即可实现从“纯控制”到“控制+算法”的平滑升级。

- 典型适用场景:电机FOC矢量控制、数字电源、音频编解码、轻量级AI推理、物联网边缘节点信号预处理、医疗电子等。代表产品有STM32F4、F3系列。

Cortex-M7:MCU领域的性能天花板

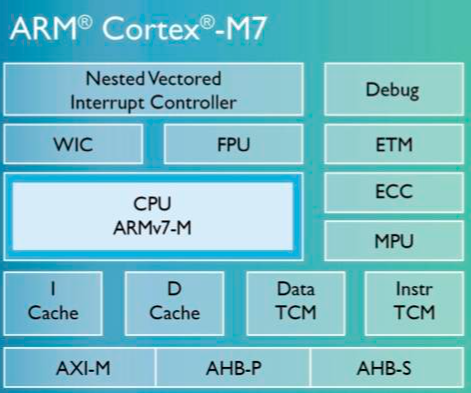

Cortex-M7同样基于Armv7E-M架构,是Cortex-M系列的旗舰性能型号,彻底打破了“MCU只能做简单控制”的刻板印象。

- 核心性能:标称算力高达2.14 DMIPS/MHz,主流产品主频可达400MHz甚至1GHz。采用6级双发射超标量流水线,支持L1指令/数据缓存、TCM紧耦合内存,可配备单/双精度FPU和增强型DSP指令集。其算力已足以支撑轻量级图形界面或机器视觉前端处理。

- 核心优势:在保持MCU高实时性、低功耗特性的前提下,提供了接近低端应用处理器(A核)的算力,能够实现“单芯片完成复杂控制、算法运算和人机交互”的全功能设计,极大简化了硬件方案。

- 典型适用场景:高端工业伺服驱动器、车载HMI显示屏、边缘计算网关、高端音频处理设备、轻量级机器视觉系统等。代表产品为STM32F7、H7系列。

- 选型避坑:M7的成本和功耗远高于其他M系列内核。对于纯IO控制或简单逻辑场景,使用M7无异于“大炮打蚊子”,不仅浪费成本,还可能引入不必要的开发复杂度。

3、Cortex-M33、M35P:物联网时代的安全卫士

随着物联网设备安全需求激增,传统M系列仅靠软件加密的方式已显薄弱。基于Armv8-M架构推出的M33和M35P,核心使命就是提供原生硬件级安全能力。

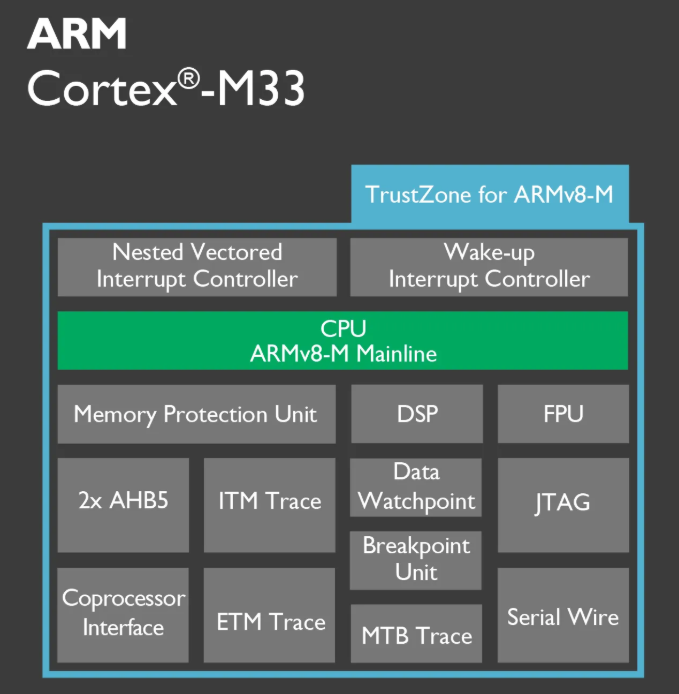

Cortex-M33:TrustZone安全扩展的引入

Cortex-M33基于Armv8-M Mainline架构,在完全兼容M4所有指令集和可选FPU的基础上,首次为中等性能MCU集成了Arm TrustZone硬件安全扩展。

- 核心性能:标称算力约1.5 DMIPS/MHz,主频可达300MHz。采用3级流水线,与M4生态完全兼容。其核心是新增了硬件级的“安全世界”与“非安全世界”双区隔离,并支持安全/非安全双MPU、安全调试权限控制等。

- 核心优势:以极低的成本和功耗增量,实现了金融级的硬件安全隔离。可将密钥管理、加密算法、安全启动等关键逻辑置于受保护的“安全世界”执行,即使“非安全世界”的应用代码被攻破,核心机密数据依然安全。

- 典型适用场景:物联网安全节点、工业安全网关、车规级ECU、生物识别设备、支付终端等。代表产品有STM32L5、U5系列。

Cortex-M35P:物理安全增强版

Cortex-M35P同样基于Armv8-M Mainline架构,其基础算力、指令集和TrustZone能力与M33完全一致,可视为M33的“物理安全增强版”,面向对安全有极致要求的场景。

- 核心升级:在M33的硬件安全隔离基础上,进一步增加了针对侧信道攻击(如DPA/SPA)的防护、物理篡改检测、增强型安全存储、硬件加密加速以及不可逆的安全调试锁等功能。它能同时防御软件破解和物理层面的探针攻击、能量分析等硬件破解手段。

- 核心优势:是Cortex-M系列中安全等级最高的内核之一。无需外挂安全芯片,单芯片即可实现金融级的安全防护,简化了高安全设备的硬件设计,降低了BOM成本。

- 典型适用场景:金融IC卡、政务安全终端、车规安全域控制器、防篡改加密模块、国防电子等。

三、实战选型法则总结

选型的黄金法则是:永远不要选“性能最强的”,只选“最贴合项目需求的”。

你可以遵循以下简单的排序和决策树:

- 性能排序(通用算力):Cortex-M0 < Cortex-M3 ≈ Cortex-M4 < Cortex-M7。

- 安全排序:无专门需求 < Cortex-M33 < Cortex-M35P。

- 成本排序(通常):M0 < M3 < M4 < M33 < M7 < M35P。

选型决策流程参考:

- 需求仅为简单逻辑控制、电池供电、极致成本 -> 首选 Cortex-M0。

- 需求为通用工业控制、复杂外设管理、丰富生态 -> 首选 Cortex-M3。

- 在M3基础上,需要额外的信号处理(如电机控制、简单音频)或浮点运算 -> 升级至 Cortex-M4(带FPU的型号)。

- 需求涉及复杂算法、轻量级GUI、高速数据处理 -> 考虑 Cortex-M7。

- 任何涉及联网、数据隐私、设备认证的物联网产品或工业设备 -> 强烈建议选用支持TrustZone的 Cortex-M33。

- 应用于金融支付、高价值资产追踪、防篡改等对安全有极端要求的领域 -> 评估 Cortex-M35P。

切记,嵌入式MCU选型是一门平衡艺术,过度选型意味着为用不到的性能和功能买单。希望本文能帮助你建立起清晰的Cortex-M系列认知框架,在未来的项目开发中做出更明智的技术决策。 |