当许多用户还在等待PCIe 5.0 SSD普及时,专业领域对I/O带宽的追求却从未停歇。从人工智能训练、高性能计算到大规模数据中心、高速网络,乃至边缘计算、量子计算和汽车电子,对更快数据吞吐的需求正驱动着接口标准的飞速迭代。

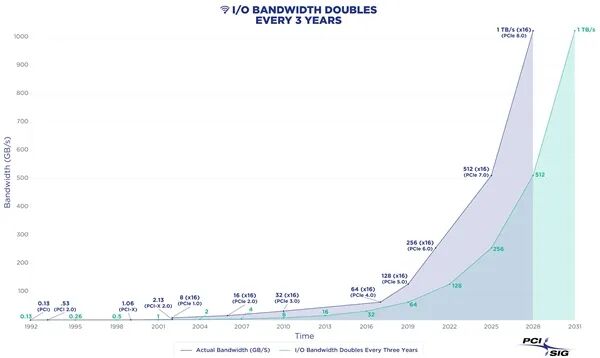

如今,PCIe 6.0和7.0的标准已相继确立,而下一代PCIe 8.0的筹备工作也早已紧锣密鼓地展开。该标准于去年8月初首次宣布,并迅速完成了v0.3版草案的制定,最终正式版本预计将在2028年面世。

PCI-SIG公布的图表显示,I/O带宽保持着约每三年翻一番的增长趋势。

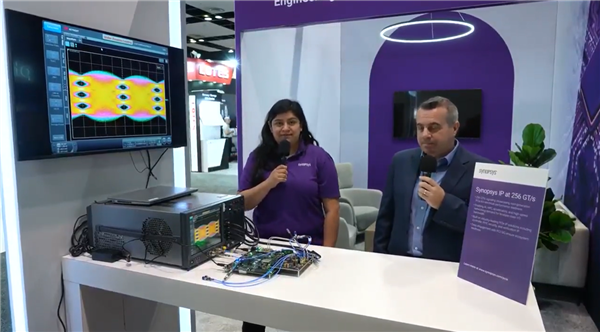

不过,标准规范虽未最终落地,但生态厂商的脚步往往更快一步。在近期举办的DesignCon 2026大会上,新思科技(Synopsys)首次公开展示了符合PCIe 8.0预期的电气性能测试结果,包括关键的眼图分析和接收端性能验证。

根据演示,新思科技的IP方案已经能够实现每通道256 GT/s的数据传输率。若以最常用的x16全链路配置计算,其理论双向总带宽将高达惊人的1TB/s。

新思科技工程师在DesignCon 2026展台进行技术讲解。

需要明确的是,此次演示与以往的新标准早期展示类似,主要是利用现有芯片技术验证PCIe 8.0物理层(PHY)IP的信号完整性。这标志着物理层面实现的重要里程碑,但距离完整的、可用于产品的PCIe 8.0控制器还有相当长的路要走。

对于普通消费者而言,目前了解这一进展即可。毕竟,消费级市场上的PCIe 6.0 SSD、显卡和主板都尚未普及,PCIe 8.0的到来更是遥远。然而,正是这些前沿探索,不断为未来的算力爆发铺平道路。对这类底层技术动态感兴趣的朋友,可以多在云栈社区这样的技术论坛交流探讨。

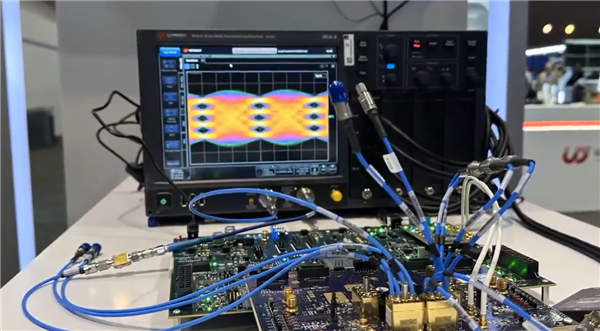

用于测试PCIe 8.0电气性能的示波器与测试板卡。

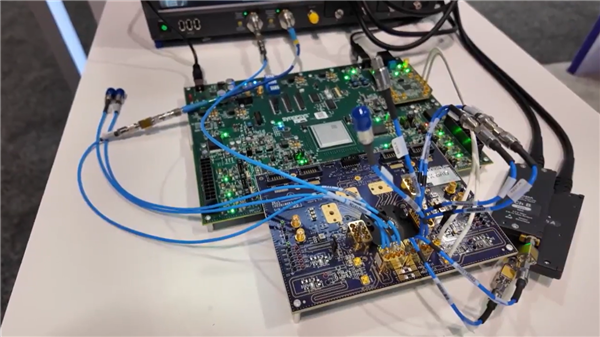

连接着多根光纤的PCIe测试板卡,绿色LED指示灯显示其正在工作中。

|