在现代 ARM 架构的 Linux 系统中,GIC 扮演着中断信号的总调度者角色。想象一下一个繁忙的机场,不同航班(中断)需要降落到不同跑道(CPU核心),而 GIC 就是那位精确指挥每架航班降落时机和跑道的空中交通管制员。

1. GIC 核心架构全景剖析

ARM 通用中断控制器是一个复杂的硬件系统,它将系统中所有中断源集中管理,根据优先级、目标CPU和安全性策略,决定哪些中断应该被处理、何时处理以及由哪个CPU处理。

1.1 GIC 的硬件构成与职责划分

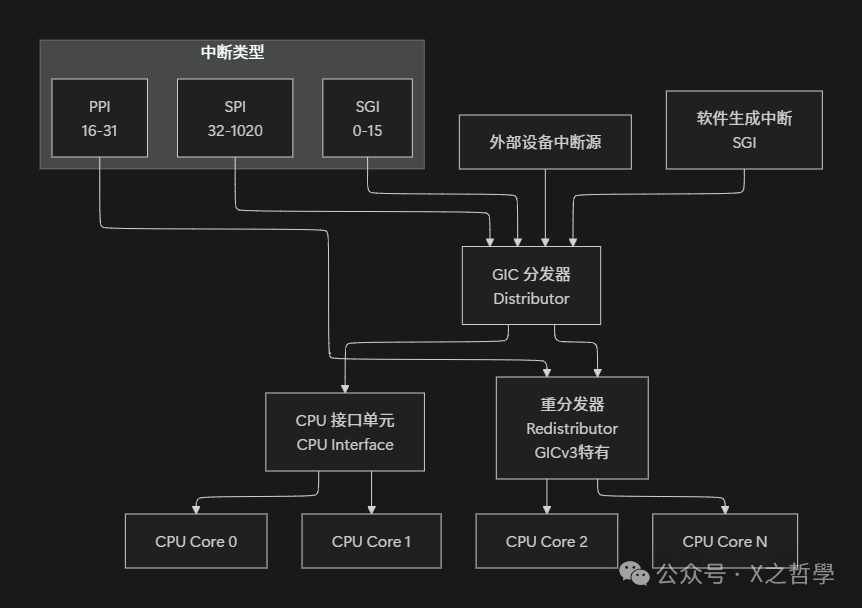

GIC 在硬件上主要由两部分组成:分发器和CPU 接口单元。这两者共同构成了中断管理的完整流水线。

下面的图表展示了 GIC v2/v3 的基本架构组成:

表1: GIC主要组件功能对比

| 组件 |

主要职责 |

类比说明 |

访问特性 |

| 分发器(Distributor) |

接收所有中断源,进行优先级仲裁和路由决策 |

机场总调度中心,决定航班降落顺序和跑道 |

全局共享,所有CPU可访问 |

| CPU接口单元(CPU Interface) |

为单个CPU核心提供中断接口,管理中断屏蔽和确认 |

单个跑道的塔台,与具体飞机通信 |

每个CPU独立,地址相同但硬件隔离 |

| 重分发器(Redistributor) |

在GICv3中管理PPI和SGI,支持电源管理和LPI |

区域调度站,处理本地航班 |

GICv3特有,每个CPU或CPU集群独立 |

1.2 中断类型:软件到硬件的完整谱系

GIC 根据中断来源和特性,将中断分为三类基本类型,这一分类对理解Linux中断处理至关重要:

- SGI (软件生成中断):中断号 0-15,由软件显式触发。想象成机场内部的 对讲机呼叫,用于地勤人员间紧急通信。在Linux中,这主要实现核间通信,例如一个CPU唤醒另一个CPU。

- PPI (私有外设中断):中断号 16-31,特定于某个CPU的外设中断。好比飞行员与个人塔台的专用通信频道。典型例子是每个CPU的私有定时器中断。

- SPI (共享外设中断):中断号 32-1020,可以被路由到任何CPU的全局外设中断。这像是公共航空无线电频率,所有飞行员都能听到,但只有被指定的飞行员回应。常见的外设如GPIO、UART、Ethernet中断都属于此类。

表2: GIC中断类型详细对比

| 特性 |

SGI |

PPI |

SPI |

| 中断ID范围 |

0-15 |

16-31 |

32-1020 |

| 触发方式 |

软件写寄存器 |

硬件信号 |

硬件信号 |

| CPU关联性 |

可定向到特定CPU |

绑定到特定CPU |

可路由到任何CPU |

| 主要用途 |

核间通信 |

CPU私有外设 |

系统共享外设 |

| 状态寄存器 |

每个CPU独立 |

每个CPU独立 |

全局共享 |

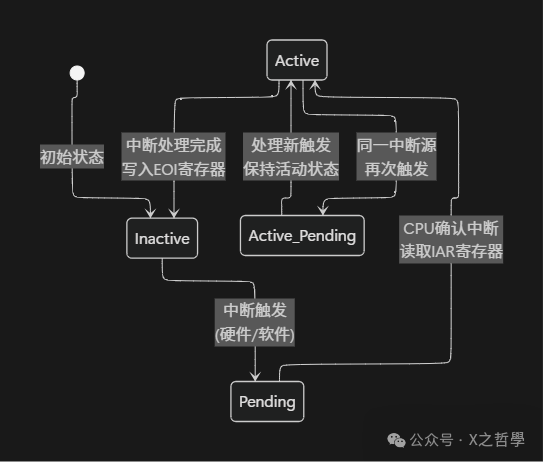

1.3 中断状态机:四态转换的精妙设计

每个中断在GIC中都有一个明确的生命周期,通过四个状态的转换来管理:

- 非活动状态:中断未触发,处于“休眠”状态。

- 挂起状态:中断已触发但尚未被CPU处理,相当于“已按下呼叫按钮但尚未接通”。

- 活动状态:CPU已开始处理中断,但尚未完成。

- 活动且挂起状态:CPU正在处理中断时,同一中断源又触发了新中断。

下面的状态图清晰地展示了这一转换过程:

2. Linux内核中的GIC实现框架

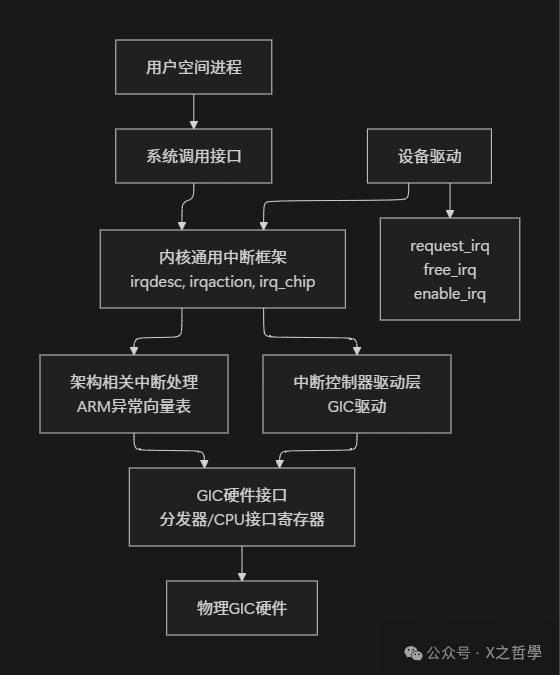

Linux内核的中断子系统是一个多层抽象架构,GIC驱动位于硬件抽象层,向上提供标准化的中断管理接口。

2.1 Linux中断子系统的分层架构

Linux中断处理采用高度模块化设计,从硬件无关的通用接口到具体的硬件驱动,形成了清晰的层次结构:

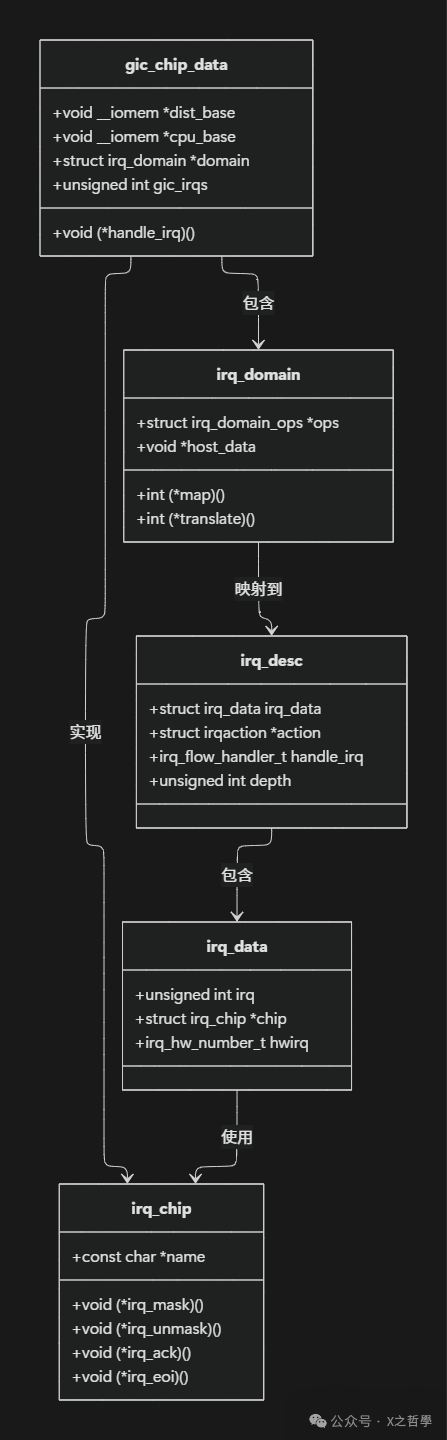

2.2 中断号映射:硬件ID到软件IRQ的转换

这是理解Linux中断处理的关键概念之一。在系统中存在两种编号:

- 硬件中断号:GIC硬件定义的ID,范围0-1020,由芯片手册固定。

- 软件IRQ号:Linux内核内部使用的虚拟中断号,从0开始动态分配。

连接这两者的是 irq_domain 机制,它就像一个翻译官,负责硬件ID和软件IRQ之间的双向转换:

// 典型的irq_domain映射示例 (简化概念)

struct irq_domain {

const struct irq_domain_ops *ops; // 映射操作函数

void *host_data; // 私有数据

// ... 其他字段

};

// GIC驱动中的domain创建

static int gic_irq_domain_map(struct irq_domain *d, unsigned int irq,

irq_hw_number_t hw)

{

// 建立hwirq到virq的映射

irq_domain_set_info(d, irq, hw, &gic_chip, ...);

return 0;

}

2.3 链式与层级中断控制器

在复杂SoC中,GIC往往不是唯一的中断控制器,还可能存在级联的中断控制器。Linux内核将其分为两类处理模型:

- 链式中断控制器:子控制器的所有中断共享GIC的一个中断线,需要软件进一步区分中断源。

- 层级中断控制器:子控制器的每个中断对应GIC的独立中断线,硬件自动处理区分。

表3: 链式与层级中断控制器对比

| 特性 |

链式中断控制器 |

层级中断控制器 |

| 硬件连接 |

共享GIC一条中断线 |

独占GIC中断线 |

| 中断分辨 |

需要软件读取子控制器寄存器 |

硬件自动区分 |

| 性能影响 |

需要额外软件开销 |

硬件高效处理 |

| 典型应用 |

简单的GPIO中断扩展 |

复杂外设模块 |

| 处理流程 |

两级中断处理程序 |

统一中断处理 |

3. GIC核心数据结构与代码实现

深入Linux内核代码,我们可以发现GIC驱动实现了一系列精心设计的数据结构和函数。

3.1 核心数据结构关系

下面的Mermaid图展示了GIC驱动中关键数据结构的关系:

3.2 关键寄存器与驱动代码

从中的Rust GIC驱动代码,我们可以一窥GIC编程的核心模式:

// 基于C语言的GICv2驱动核心函数 (概念代码)

struct gic_v2 {

void __iomem *gicd_base; // 分发器基地址

void __iomem *gicc_base; // CPU接口基地址

};

// GIC初始化

void gic_v2_init(struct gic_v2 *gic)

{

// 1. 使能分发器

writel(GICD_CTLR_ENABLE, gic->gicd_base + GICD_CTLR);

// 2. 配置所有中断为组1 (非安全状态)

for (int i = 0; i < 32; i++) {

writel(0xFFFFFFFF, gic->gicd_base + GICD_IGROUPR + i * 4);

}

// 3. 使能CPU接口

writel(GICC_CTLR_ENABLE, gic->gicc_base + GICC_CTLR);

// 4. 设置优先级掩码 (接受所有优先级中断)

writel(0xFF, gic->gicc_base + GICC_PMR);

}

// 中断使能/禁用

void gic_v2_enable_irq(struct gic_v2 *gic, unsigned int irq, bool enable)

{

unsigned int reg_offset = GICD_ISENABLER + (irq / 32) * 4;

unsigned int bit_mask = 1 << (irq % 32);

if (enable) {

writel(bit_mask, gic->gicd_base + reg_offset);

} else {

writel(bit_mask, gic->gicd_base + GICD_ICENABLER + (irq / 32) * 4);

}

}

// 中断处理入口

irqreturn_t gic_handle_irq(int irq, void *dev_id)

{

unsigned int iar = readl(gic->gicc_base + GICC_IAR);

unsigned int irq_num = iar & GICC_IAR_INT_ID_MASK;

if (irq_num >= 1020) { // 伪中断

return IRQ_NONE;

}

// 转换为Linux IRQ号

unsigned int linux_irq = irq_find_mapping(gic->domain, irq_num);

// 调用通用中断处理

generic_handle_irq(linux_irq);

// 写EOI结束中断

writel(iar, gic->gicc_base + GICC_EOIR);

return IRQ_HANDLED;

}

3.3 设备树绑定:硬件描述的标准化

设备树是描述硬件配置的现代方法,GIC的设备树节点包含关键硬件信息:

// 典型的GIC设备树节点示例

interrupt-controller@2c001000 {

compatible = "arm,cortex-a15-gic";

#interrupt-cells = <3>; // 3个单元描述一个中断

interrupt-controller; // 标记为中断控制器

reg = <0x2c001000 0x1000>, // 分发器寄存器区域

<0x2c002000 0x1000>, // CPU接口寄存器区域

<0x2c004000 0x2000>, // 虚拟接口控制 (可选)

<0x2c006000 0x2000>; // 虚拟CPU接口 (可选)

interrupts = <1 9 0xf04>; // 维护中断

// GICv2m扩展 (用于MSI支持)

v2m0: v2m@0x8000 {

compatible = "arm,gic-v2m-frame";

msi-controller;

reg = <0x0 0x80000 0 0x1000>;

};

};

表4: GIC设备树属性详解

| 属性 |

含义 |

示例值 |

说明 |

| compatible |

设备兼容性 |

"arm,cortex-a15-gic" |

指定GIC版本和实现 |

| #interrupt-cells |

中断描述单元数 |

<3> |

每个中断用3个32位数描述 |

| interrupt-controller |

中断控制器标志 |

空属性 |

标记节点为中断控制器 |

| reg |

寄存器区域 |

<0x2c001000 0x1000> |

基地址和大小对 |

| interrupts |

控制器自身中断 |

<1 9 0xf04> |

GIC的维护中断 |

4. 中断处理完整流程剖析

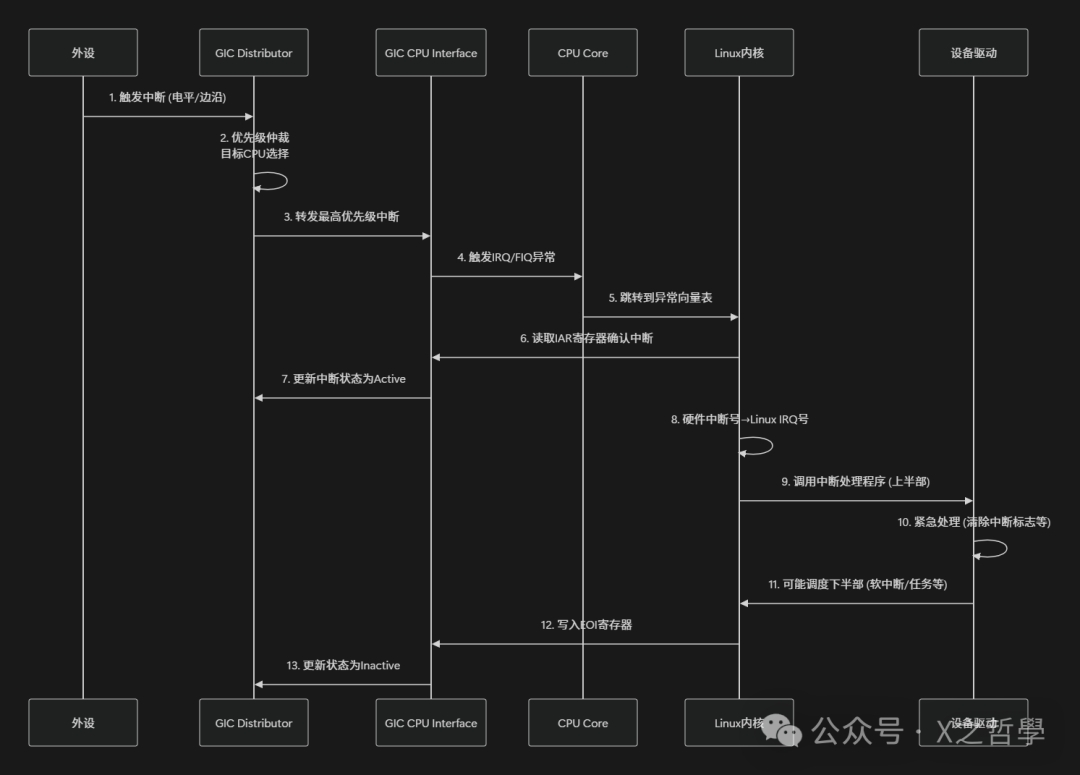

当一个中断从触发到处理完成,Linux内核和GIC硬件协同完成了一系列复杂但有序的操作。

4.1 完整中断处理时序

下面的时序图展示了从硬件中断触发到软件处理完成的完整过程:

4.2 中断上下部机制:紧急与延迟处理的平衡

Linux中断处理的一个关键设计是 中断上下部分割,这一设计源于中断处理的一个基本原则:尽可能快地从中断处理程序中返回。

- 中断上半部:在中断上下文中执行,要求快速完成,通常只做最紧急的工作,如清除中断标志、复制数据到缓冲区。

- 中断下半部:延迟执行,可以完成较耗时的处理,如数据处理、协议栈处理等。

// 典型的中断处理程序结构

static irqreturn_t example_interrupt_handler(int irq, void *dev_id)

{

struct example_device *dev = dev_id;

// 上半部: 紧急处理

// 1. 读取中断状态寄存器

u32 status = readl(dev->base + STATUS_REG);

// 2. 清除中断标志

writel(status, dev->base + STATUS_CLEAR_REG);

// 3. 复制数据到安全缓冲区

memcpy(dev->buffer, dev->data_reg, sizeof(dev->buffer));

// 4. 调度下半部处理

tasklet_schedule(&dev->tasklet);

return IRQ_HANDLED;

}

// 下半部处理函数

static void example_tasklet_handler(unsigned long data)

{

struct example_device *dev = (struct example_device *)data;

// 这里可以进行耗时操作

// 如: 数据处理、协议解析、唤醒用户进程等

process_device_data(dev->buffer);

// 唤醒等待数据的用户进程

wake_up_interruptible(&dev->wait_queue);

}

5. GIC版本演进与Linux支持

ARM GIC自推出以来经历了多个版本的演进,每个版本都引入了重要改进。

表5: GIC主要版本特性对比

| 特性 |

GICv2 |

GICv3 |

GICv4 |

| 引入时间 |

2008年 |

2013年 |

2017年 |

| 支持架构 |

ARMv7, Cortex-A系列 |

ARMv8-A, ARMv9-A |

ARMv8.4-A+ |

| 最大CPU数 |

8个 |

128个 (理论更多) |

256个+ |

| 中断ID范围 |

0-1019 |

0-1019 + LPI |

0-1019 + LPI |

| LPI支持 |

否 |

是 (可选) |

是 (增强) |

| 虚拟化支持 |

基本 |

增强 (直接注入) |

完全硬件虚拟化 |

| 配置存储 |

寄存器 |

寄存器+内存表 |

寄存器+内存表 |

| Linux内核支持 |

3.x+全面支持 |

4.6+主要支持 |

4.19+实验性支持 |

5.1 GICv3/v4的新特性

GICv3及后续版本引入了重要的架构改进:

- 基于消息的中断:支持LPI,配置信息存储在内存表中而非寄存器,提供更好的扩展性。

- 独立的CPU接口:从GIC物理分离,通过AXI Stream接口通信。

- 增强的虚拟化:硬件支持直接向虚拟机注入虚拟中断。

- ITS:中断转换服务,可选组件,处理基于消息的中断转换。

6. 实用调试工具与技巧

在实际开发和调试中,掌握合适的工具和方法至关重要。

6.1 常用调试命令

# 1. 查看系统中断统计

cat /proc/interrupts

# 输出示例:

# CPU0 CPU1

# 16: 0 0 GICv2 27 Level arch_timer

# 33: 1254 0 GICv2 33 Edge eth0

# 2. 查看特定中断的亲和性 (绑定的CPU)

cat /proc/irq/33/smp_affinity

# 输出: 3 (二进制11, 表示绑定到CPU0和CPU1)

# 3. 查看GIC相关内核信息

dmesg | grep -i gic

# 输出GIC初始化信息

# 4. 使用ftrace跟踪中断

echo 1 > /sys/kernel/debug/tracing/events/irq/enable

cat /sys/kernel/debug/tracing/trace_pipe

# 5. 查看中断延迟统计

cat /proc/interrupts | grep -i latency

# 6. 设备树查看GIC配置

dtc -I fs /sys/firmware/devicetree/base | grep -A 10 -B 5 gic

6.2 性能调优建议

- 中断亲和性设置:将特定中断绑定到特定CPU,减少缓存失效。

- 中断合并:对高频小中断进行合并,减少处理开销。

- NAPI机制:网络驱动中使用,在高负载时切换为轮询模式。

- 中断线程化:将中断处理转换为内核线程,提高响应性。

# 设置中断亲和性示例

echo 2 > /proc/irq/33/smp_affinity # 将中断33绑定到CPU1

# 使用irqbalance服务自动优化中断分配

systemctl start irqbalance

7. 从零开始:一个简单的GIC驱动示例

为了将理论转化为实践,让我们创建一个最简单的GIC驱动模块,它注册一个中断处理程序并响应中断。

/*

* 最简单的GIC中断驱动示例

* 假设我们有一个虚拟设备,使用GIC的SPI中断号100

*/

#include <linux/module.h>

#include <linux/interrupt.h>

#include <linux/io.h>

#define VIRTUAL_DEVICE_NAME "example-gic-device"

#define GIC_SPI_IRQ_NUM 100 // 假设的硬件中断号

static int irq_number; // 实际的Linux IRQ号

static void __iomem *virtual_device_regs;

// 中断处理函数

static irqreturn_t example_irq_handler(int irq, void *dev_id)

{

printk(KERN_INFO "GIC中断示例: 收到中断IRQ%d\n", irq);

// 在这里处理实际的中断

// 1. 读取设备状态

// 2. 清除中断标志

// 3. 处理数据等

return IRQ_HANDLED;

}

static int __init example_gic_init(void)

{

int ret;

printk(KERN_INFO "初始化GIC示例驱动\n");

// 在实际驱动中,这里会:

// 1. 映射设备寄存器

// virtual_device_regs = ioremap(REG_BASE, REG_SIZE);

// 2. 从设备树或平台数据获取实际IRQ号

// 假设我们通过某种方式获得了Linux IRQ号

irq_number = gic_get_linux_irq(GIC_SPI_IRQ_NUM);

if (irq_number < 0) {

printk(KERN_ERR "无法获取IRQ号\n");

return -ENODEV;

}

// 3. 注册中断处理程序

ret = request_irq(irq_number, example_irq_handler,

IRQF_TRIGGER_RISING, VIRTUAL_DEVICE_NAME, NULL);

if (ret) {

printk(KERN_ERR "无法注册中断处理程序: %d\n", ret);

return ret;

}

printk(KERN_INFO "已注册中断IRQ%d\n", irq_number);

// 4. 配置设备触发中断 (在实际硬件中)

// writeb(ENABLE_INTERRUPT, virtual_device_regs + CTRL_REG);

return 0;

}

static void __exit example_gic_exit(void)

{

// 清理工作

free_irq(irq_number, NULL);

// 取消映射寄存器

// iounmap(virtual_device_regs);

printk(KERN_INFO "卸载GIC示例驱动\n");

}

module_init(example_gic_init);

module_exit(example_gic_exit);

MODULE_LICENSE("GPL");

MODULE_AUTHOR("GIC示例作者");

MODULE_DESCRIPTION("一个简单的GIC中断处理驱动示例");

表6: GIC驱动开发关键API总结

| API函数 |

用途 |

参数说明 |

返回值 |

request_irq() |

注册中断处理程序 |

irq_num, handler, flags, name, dev_id |

成功返回0 |

free_irq() |

释放中断 |

irq_num, dev_id |

无 |

enable_irq() |

启用中断 |

irq_num |

无 |

disable_irq() |

禁用中断 |

irq_num |

无 |

disable_irq_nosync() |

异步禁用中断 |

irq_num |

无 |

local_irq_save() |

保存并禁用本地CPU中断 |

flags变量 |

无 |

local_irq_restore() |

恢复本地CPU中断状态 |

flags变量 |

无 |

gic_get_linux_irq() |

获取硬件IRQ对应的Linux IRQ |

hwirq |

Linux IRQ号 |

8. 故障排除与常见问题

在处理GIC相关问题时,以下检查清单可能有所帮助:

- 中断未触发:

- 检查GIC分发器是否使能。

- 确认特定中断在分发器中是否使能。

- 验证CPU接口是否使能。

- 检查CPU的CPSR中断屏蔽位。

- 中断处理程序未调用:

- 确认

request_irq成功。

- 检查中断号映射是否正确。

- 验证设备树配置。

- 检查中断触发类型配置。

- 系统性能问题:

- 使用

/proc/interrupts查看中断分布。

- 考虑中断负载均衡。

- 评估是否使用NAPI或中断合并。

- 多核问题:

- 检查中断亲和性设置。

- 验证SMP中断分配。

- 确保核间中断正常工作。

总结:理解Linux GIC的层次与价值

经过对Linux GIC的深入剖析,我们可以看到这是一个多层协同的系统:

- 硬件层:GIC提供物理中断管理能力,包括优先级仲裁、目标路由和状态管理。

- 驱动层:Linux GIC驱动程序将硬件能力抽象为标准接口,维护硬件中断号到Linux IRQ号的映射。

- 框架层:通用中断框架提供

irq_desc、irq_chip等抽象,支持链式和层级中断控制器。

- 设备层:设备驱动程序使用标准API注册中断处理程序,无需关心底层GIC细节。

理解GIC的关键在于掌握 中断流 的全路径:从外设触发,经过GIC硬件仲裁,转换为CPU异常,由Linux异常向量表处理,通过irq_domain映射,最终调用设备特定的处理程序。