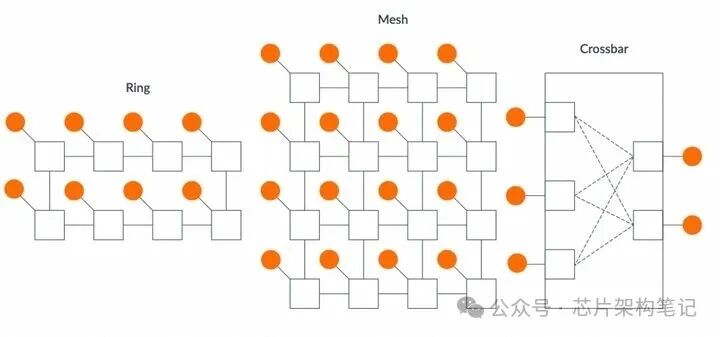

在复杂的SoC芯片设计中,总线互联架构的选择至关重要,它直接关系到系统的性能、功耗和规模。通常,芯片中的总线互联拓扑主要有三种类型:Crossbar(交叉开关)、Ring(环形)和Mesh(网状)。其中,Crossbar拓扑因其全连接、低延迟的特性,非常适合小型或对性能要求苛刻的系统;Ring拓扑则以其简单的扩展性,适用于中等规模的系统;而Mesh拓扑凭借其出色的可扩展性和带宽,是大规模多核系统的理想选择。

本文将聚焦于Crossbar互联,并深入介绍其一个经典的工业实现——来自ARM的CoreLink NIC-400网络互连IP。对于从事芯片设计,尤其是基于ARM架构的计算机架构开发的工程师而言,理解NIC-400的配置与功能是构建高效片上通信网络的基础。

1. NIC-400概述

ARM CoreLink NIC-400是一款通用性强、高度可配置的总线互联IP。设计者可以利用它创建一个完整的高性能、经过优化的、且完全兼容AMBA协议的网络互联系统。其配置灵活性极高,可以从一个简单的协议转换桥(例如AHB到AXI桥),扩展为由多达128个主设备(Master)接口和64个从设备(Slave)接口组成的复杂互连网络。

重要提示:NIC-400本身不负责桥接不同的电源域、电压域或地理(geographic)域。

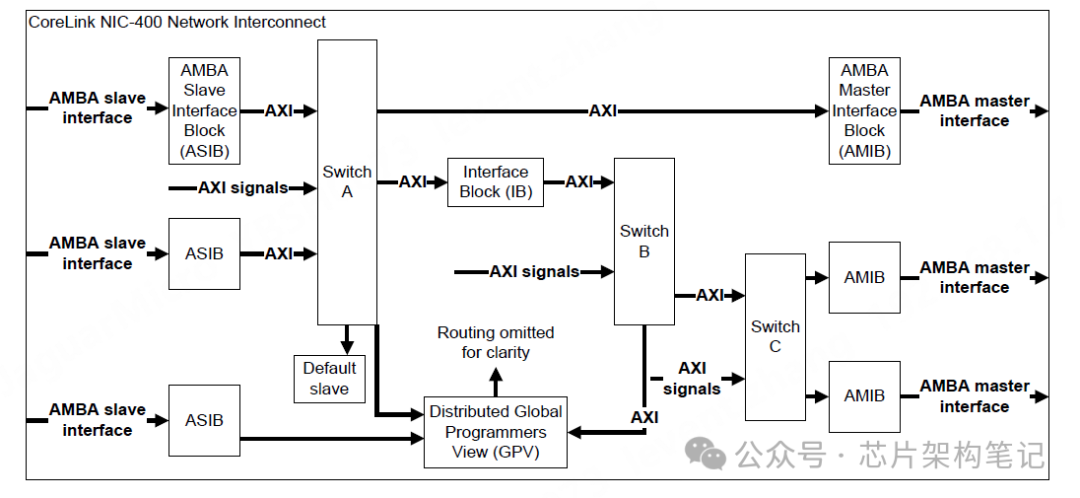

一个NIC-400配置可以由多个交换机(Switch)和接口模块组成,支持多种拓扑选项。其顶层框图清晰地展示了数据在AMBA接口、多个交换机以及各类接口块(如ASIB, AMIB)之间的流动路径。

单个NIC-400实例支持以下关键特性:

- 接口数量:1~128个主接口(支持AXI3, AXI4, AHB-Lite master等);1~64个从接口(支持AXI3, AXI4, AHB-Lite slave等)。

- 位宽支持:AXI和AHB-Lite地址位宽支持32-64位;数据位宽支持32、64、128和256位。

- 性能特性:分层次的时钟门控(Clock Gating)、单周期仲裁、灵活的时序收敛配置。

- 限制:不支持写数据交织(Write Data Interleaving)。

2. NIC-400功能介绍

2.1 NIC-400接口

Slave接口能力:

AXI3和AXI4的从接口支持接收1~32个写事务(Write Transaction)和1~127个读事务(Read Transaction)。如果在ASIB(AMBA Slave Interface Block)中配置了完整的寄存器切片(Full Register Slice),接收能力会增加2;如果配置了前向寄存器切片(Forward Register Slice),则增加1。

Master接口能力:

AXI3和AXI4的主接口支持1~32个写未完成事务(Write Outstanding)。这里有一个设计细节:如果AMIB前面的交换机模块没有看到对应的写数据,它不会发送超过两个的写地址传输。这有助于减少交换机内部的逻辑复杂度,提升系统服务质量(QoS),且不影响写通道的吞吐量。

对于读操作,主接口支持1~127个读未完成事务。在特定条件下(无协议转换、无数据位宽缩放),甚至可以将读未完成能力配置为0,这表示该接口的读未完成能力被视为无限大。

APB接口:

APB主接口可以配置为APB2、APB3或APB4协议,其地址和数据位宽固定为32位。

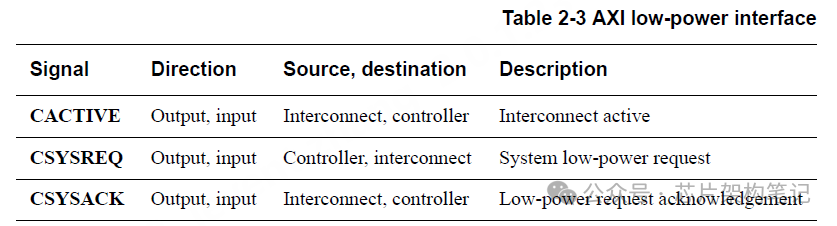

低功耗接口:

NIC-400支持AXI低功耗接口(C通道),用于在系统空闲时请求和确认时钟门控,从而有效降低动态功耗。

2.2 NIC-400操作(数据位宽转换)

NIC-400支持数据位宽的扩展(Upsize)和缩减(Downsize),以适应不同总线宽度的组件。

Upsize功能:

Upsize功能能够以1:2、1:4、1:8的比例扩展数据宽度,仅对可缓存(Cacheable)的读写事务进行数据打包。

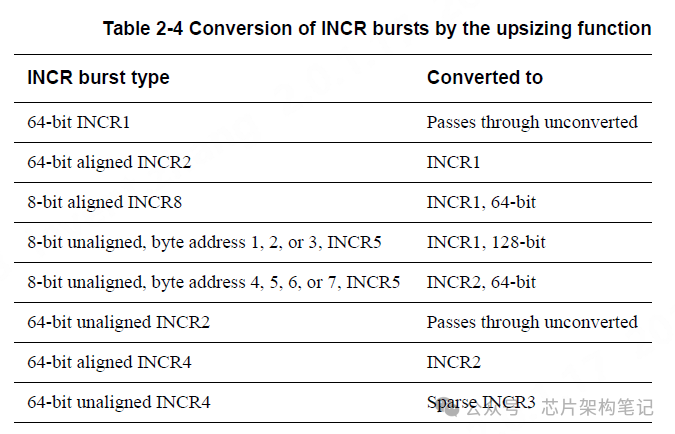

- INCR Burst:互连会将落在单个输出数据宽度内的所有输入INCR Burst转换为可能的最小尺寸的INCR1 Burst。下表展示了upsize功能如何转换INCR Burst(注意:Burst传输不会合并)。

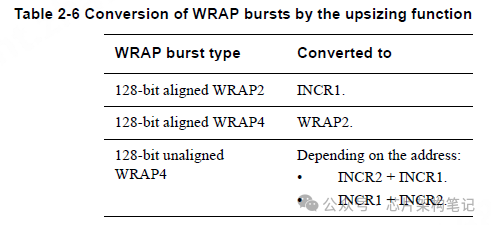

- WRAP Burst:所有的WRAP Burst要么原样通过,要么被转换为输出总线上的一个或两个INCR Burst。

- FIXED Burst:所有FIXED类型的传输都会原样通过(Pass Through),不做任何转换。

Downsize功能:

Downsize功能能够以2:1、4:1、8:1的比例缩减数据宽度。对于非缓存(Non-cacheable)事务,此功能不会合并比目标总线更窄的数据。

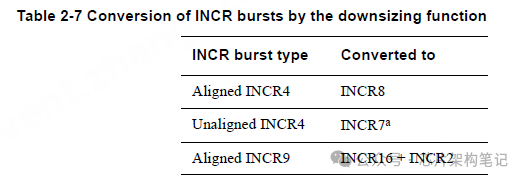

- INCR Burst:处于输出数据总线最大有效负载大小范围内的INCR Burst会被转换为一个INCR Burst;更大的则被拆分为多个。

- WRAP Burst:通常会被转换为长度翻倍的WRAP Burst,直至达到WRAP16的上限。若超过,则视为两个INCR Burst处理。

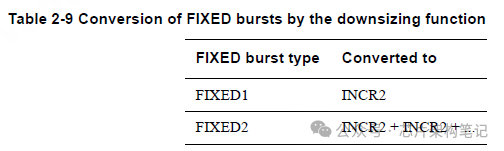

- FIXED Burst:会根据缩小比例,被转换为一个或多个INCR1或INCRn类型的Burst。

2.3 FIFO和时钟功能

当NIC-400被配置为跨时钟域桥接时,需要配置FIFO功能。实际上,即使是1:1的时钟比,也可以配置FIFO用于缓冲。

用户可以在任何通道上实例化FIFO,并配置其用于缓冲和时钟域跨越,支持的方案包括:SYNC 1:1、SYNC 1:n、SYNC n:1、ASYNC以及SYNC m:n。

FIFO的宽度会自动确定为最宽数据包的宽度,深度则可由用户在2到32之间进行配置。

2.4 仲裁功能

NIC-400的所有仲裁节点都可以配置仲裁算法。在事务入口处,每个事务会被分配一个本地服务质量(QoS)值,该值可配置为:

- 静态值。

- 可编程值。

- 从所连接的AXI主设备接收而来。

在仲裁节点上,QoS值更高的事务拥有固定的更高优先级。如果多个待仲裁事务具有相同的QoS值,则采用最近最少使用(LRU)算法进行仲裁。

2.5 NIC-400死锁处理

由于AXI协议支持乱序传输,当多个事务从NIC-400的入口(Slave接口)同时被路由到多个从设备时,可能存在死锁风险。为此,NIC-400引入了循环依赖避免方案(CDAS)。

每个ASIB都可以独立配置不同的CDAS方案(读写事务独立运行相同方案)。NIC-400支持三种方法:

- Single Slave (SS):对于一个ASIB,所有未完成的读事务必须访问同一个目标设备,所有未完成的写事务也必须访问同一个目标设备。该方法对面积和时钟频率影响小,但在主设备期望并发访问不同目标时,对性能影响较大。

- Single Slave per ID (SSPID):对于一个ASIB,所有具有相同ID的未完成读事务必须访问同一个目标,所有具有相同ID的未完成写事务也必须访问同一个目标。这提供了比SS更灵活的并发能力。

- Single Active Slave (SAS):如果存在发往其他主接口的未完成写数据,那么发往当前主接口的AW(写地址)请求会被阻塞。此机制主要用于避免AW-W通道之间的死锁。

总结

ARM CoreLink NIC-400作为一款成熟且高度可配置的互连IP,为芯片设计者提供了构建从简单到复杂片上网络的高效工具。理解其接口能力、数据位宽转换机制、仲裁策略以及死锁避免方案,对于优化SoC的系统性能、功耗和面积至关重要。在实际项目中,需要根据具体的应用场景、主从设备数量及性能需求,仔细配置NIC-400的各项参数,才能充分发挥其价值。更多关于芯片互连与计算机基础的深度讨论,欢迎在云栈社区交流分享。

参考:

- Arm CoreLink NIC-400 Network Interconnect Technical Reference Manual

- https://zhuanlan.zhihu.com/p/347874698?share_code=1cXzYekHo9BMo&utm_psn=2023890831623430726