在上一篇文章中,我们利用 lspci -t -v 的输出,以一个简单的PCIe体系结构为例,重构了它的拓扑结构。本篇我们将对一个包含PCIe Switch的、更为复杂的PCIe体系架构进行实战解析,深入理解系统总线的枚举与分配逻辑。

一、含有PCIe Switch的PCIe体系拓扑结构重建

1. lspci -t -v 输出解析

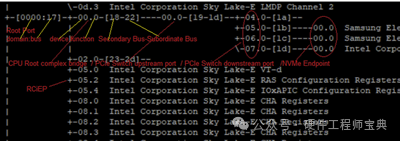

下图是一个含有PCIe Switch的HOST CPU运行 lspci -t -v 命令后的部分输出结果。该系统基于Intel Sky Lake-E双CPU服务器架构,CPU本身集成有两个Root Port和多个Endpoint设备。其中一个Root Port连接了PCIe Switch,另一个则未连接设备。

在开始前,我们先回顾几个关键概念:

- 根节点 (Root Node): 以

+-[0000:17] 开始,其中 0000 表示 PCI 域 (Domain)。系统通常只有一个域。

- 子节点 (Child Nodes): 代表连接到PCI总线上的设备。例如

+-00.0 表示总线17下的一个设备(这里是CPU的Root Port 1)。

- 连接符:

+- 或 \- 表示连接关系,后面紧跟 [Bus:Dev.Fun],即总线号、设备号、功能号。

- [PB:SB.Sub]: 表示PCIe Bridge(或虚拟桥)的三个关键寄存器值:主总线号(Primary Bus Number)、次总线号(Secondary Bus Number)和下级总线号(Subordinate Bus Number)。

图一、含有PCIe Switch的HOST CPU lspci -t -v 输出结果

2. PCIe设备列表

该PCIe体系包含以下设备:

- 一个Host Bridge(由CPU直接承载),其下直接连接总线17。

- 两个PCI Bridge(即CPU的Root Port),ID分别为

17:00.0 和 17:02.0。

- 三个外置的NVMe SSD(独立Endpoint),它们都连接在PCIe Switch的下游端口(Downstream Port)下。

- 多个集成在CPU内部的Endpoint设备。

- 注意:

17:05.0, 17:05.2, 17:05.4 是同一个物理设备(17:05)的三个不同功能(Function)。

17:08.0, 17:08.1, 17:08.2, 17:08.3 是同一个物理设备(17:08)的四个不同功能(Function)。

3. 构建PCIe体系拓扑结构

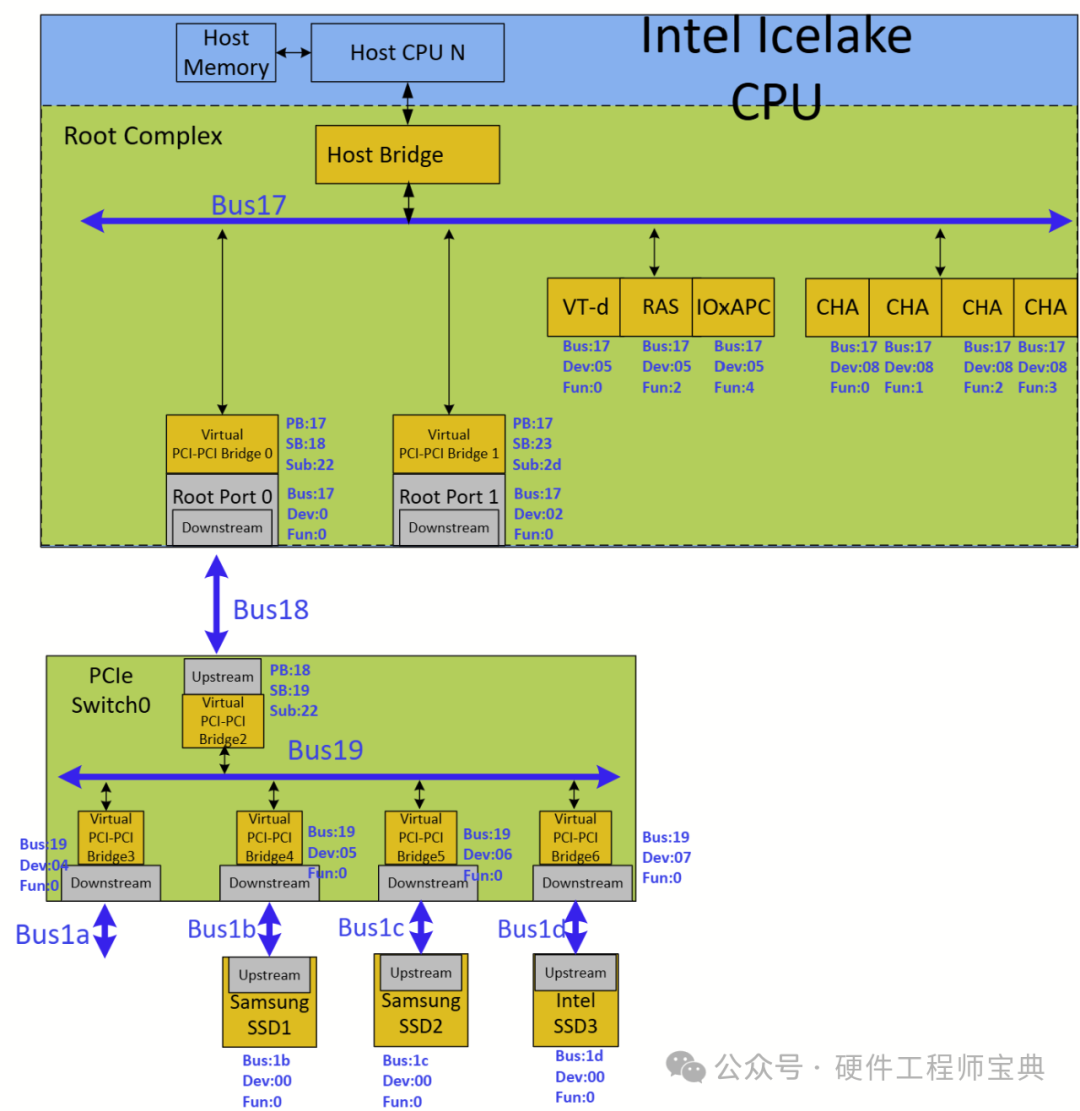

根据 lspci 的输出信息,我们重建出该系统的PCIe拓扑结构,如下图所示:

图二、重建后的PCIe体系拓扑结构

拓扑结构详解:

- 根域与主桥: PCI域为

0000,其下直接承载总线 17。

- 根端口与虚拟桥:

- 总线17下有两个虚拟PCI-PCI桥(Virtual PCI-PCI Bridge),对应CPU的两个根端口。

- Virtual PCI-PCI Bridge 0(ID:

[17:00.0])连接了PCIe Switch。它的总线寄存器值为 [PB=17, SB=18, Sub=22]。这意味着它的上游总线是17,它自己管理的下游总线号从18开始,其下所有子树使用的总线号范围上限是22。掌握 lspci 等命令的输出解读是进行Linux系统底层调试和性能分析的基础技能。

- Virtual PCI-PCI Bridge 1(ID:

[17:02.0])未连接任何物理设备,但BIOS仍为其预留了总线资源,其寄存器值为 [PB=17, SB=23, Sub=2d]。

- PCIe Switch结构:

- Switch的上游端口自身也是一个虚拟桥(Virtual PCI-PCI Bridge 2,ID:

[18:00.0]),寄存器值为 [PB=18, SB=19, Sub=22]。它创建了下游总线 19。

- 在总线19上,连接了四个下游端口的虚拟桥(Bridge 3, 4, 5, 6),每个桥都创建了一条新的下游总线(

1a, 1b, 1c, 1d),并分别挂载了NVMe SSD或空置。例如:

- Bridge 4(ID:

[19:05.0])下游总线为 1b,其上挂载了三星NVMe SSD(ID: [1b:00.0])。

- 集成端点设备: 剩余设备如

[17:05.x] 和 [17:08.x] 均为CPU内部的集成端点,直接位于总线17上,通过多功能形式存在。

三、总结与下期预告

本章通过一个复杂的实例,详细演示了如何利用 lspci 命令解析包含PCIe Switch的系统拓扑,并深入理解了总线号的分配逻辑。这种分析方法对于诊断服务器硬件连接问题、优化IO布局至关重要。

下一章,我们将深入探讨PCIe设备的初始化枚举过程,敬请关注。 |