配置寄存器是SoC或FPGA设计中用于参数配置、状态监控与控制的核心模块。在Verilog或SystemVerilog设计中,这类寄存器堆文件通常被称为配置寄存器文件,理解和掌握其设计方法是开启一个新硬件设计项目的首要步骤。

配置寄存器的核心特点

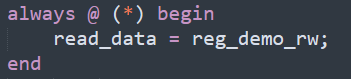

一个典型的配置寄存器堆通常具备以下特征:

- 地址映射:每个寄存器在地址空间中拥有固定的映射地址。

- 多种访问模式:支持读/写、只读或只写等不同访问权限。

- 位字段控制:寄存器内的不同比特位用于控制独立的功能或参数。

- 复位值:每个寄存器或位字段在系统复位后都有一个确定的初始值。

典型的应用场景

配置寄存器几乎出现在所有需要软件动态控制或监控硬件参数的场景中,例如:

- 外设配置:设置UART、SPI、I2C等接口的波特率、模式等。

- 时钟管理:配置PLL倍频参数、时钟分频器。

- 中断控制:使能/屏蔽中断源、设置中断优先级、查询中断状态。

- DMA控制:配置数据传输的源地址、目标地址和传输长度。

- 电源管理:控制芯片的休眠模式、时钟门控等。

- 校准参数:存储ADC/DAC的校准系数。

寄存器读写逻辑的实现与分析

配置寄存器的核心功能就是实现可靠的读写操作。

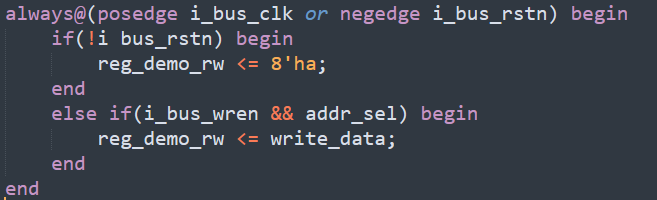

对于一个可读可写的寄存器,其基本的Verilog实现思路如下:

写操作逻辑:

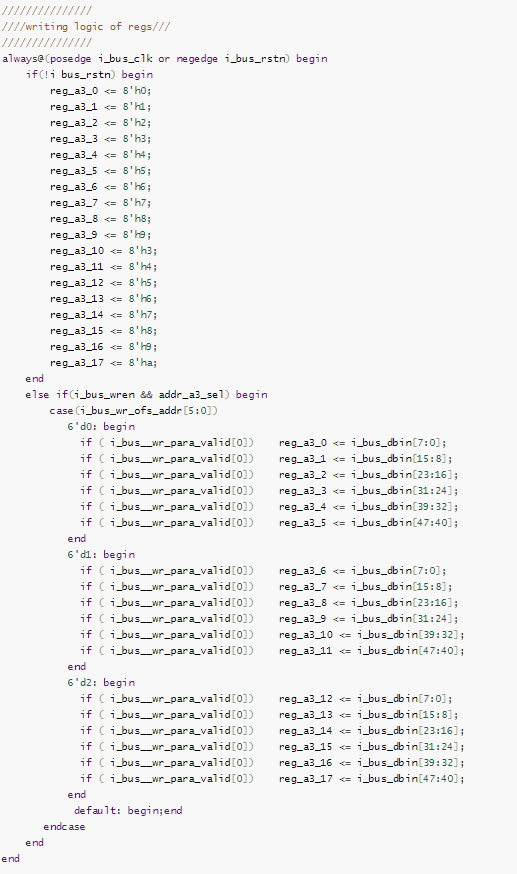

写操作通常是时序逻辑。当写使能信号和对应的地址选择信号有效时,在时钟上升沿将数据总线上的值锁存到目标寄存器中。

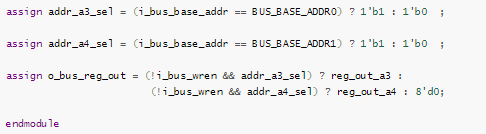

读操作逻辑:

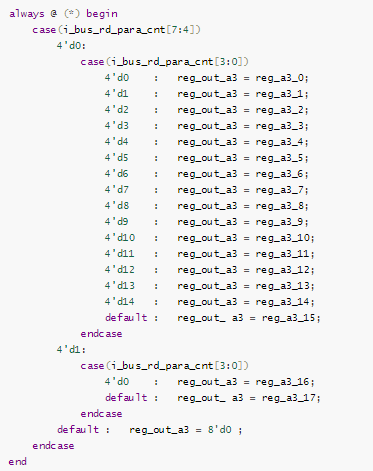

读操作一般是纯组合逻辑。当读使能信号和地址选择信号有效时,直接将对应寄存器的值驱动到读数据总线上,这个过程不消耗额外的时钟周期。

关键设计考量:总线宽度与效率

在实际系统中,一个寄存器地址往往对应一组相关的配置参数。如果数据总线宽度仅为8位,而一个配置组包含多达200个参数,那么通过8位总线逐个写入将极其低效。

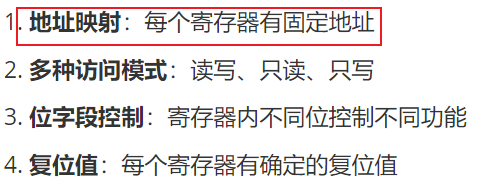

因此,设计时通常会采用更宽的数据总线(如32位、64位或更宽),并配合特定的位字段映射,实现一次写入配置多个参数,从而显著提升配置效率。下图展示了一个寄存器地址与位字段的映射关系示例:

使用Excel与Python实现寄存器代码自动化生成

对于大型设计,手动编写和维护大量的配置寄存器代码容易出错且效率低下。一种高效的实践是使用Excel定义寄存器表,然后通过脚本自动生成RTL代码。

一个标准的寄存器定义表格模板包含以下关键列:

- TYPE:寄存器类型(RW-读写, RO-只读)。

- CMD:寄存器的基地址。

- PARA/PARA_ADR/PARA_VALID:用于定义参数组、一次写入的字节数(数据宽度)以及每个参数在数据总线中的位置。

- D7-D0:描述一个字节(8bit)中每一位的功能定义。

- INIT:寄存器的复位初始值。

基于这样的表格,我们可以编写Python脚本进行自动化解析,并生成对应的Verilog寄存器模块代码。这种方法确保了文档(Excel表格)与代码(RTL)的一致性,极大降低了维护成本。通过脚本,可以一键生成寄存器地址解码、读写控制逻辑以及位字段映射等所有硬件代码。

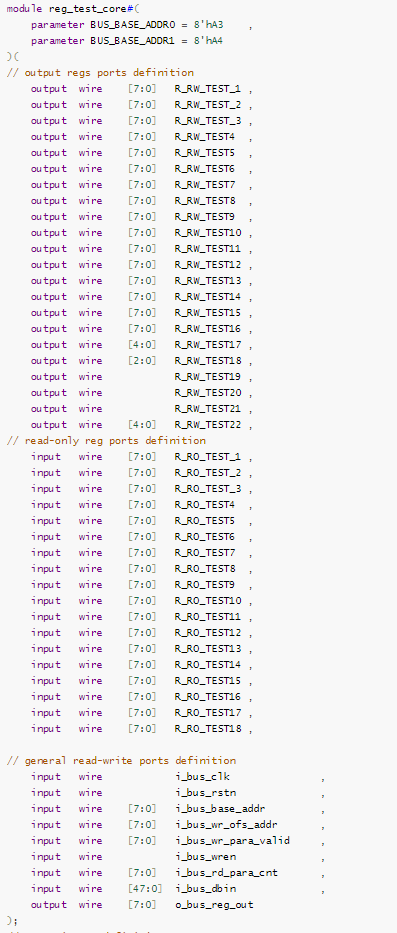

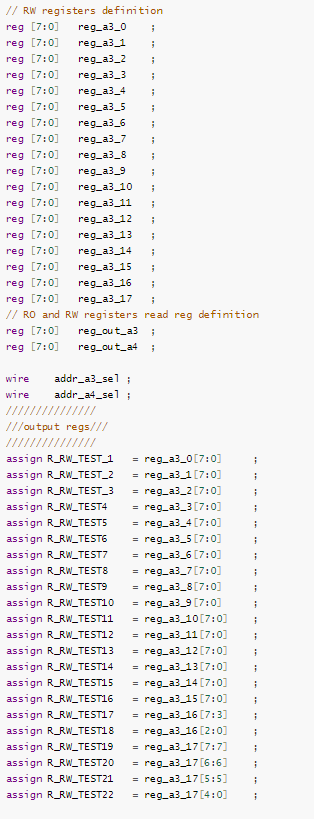

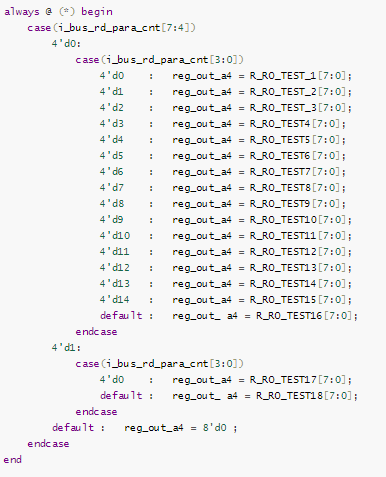

以下是自动化工具可能生成的部分代码结构示意:

|