在如今的SoC(片上系统)设计中,中断控制器往往呈现多级级联的复杂拓扑结构。Linux内核通过引入 IRQ Domain 抽象层,实现了对异构中断控制器的统一管理和中断号的透明映射。这套机制是如何优雅地处理从简单控制器到复杂多级级联的中断系统的呢?

一、中断控制器级联的现实需求

1.1 SoC中断拓扑的复杂性

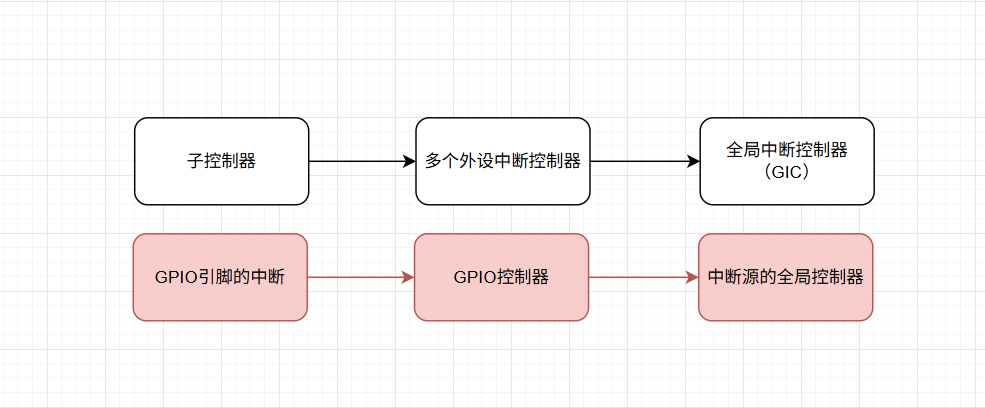

现代SoC通常包含多个中断控制器,形成树形或层级的拓扑结构。典型的架构包括:

- 一个全局中断控制器(GIC)作为根节点

- 多个外设中断控制器(如GPIO、I2C、SPI控制器)作为子节点

- 子控制器可能进一步级联更细粒度的中断源

例如,一个支持32个中断源的全局控制器中,其中4个中断号被分配给4个GPIO控制器,每个GPIO控制器又管理32个GPIO引脚的中断。这种层级关系要求软件框架能够高效管理中断的传播和处理。

1.2 中断号的层级映射问题

在这种级联结构中,中断号呈现双重映射特性:

- 第一级映射:子控制器在父控制器中的中断号(如GPIO控制器1占用全局中断号28)

- 第二级映射:子控制器内部中断源的本地编号(如gpio0_0在GPIO控制器1中的编号为0)

- 系统全局映射:Linux内核需要为所有中断源分配唯一的虚拟中断号(virtual IRQ)

二、IRQ Domain:中断控制器的软件抽象

2.1 Domain的核心概念

IRQ Domain是Linux内核为每个中断控制器创建的软件抽象,主要职责包括:

- 管理硬件中断号(hwirq)到虚拟中断号(virq)的映射关系

- 提供中断控制器的操作函数集(irq_chip)

- 维护中断控制器的拓扑连接信息

中断号就像学生的全校学号,通过“年级→班级→座位”的层级映射,最终每个中断源都有一个统一的编号,设备只需知道这个最终编号就能申请中断。

2.2 Domain的创建与初始化

中断控制器驱动在初始化阶段创建并注册自己的IRQ Domain:

struct irq_domain *irq_domain_add_linear(struct device_node *of_node,

unsigned int size,

const struct irq_domain_ops *ops,

void *host_data);

参数解析:

of_node:设备树节点,描述控制器的硬件信息size:该控制器管理的中断源数量ops:Domain操作函数集,实现映射、转换等核心功能host_data:指向控制器私有数据的指针

2.3 三种映射策略

内核提供多种映射策略,以适应不同硬件架构。对于中断号的映射管理,这属于 操作系统 底层核心机制的一部分。

// 1. 线性映射:适用于固定、连续的中断号范围

struct irq_domain *irq_domain_add_linear(...);

// 2. 树形映射:适用于稀疏、非连续的中断号

struct irq_domain *irq_domain_add_tree(...);

// 3. 传统映射:向后兼容旧式驱动程序

struct irq_domain *irq_domain_add_legacy(...);

线性映射使用数组,树形映射使用radix树。线性映射的查找速度是O(1),而树形映射的查找速度是O(log n)。因此,对于连续且数量固定的中断控制器,通常使用线性映射。但是,如果中断控制器的中断号是稀疏的(即不是连续分配),那么线性映射会造成内存浪费,此时树形映射更合适。

三、中断号映射机制详解

3.1 映射的建立过程

当设备通过设备树描述中断连接关系时,内核自动建立映射:

// 设备树示例

gpio2: gpio-controller@48051000 {

compatible = "ti,omap4-gpio";

interrupt-parent = <&gic>; // 父控制器为GIC

interrupts = <29 IRQ_TYPE_LEVEL_HIGH>; // 在GIC中使用29号中断

gpio-controller;

#gpio-cells = <2>;

};

my_device {

compatible = "vendor,my-device";

interrupt-parent = <&gpio2>; // 连接到GPIO控制器2

interrupts = <0 IRQ_TYPE_EDGE_RISING>; // 使用GPIO2的第0个引脚

};

内核解析过程:

- 为

gpio2 创建IRQ Domain,管理32个中断源

- 建立GIC中断号29与gpio2 Domain的关联

- 为

my_device 分配虚拟中断号:hwirq 0 → virq 64

- 建立gpio2 Domain中hwirq 0到virq 64的映射

3.2 映射数据结构

内核通过以下关键数据结构维护映射关系:

struct irq_domain {

struct list_head link; // 全局Domain链表

const struct irq_domain_ops *ops; // 映射操作函数

void *host_data; // 控制器私有数据

unsigned int flags; // Domain特性标志

int mapcount; // 当前映射数量

/* 线性映射专用字段 */

unsigned int linear_revmap[]; // 硬件中断号到虚拟中断号的查找表

};

struct irq_data {

struct irq_chip *chip; // 硬件操作函数集

struct irq_domain *domain; // 所属Domain

unsigned int hwirq; // 硬件中断号

unsigned int irq; // 虚拟中断号

...

};

四、中断处理流程分析

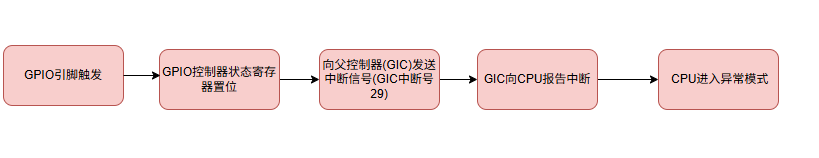

4.1 中断触发与传播

当中断发生时,硬件处理流程如下:

和软件的协同处理流程如下:

4.2 级联中断处理函数

每个子中断控制器需要注册级联处理函数:

static void gpio_irq_handler(struct irq_desc *desc)

{

struct irq_domain *domain = irq_desc_get_handler_data(desc);

struct gpio_ctrl *ctrl = gpio_domain_get_host_data(domain);

unsigned long pending;

// 读取中断状态寄存器

pending = readl(ctrl->base + INT_STATUS_OFFSET);

// 处理每个触发的中断

for_each_set_bit(hwirq, &pending, 32) {

// 关键步骤:硬件中断号到虚拟中断号的转换

virq = irq_find_mapping(domain, hwirq);

if (virq) {

// 调用通用中断处理框架

generic_handle_irq(virq);

}

}

// 可选:向父控制器发送EOI

if (desc->irq_data.chip->irq_eoi)

desc->irq_data.chip->irq_eoi(&desc->irq_data);

}

4.3 中断控制器的注册与连接

完整的中断控制器初始化流程:

static int gpio_interrupt_probe(struct platform_device *pdev)

{

struct device_node *np = pdev->dev.of_node;

struct gpio_ctrl *ctrl;

int parent_irq, ret;

// 1. 分配控制器数据结构

ctrl = devm_kzalloc(&pdev->dev, sizeof(*ctrl), GFP_KERNEL);

// 2. 创建IRQ Domain

ctrl->domain = irq_domain_add_linear(np, 32,

&gpio_irq_domain_ops, ctrl);

// 3. 获取父中断号

parent_irq = irq_of_parse_and_map(np, 0);

// 4. 注册级联处理函数

irq_set_chained_handler_and_data(parent_irq,

gpio_irq_handler,

ctrl->domain);

// 5. 配置硬件中断控制器

gpio_hw_init(ctrl);

return 0;

}

五、设备驱动程序的中断使用接口

5.1 透明的中断申请机制

设备驱动程序无需关心中断控制器的级联细节,这得益于内核提供的统一抽象层,其原理与 计算机基础 中的分层思想一致。

static int my_device_probe(struct platform_device *pdev)

{

struct device *dev = &pdev->dev;

int irq, ret;

// 自动完成中断号映射

irq = platform_get_irq(pdev, 0); // 返回映射后的虚拟中断号

// 申请中断处理函数

ret = devm_request_irq(dev, irq, my_device_isr,

IRQF_TRIGGER_RISING | IRQF_ONESHOT,

dev_name(dev), priv);

return ret;

}

5.2 中断处理函数的执行上下文

当中断最终分发到设备驱动时:

static irqreturn_t my_device_isr(int irq, void *dev_id)

{

struct my_device *dev = dev_id;

// 1. 读取设备状态寄存器

u32 status = readl(dev->regs + STATUS_REG);

// 2. 处理中断事件

if (status & DATA_READY_MASK) {

// 处理数据就绪事件

process_data(dev);

}

// 3. 清除中断标志

writel(status, dev->regs + STATUS_REG);

return IRQ_HANDLED;

}

总结

Linux内核的IRQ Domain机制通过软件抽象,成功解决了硬件中断控制器级联带来的复杂性。它将硬件的层级关系对上层设备驱动完全透明化,使得驱动开发者可以像使用单一中断控制器一样编写代码。这种设计体现了内核在 网络/系统 底层架构中一贯追求的解耦与抽象思想。理解这套机制,对于深入进行嵌入式Linux驱动开发或内核相关的工作至关重要。想了解更多类似的技术解析和实战经验,欢迎访问 云栈社区 与广大开发者交流探讨。