FPGA入门对于初学者来说往往具有挑战性,主要由于学习门槛高和开发板成本高。市面上入门级FPGA开发板价格普遍较贵,例如经典的Artix-7系列基础款就需要数百元。

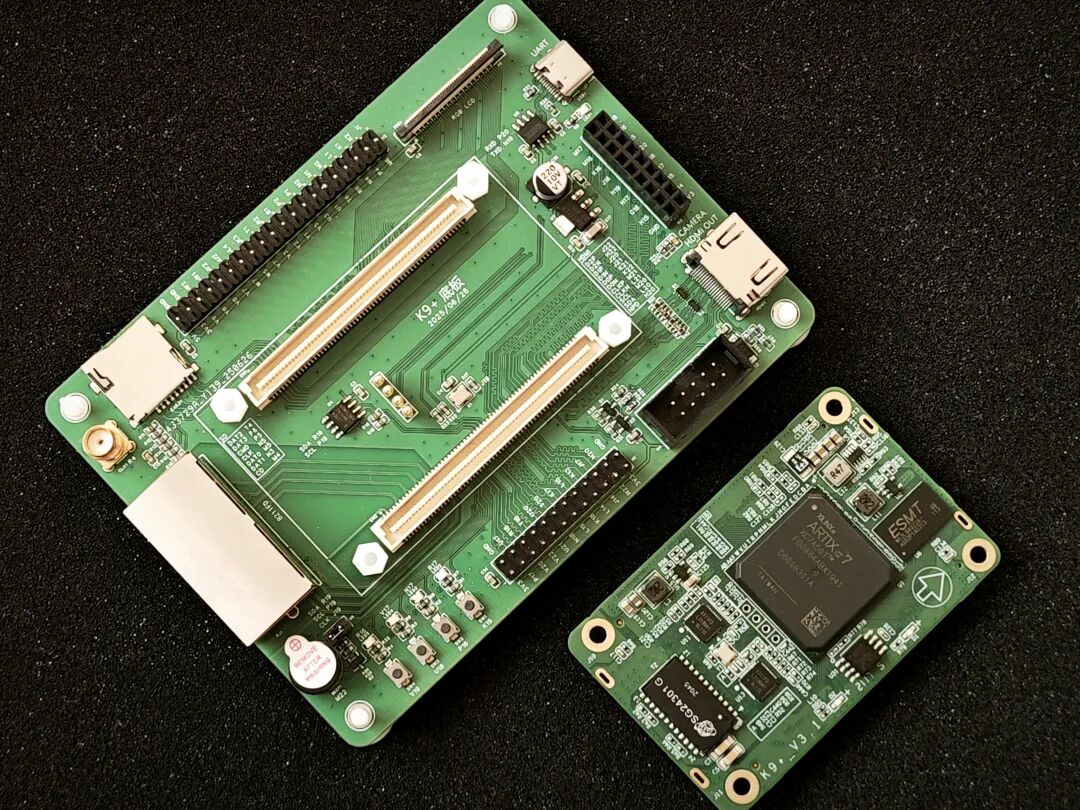

近期在二手平台发现一款从显示屏拆机的图像接收卡核心板,核心芯片为XC7A50T——采用28nm工艺,提供50K逻辑单元。卖家还专门开发了配套底板,充分发挥拆机核心板的性能。底板上集成LED、按键、网口、HDMI等基础外设,并预留扩展接口,方便后续连接传感器、摄像头或显示屏进行实战项目开发,非常适合FPGA入门学习。价格仅为135元,远低于全新开发板,对于从基础逻辑电路和Verilog语法开始学习的用户来说,这款兼具性能、扩展性和性价比的板子,搭配下载器后是理想选择。

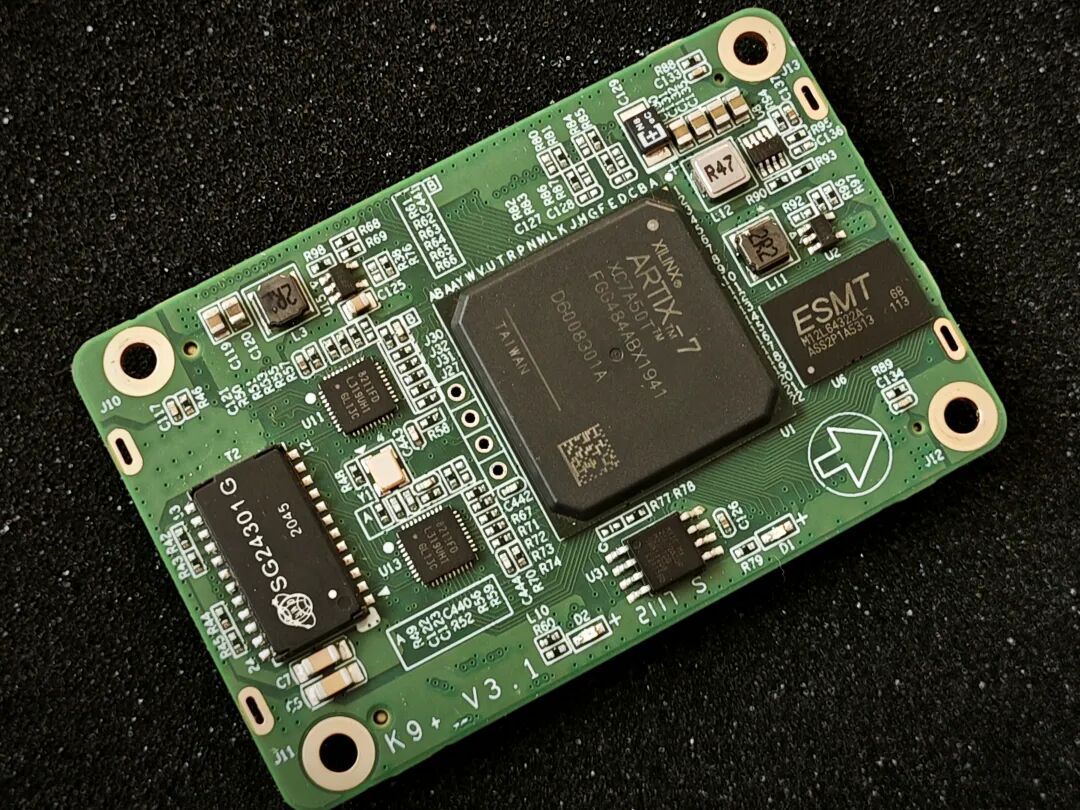

核心板硬件资源

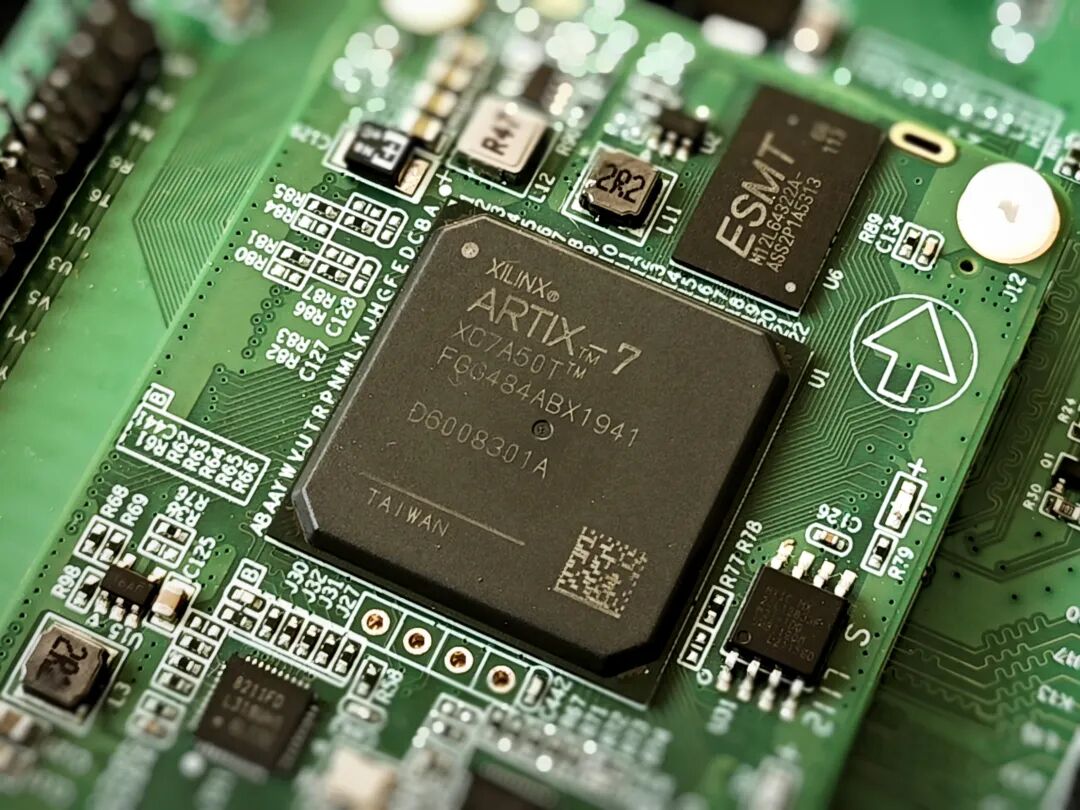

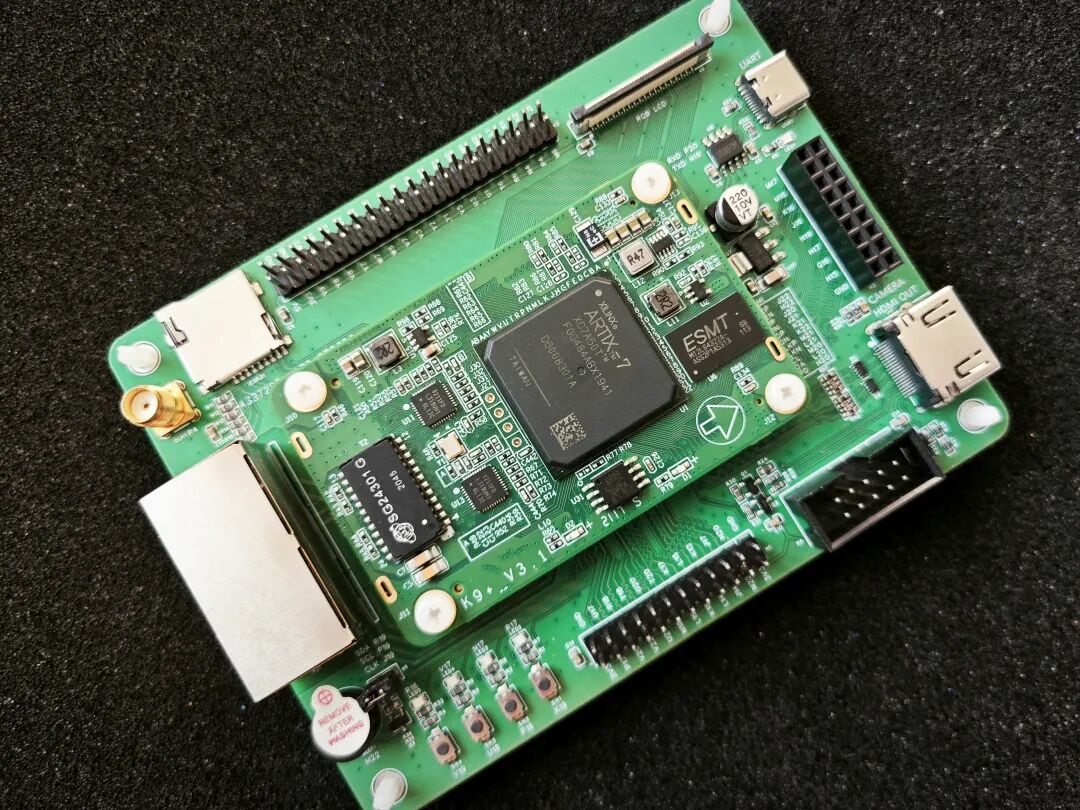

该核心板原为某品牌显示屏控制板上的图像接收卡,虽为二手拆机件,但硬件配置完整。核心采用Xilinx Artix-7系列的XC7A50T芯片,28nm工艺,52K逻辑单元,资源规模适中,既不会浪费也不会限制基础项目开发,堪称入门黄金配置。

网络配置方面,板载两颗瑞昱RTL8211千兆网卡,采用RGMII接口,共享25M有源晶振,并设置不同物理地址(0x1和0x2)以避免冲突。FPGA时钟源自网卡的CLKOUT管脚,频率25M。

存储部分采用旺宏MX25L128芯片,单线SPI接口,容量128Mb(16MB),满足程序和配置文件存储需求。内存使用ESMT M12L64322A SDRAM,容量64Mb(8MB),可缓存图像数据,入门学习足够流畅。

电源设计简洁,单路5V供电即可,板载DC/DC和LDO自动转换为3.3V、1.8V、1.0V等所需电压,无需用户自行设计电源电路,对新手非常友好。

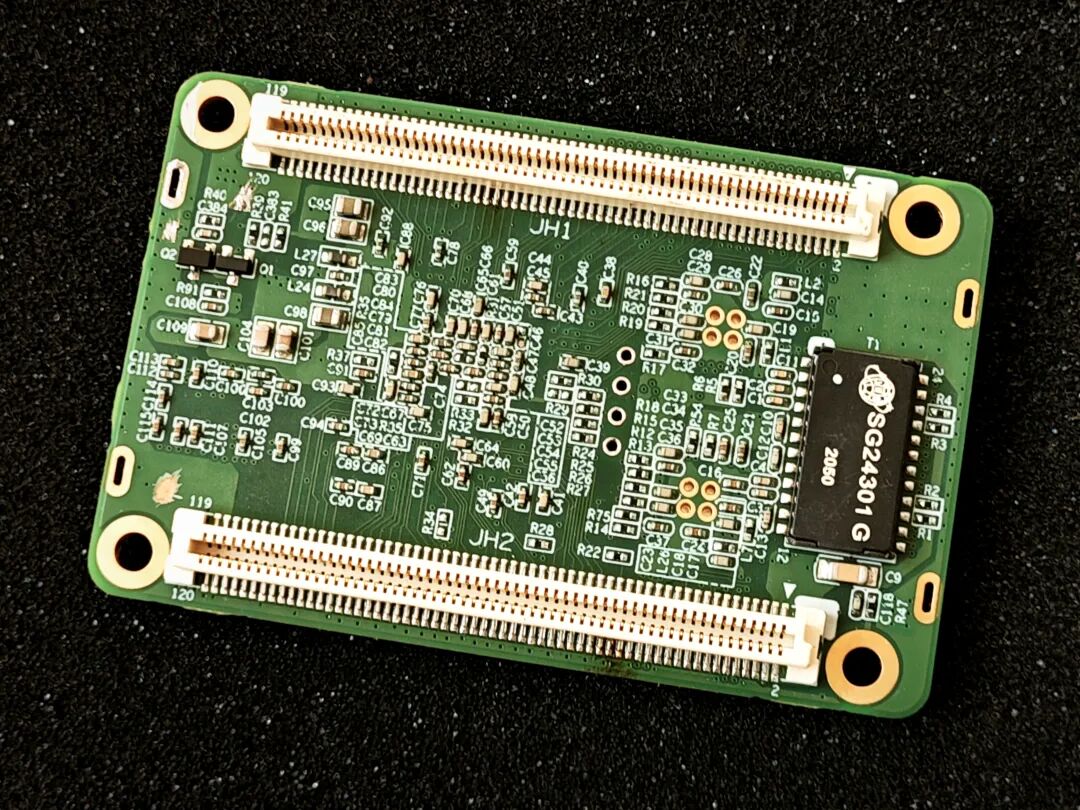

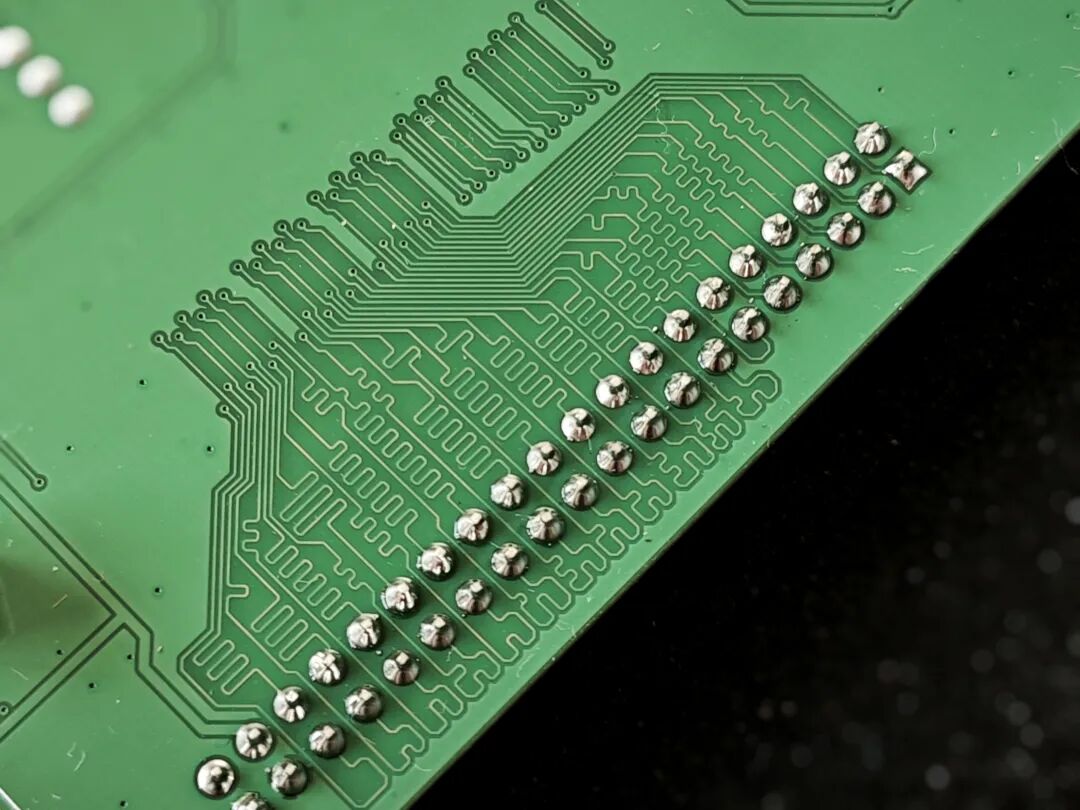

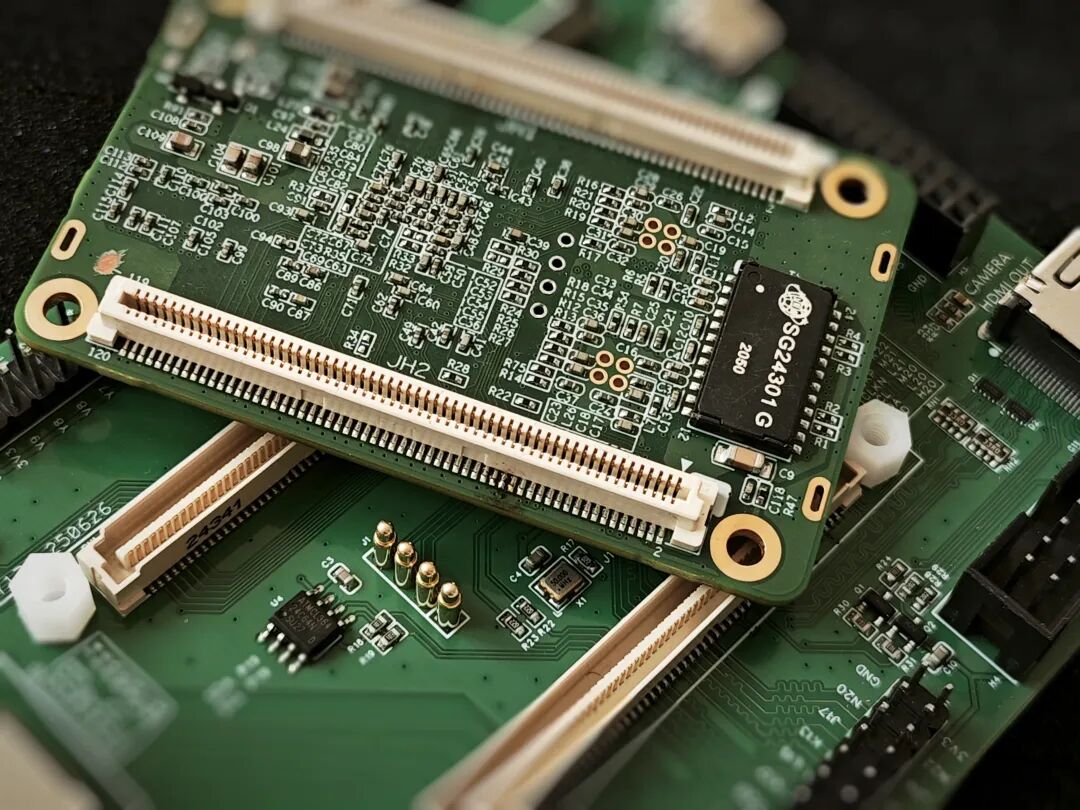

其他细节包括:两颗SG24301G网络变压器,信号通过板对板接口引出;JTAG接口为标准4P 2.54mm排针,可直接连接仿真器;对外接口为两个120Pin 0.8mm间距板对板连接器。板载两个LED——红色为电源指示灯,绿色为用户灯(低电平点亮),适合练习基础IO控制或呼吸灯效果。

总体而言,核心板资源设计实用且周全,核心部件齐全,所有引出管脚均为3.3V电平标准,避免烧件风险。

底板硬件资源

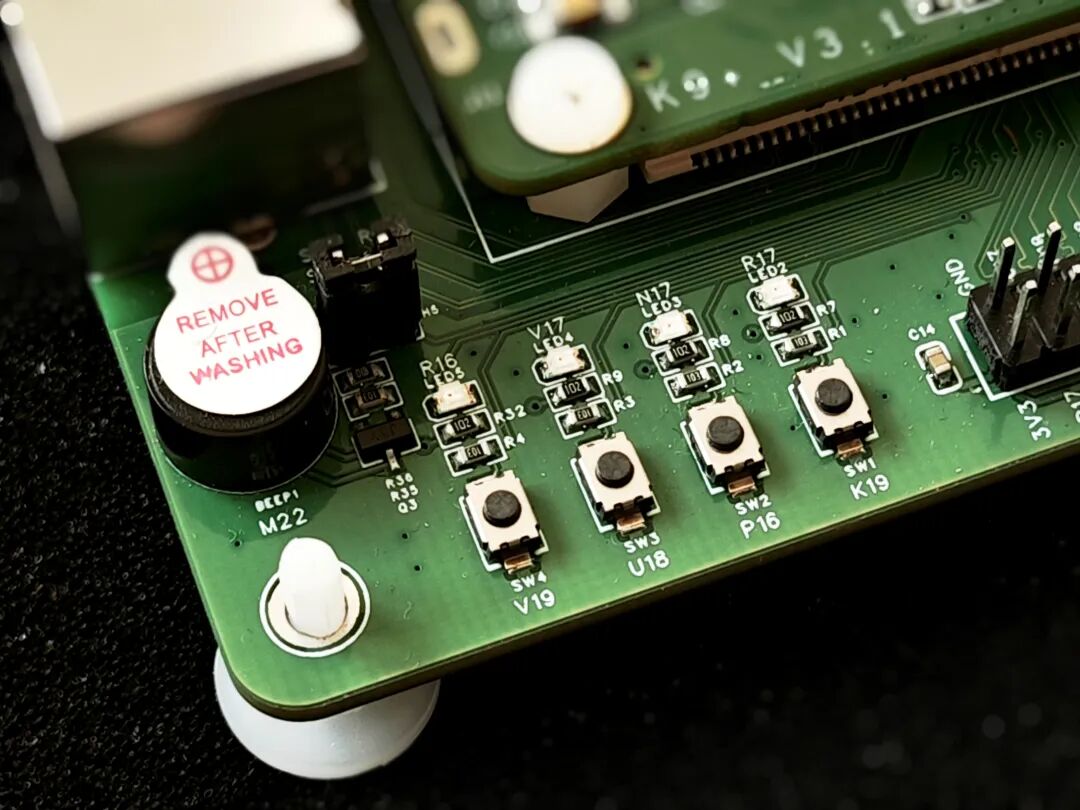

底板扩展资源丰富,支持从入门到进阶的学习需求。配备两路千兆网口座,可用于练习FPGA实现UDP等网络协议,开展高速通信实验。板载1路有源蜂鸣器(跳线帽控制)、4颗用户LED和4路轻触按键(均低电平有效),适合基础IO实验。

时钟系统包含1路50M有源晶振,直连FPGA全局时钟管脚,为高速实验提供稳定时钟源。存储扩展配备24C64 EEPROM芯片,用于学习IIC接口通信。

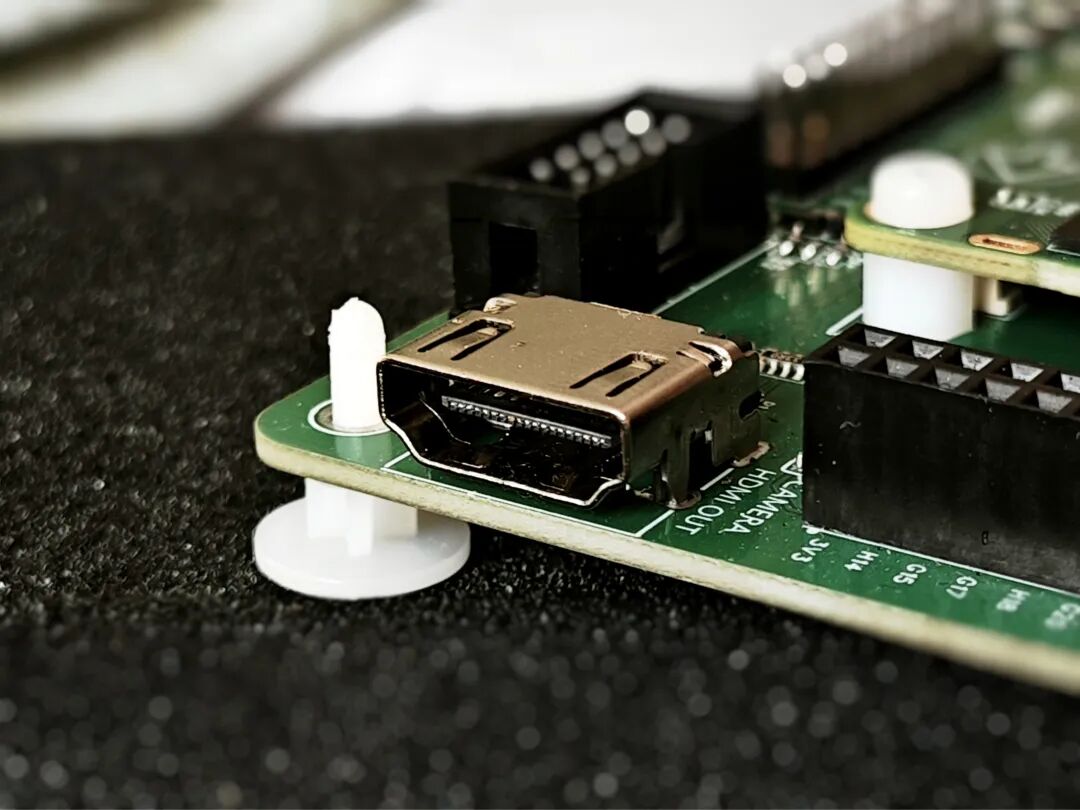

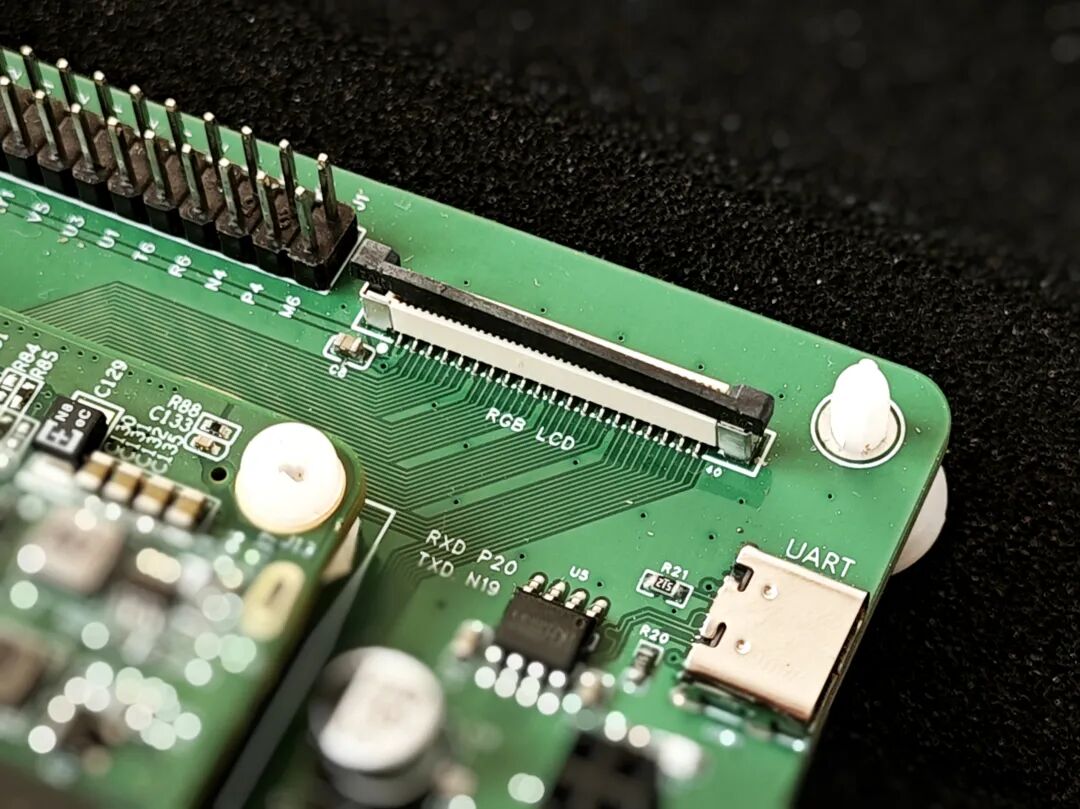

显示与图像采集是亮点:RGB LCD接口支持RGB888液晶屏;标准HDMI-A接口支持TMDS编码输出和IIC参数读取;2*9P摄像头接口可连接OV7725、OV5640等模块,实现图像采集项目。

存储与调试接口包括:标准7线SD卡座(支持SDIO/SPI驱动和插入检测);CH340N串口芯片与Type-C接口组成的调试串口。40PIN接口可对接正点原子等厂商的AD/DA模块。

1路SMA接口直连FPGA管脚,适合高速信号长距离传输。未使用信号通过2*12P标准排针引出,便于外接自定义模块。调试接口为标准10Pin JTAG,满足程序下载需求。

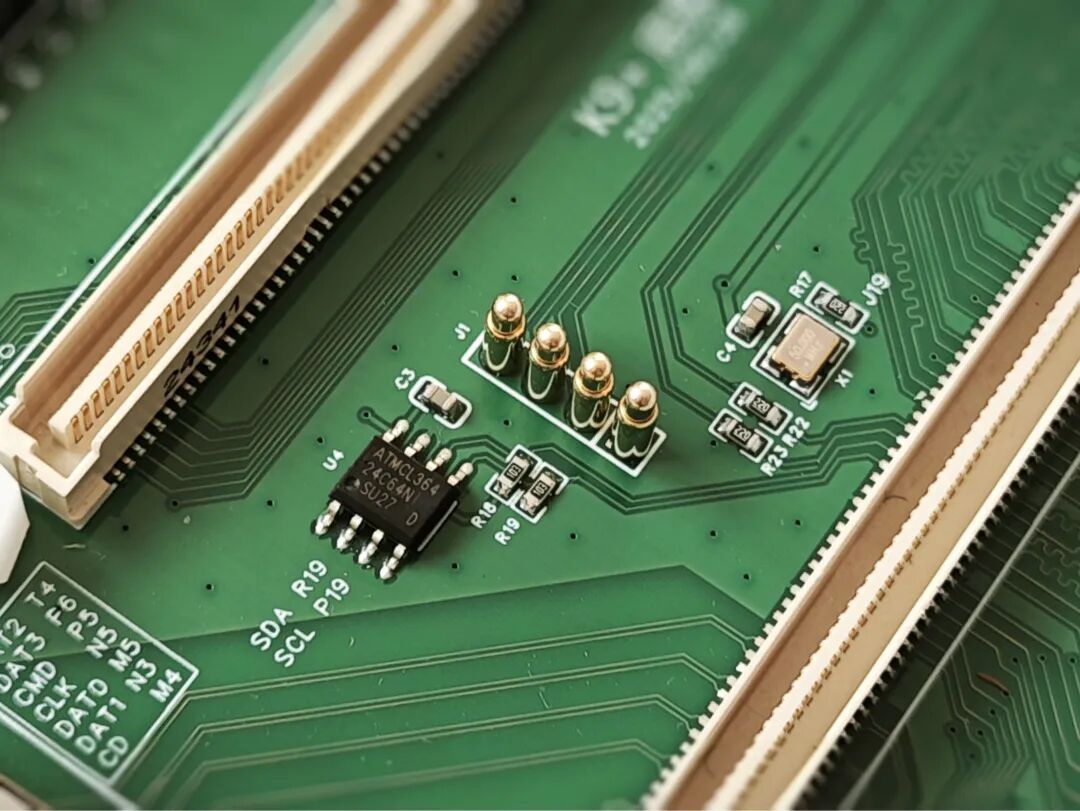

底板JTAG连接设计巧妙:核心板JTAG通过排针独立引出,底板对应位置焊接4根短弹簧顶针。扣合时顶针稳定接触导通信号,拔插时压缩结构不造成阻碍,平衡稳定性和便捷性。

配套资料

核心板源自拆机设备,故无法提供原厂原理图,但已获取完整FPGA管脚定义,满足开发调试需求。配套FPGA例程移植自正点原子、黑金等厂商,稳定性高,内容覆盖从基础到实战:包括LED点亮、按键滤波等入门实验;EPROM读写、SDRAM操作等存储控制;VGA/HDMI显示驱动;以及液晶显示摄像头图像、UDP传输图像等实战项目。

进阶部分提供MicroBlaze软核例程,支持从新手到高阶的完整学习路径,无需额外搜集资源。

总结

该开发板为FPGA学习提供完整进阶路径:入门阶段可掌握LED驱动、按键滤波、蜂鸣器控制等外设操作,以及IIC、SPI、UART通信协议实现,完成FIFO、RAM等存储单元设计;进阶阶段可开发RGB显示驱动、HDMI TMDS编码、摄像头数据采集、SDRAM读写控制等复杂应用;高阶阶段支持MicroBlaze软核开发,具备STM32经验者更易上手,可运行FreeRTOS系统,掌握GPIO、串口、定时器、中断等外设管理,以及软核与FPGA逻辑基于共享BRAM、AXI协议的通信,实现固件在线升级和MultiBoot多镜像启动。

扩展应用方面:搭配CAN收发器模块可实现CAN协议通信;支持数据压缩、图像编解码、浮点运算、SHA加密等高级实践;还可进行高等级综合(HLS)技术学习,将C语言函数转换为IP核,开发图像边缘检测等机器视觉应用。

需注意核心板搭载SDRAM而非DDR,因此软核无法运行LwIP等大型协议栈,此为硬件配置的局限。