在FPGA高性能数据采集与信号处理系统中,信号调理扮演着连接模拟世界与数字算法的关键角色。它远不止于简单的滤波,更是对信号幅度、相位、直流偏移以及频谱特性的全方位实时修整,为后续的精确分析与处理打下坚实基础。

时域基础调理:幅度与直流校正

在信号进入复杂的滤波器之前,确保其“底子”干净规整是首要任务。模拟前端电路,例如运算放大器,常常会引入不可避免的直流偏置。对于超低频或精密测量应用,这种偏置可能直接淹没微弱的有效信号。

直流偏移校正 (DC Offset Correction)

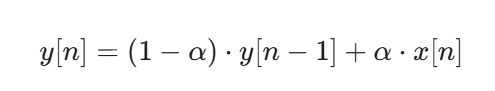

一种有效的做法是利用累加器计算一个较长时间窗口内的信号平均值,然后将该均值从当前采样值中实时减去。在FPGA实现中,为了高效且连续地提取直流分量,常采用一阶低通滤波器(IIR型),其递归公式清晰地描述了这一过程:

其中,系数 α 被设置为一个极小的值(例如 2^-16),这样得到的 y[n] 就是一个非常平滑、近似于直流偏置的估计值,便于后续校正。理解这类递归滤波器的数学原理,是深入数字信号处理的基础。

核心滤波算法:FIR vs IIR 的抉择

滤波是信号调理中最消耗资源,也最核心的环节。选择合适的滤波器类型,往往需要在性能、资源和稳定性之间做出权衡。

FIR(有限脉冲响应)滤波器

- 特点:绝对稳定,且具有严格的线性相位特性,这意味着信号通过滤波器后,波形不会产生失真,这对许多需要保持信号形状的应用至关重要。

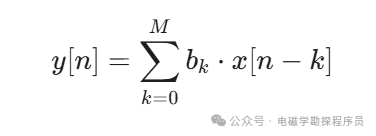

- 计算公式:FIR滤波器的输出由输入序列与滤波器系数的卷积和决定:

在FPGA中,可以利用高度并行的乘累加(MAC)单元高效实现。对于多通道时分复用(TDM)信号,还可以通过提高系统时钟频率,巧妙地复用同一套乘法器阵列来处理所有通道,从而节省宝贵的DSP资源。FIR滤波器能够保证线性相位,是其相对于IIR滤波器的一个重要优势,这在信号与系统的分析中是一个关键概念。

IIR(无限脉冲响应)滤波器

- 特点:能够以极小的阶数实现非常陡峭的频率截止特性,资源利用率高。

- 缺点:相位响应是非线性的,可能导致信号失真;并且由于存在反馈环路,在定点数实现时若设计不当,可能存在稳定性风险。

- 适用场景:非常适合那些对硬件资源要求极其苛刻,且对相位失真不敏感的快速滤波应用。

高级调理技术:多速率与频谱变换

当基础调理不能满足需求时,更高级的算法便登场了。

A. CIC(级联积分梳状)滤波器

它专为大幅度降采样(抽取)而设计。通过“积分、抽取、梳状”三个步骤,CIC滤波器完全避免了乘法器的使用,非常适合在FPGA中高效实现。但需要注意处理好其固有的数学特性,如溢出卷绕(Wrap-around)问题。

B. 希尔伯特变换 (Hilbert Transform)

该变换能够将一个实信号转换为解析的复信号(即IQ信号),实质上生成一个90°的相移版本。这在通信和雷达系统中极为有用,可用于计算信号的瞬时包络(振幅)和瞬时相位。

C. CORDIC 算法

这是一种通过迭代的旋转和移位操作来计算三角函数(如正余弦)、模值及角度的算法,其最大优点是不需要使用硬件乘法器。在信号调理中,CORDIC可用于实时计算信号的相位偏移,常应用于多通道信号的相位同步与校准。

面向多通道(TDM)的调理架构设计

在处理多通道数据时,FPGA的调理架构应遵循“逻辑复用,状态分离”的原则。

- 逻辑复用:只需设计一套FIR、IIR或校正逻辑电路,让其运行在较高的时钟频率(如50MHz或更高),然后以时分复用的方式依次处理各个通道的数据。

- 状态分离:为每一个通道分配独立的存储空间(如Block RAM),用于保存其专属的历史状态数据,例如滤波器延迟链中的

x[n-1], x[n-2] 等。这确保了通道间数据的完全隔离。

- 流水线化:在乘法器和加法器之间插入寄存器,形成流水线结构。这种“寄存器树”的设计能够有效提高系统最高工作频率,确保在处理高频信号时时序能够顺利收敛。

善用开发工具与IP核

现代FPGA开发环境提供了强大的工具链,可以大幅提升开发效率:

- FIR Compiler IP核:支持多通道TDM输入,能够根据设定的滤波器参数自动优化DSP资源的利用,是实现高性能FIR滤波器的利器。

- Complex Multiplier IP核:专门用于处理复数乘法,在进行信号的希尔伯特变换、正交上/下变频等操作时非常高效。

- 实时监控 (ILA):充分利用Vivado等工具中的集成逻辑分析仪,在线观察信号调理前后的波形对比。你会清晰地看到,经过精心调理后,原本杂乱无章的原始ADC数据,是如何转变为平滑、稳定的高质量信号,这是调试和验证过程中不可或缺的一环。想了解更多硬件描述语言与调试技巧,可以到技术社区云栈社区与同行交流。

|