目前市面上的SSD大多使用TLC或QLC 3D NAND闪存。其实,关于在每个存储单元中存储5比特数据的五级单元(PLC)3D NAND闪存,制造商们早已开始探索。SK海力士的子公司Solidigm就曾在2022年展示了全球首款PLC SSD的原型,并计划率先将其应用于数据中心领域。

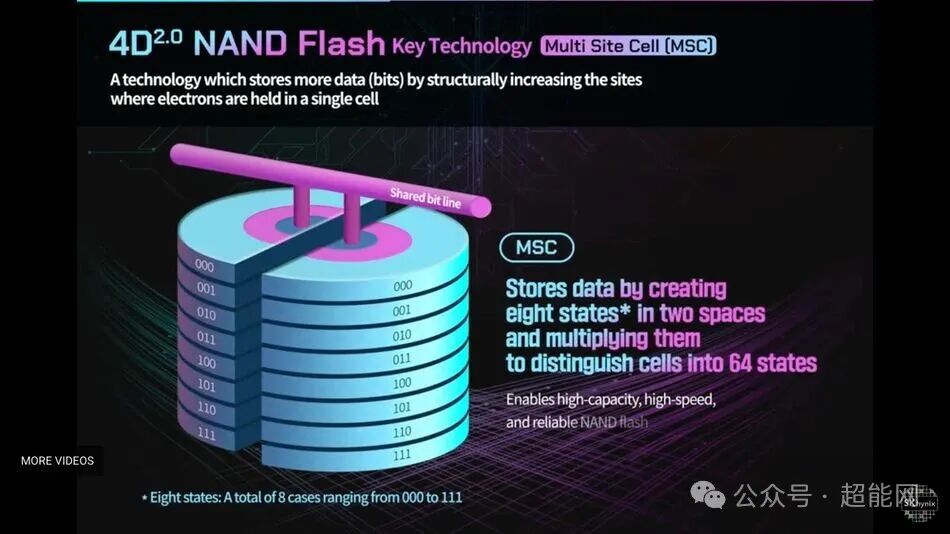

据外媒报道,SK海力士在上个月举行的2025年IEDM会议上,展示了其最新的PLC NAND闪存技术。该技术声称其读取速度可达传统PLC NAND闪存的20倍。此次,SK海力士重点介绍了其用于PLC NAND闪存的 多站点单元(Multi-Site Cell)技术,即所谓的 “4D².0”技术。其核心设计理念是绕开单纯增加单元电压状态的屏障,从而规避了在NAND闪存单元中直接实现超过4比特数据存储所带来的诸多挑战。

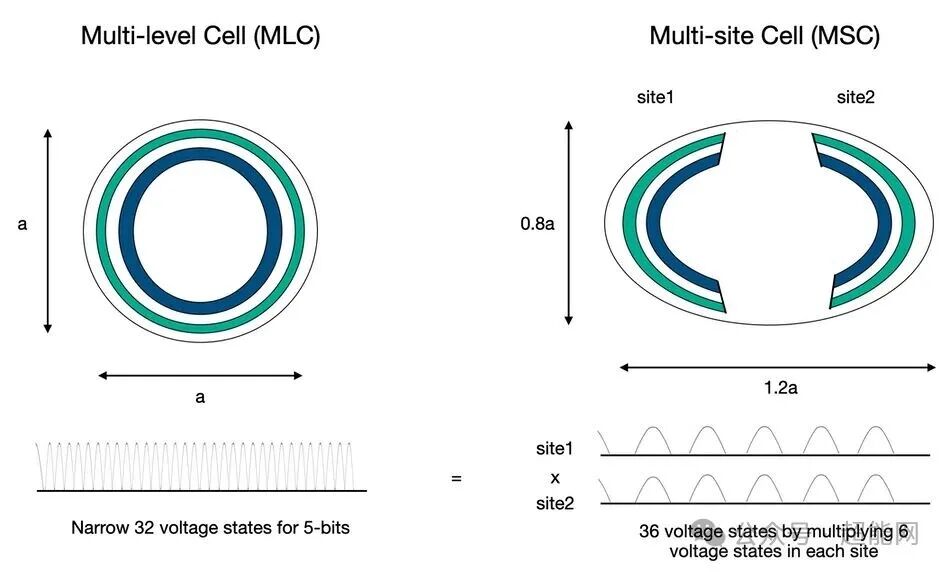

与QLC NAND闪存相比,PLC将每个存储单元存储的数据从4比特提升至5比特,电压状态也从2的4次方(16种)大幅增加至2的5次方(32种),从而获得了25%的容量提升。然而,PLC SSD的实现不仅需要更先进的NAND闪存颗粒,还依赖性能更强大的SSD主控以及更复杂的纠错算法,以解决其读取可靠性低、使用寿命短的核心难题。这也正是PLC SSD至今尚未成功实现大规模商业化的主要原因之一。

SK海力士的 Multi-Site Cell(MSC)技术 提供了一种创新思路。该技术将传统的3D NAND闪存单元在物理结构上“一分为二”,形成两个相对独立的存储区域。每个区域只需管理较少的电压状态,最后将两个区域的值组合起来,从而达到存储4比特以上数据的总目标。这种 分体式设计 不仅提高了存储的位密度,更关键的是,它将实现5比特存储所需的电压状态总数减少了约三分之二,同时显著提升了数据的读写速度和闪存单元的耐用性。这背后的原理,实则与计算机体系结构中对复杂问题进行 模块化分解 以优化整体性能的思路有异曲同工之妙。 |