在开源硬件领域,一个既有芯片级代码又能投入实际工程的项目实属难得。Baochip-1x 正是这样一个典型案例:它是一个围绕 RISC-V 架构,并以几乎完全开源的逻辑描述代码为核心的微控制器项目。该项目的代码托管于 GitHub,提供了关键的 RTL(寄存器传输级)源码,支持自动化文档生成与功能仿真,为深入学习和开发提供了宝贵的资源。

项目的核心是基于台积电 22nm 工艺制造的 350MHz 主频单片机,并提供了完整的流片级 RTL 文件。

项目简介

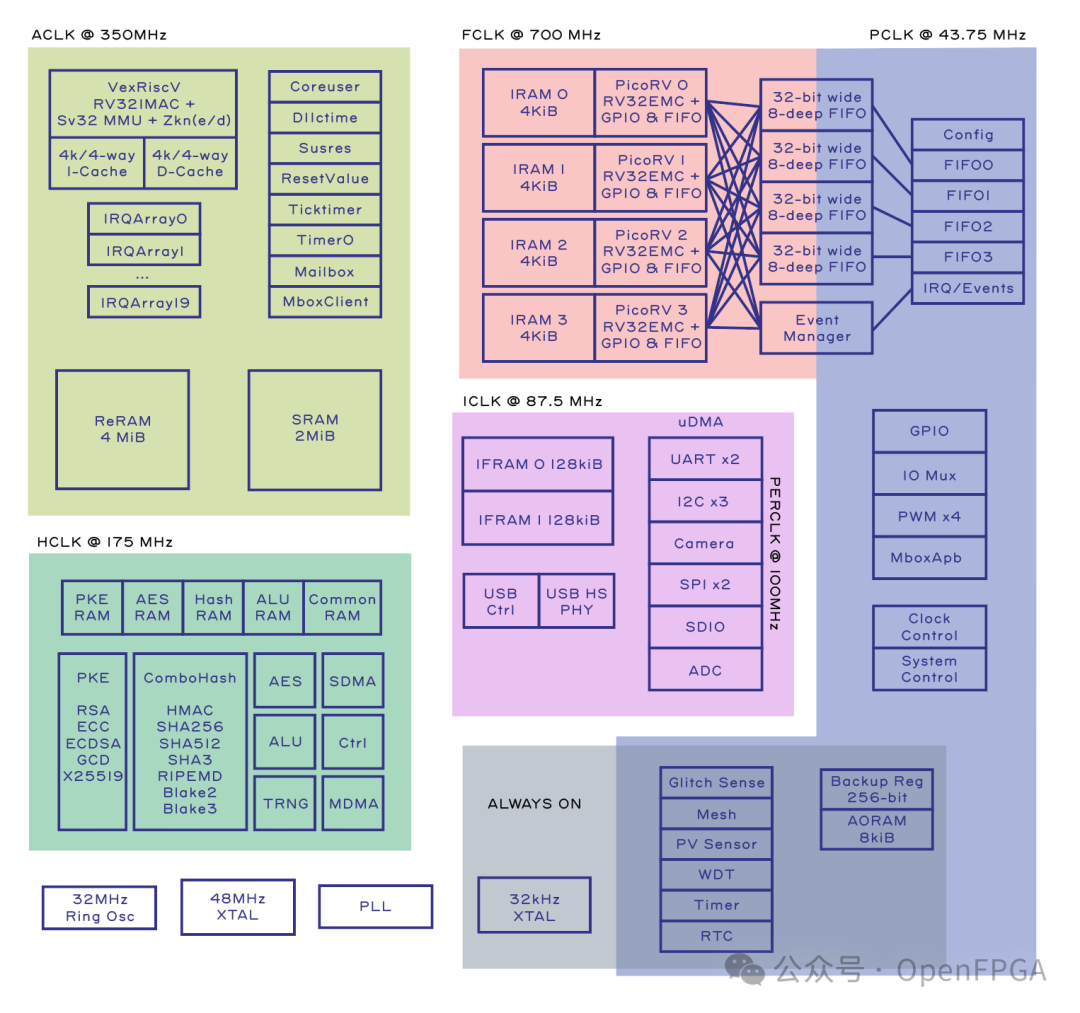

Baochip-1x 是一颗以开源 RTL 代码为主体、基于 RISC-V 指令集架构的微控制器芯片。它采用台积电 22 纳米工艺制造,搭载主频 350MHz 的 VexRiscv 内核,集成了 2MB SRAM、4MB ReRAM Flash、USB 2.0 高速接口,以及四个基于 PicoRV32 设计、主频高达 700MHz 的 I/O 加速核心。

RTL 是对数字硬件逻辑的结构化描述,可用于综合、仿真与验证,并能提取生成相关文档。该项目提供的 RTL 代码足以支撑自动化文档生成与功能级仿真,是学习和研究 SoC 设计的优秀范例。对于想深入了解 计算机基础 中数字逻辑与系统架构的开发者来说,这是一个绝佳的实践材料。

代码组织

项目的代码库结构清晰,主要包含以下几个部分:

核心特性

1. 主要由开源架构构成

项目源代码主要构建于开源技术栈之上,包括 Verilog / SystemVerilog 代码,以及借助 SpinalHDL 与 Litex 生成的代码片段。尽管部分组件因工程与 IP 原因未完全开源,但现有代码已能完整勾勒出 SoC 的主要骨架,足以用于建立技术文档和执行功能验证。

2. 文档与自动生成机制

项目内置了自动化工具链,能够直接从 RTL 代码中提取以下关键信息:

- SoC 外设的部分 SVD(系统视图描述)文件

- 供 Xous 核心代码使用的头文件

- 可读性强的 SoC 结构说明文档

这些内容均由脚本自动生成,极大地方便了开发者理解芯片设计与进行上层软件开发。

3. 支持 Verilator 仿真

为了便于软件开发和前期验证,项目支持使用开源的 Verilog 模拟器 Verilator 进行功能仿真。相比商业工具,Verilator 执行速度更快,非常适合软件调试与大规模的持续集成测试。

通过 Verilator 仿真,你可以实现:

- 启动并运行如 Xous 这样的操作系统

- 查看 SoC 内部信号的波形变化

- 调试程序计数器、寄存器文件、AXI 总线状态等

- 结合 GTKwave 与 Codezoom 工具,在仿真波形图中定位特定指令与硬件状态

虽然这种仿真不处理精确的时序细节和未知逻辑状态,但它在软件验证与开发流程中具有极高的实用价值。探索这类 开源实战 项目,能让你更直观地理解从硬件描述到软件运行的完整链条。

硬件验证

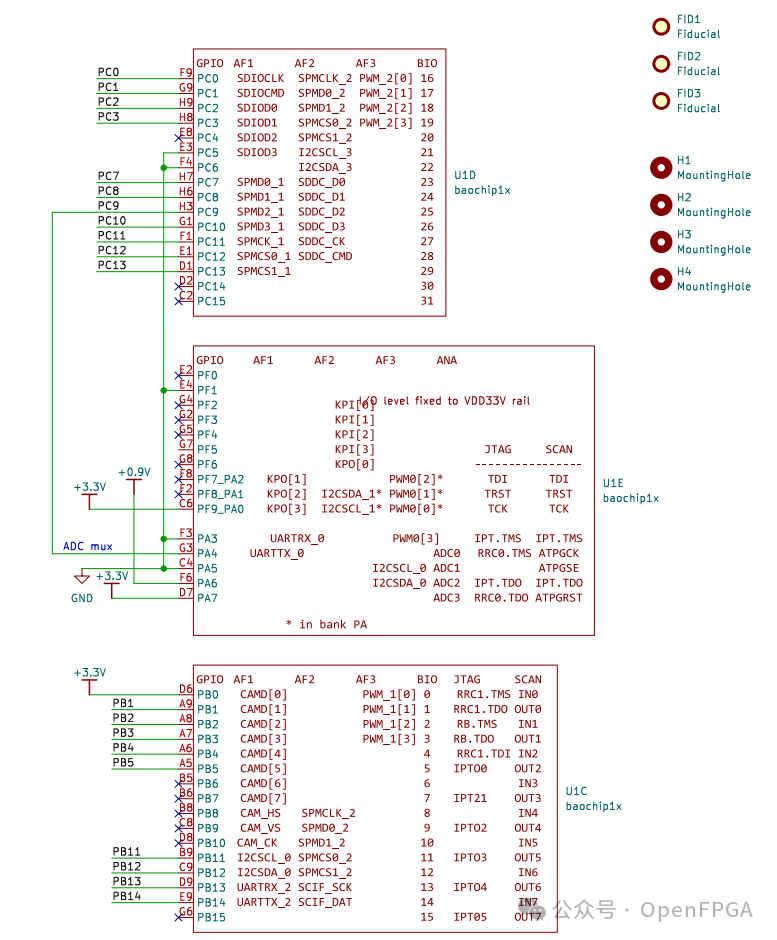

项目配备了专门设计的开发板(代号“dabao”)用于硬件验证与开发。

开发板相关资源:https://github.com/baochip/dabao

总结

Baochip-1x 是一个围绕 RISC-V 架构打造的开源 MCU 项目资源库,它提供了 RTL 描述、自动化文档生成工具以及仿真支持。尽管部分模块暂未开源,但现有资源已足够用于:

- ✔ 学习数字 SoC 的架构设计与模块组织方式

- ✔ 在 Verilator 仿真环境中进行功能验证与软件开发

- ✔ 实现技术文档与驱动头文件的自动提取生成

- ✔ 为后续开发板设计与软件生态构建提供基础

作为连接开源硬件与嵌入式软件世界的桥梁,该项目为所有关注 RISC-V 与开源硅生态的研究者和工程师提供了一个极具参考价值的实践平台。如果你想与更多开发者交流此类前沿技术,欢迎来到 云栈社区 参与讨论。 |