学习STM32单片机,尤其是经典的F103系列,掌握其核心架构与配置要点是深入开发的基础。本文整理了50条关键学习笔记,涵盖时钟、GPIO、中断、定时器、PWM、FLASH操作等核心主题,旨在帮助开发者快速构建知识体系,避开常见误区。

一、 时钟与总线架构

- AHB系统总线分为APB1(最高36MHz)和APB2(最高72MHz)。数字2>1表示APB2连接的是高速外设。

- 头文件

stm32f10x.h类似于51单片机中的reg52.h,包含了基本的位操作和寄存器定义;而stm32f10x_conf.h则用于集中管理外围器件的头文件包含,起到配置开关的作用。

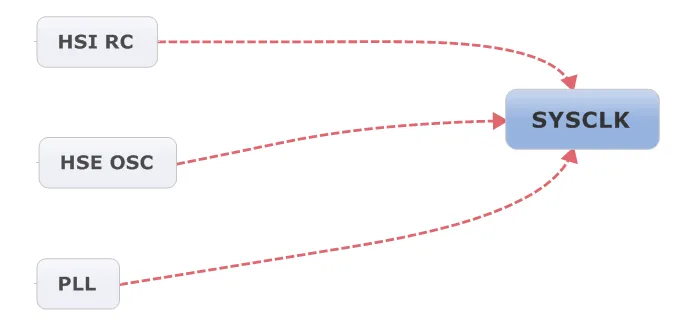

- HSE Osc (High Speed External Oscillator) 指高速外部晶振,通常接8MHz。HSI RC (High Speed Internal RC) 指高速内部RC振荡器,频率约为8MHz。

- LSE Osc (Low Speed External Oscillator) 指低速外部晶振,通常为32.768KHz,用于RTC。LSI RC (Low Speed Internal RC) 指低速内部RC振荡器,频率约40KHz,为独立看门狗和自动唤醒单元提供时钟源。

- SYSCLK(系统时钟)的来源有三个:HSI RC、HSE OSC和PLL(锁相环输出)。

- MCO[2:0] 引脚(PA8)可以输出4种不同的时钟信号,用于同步或测试。

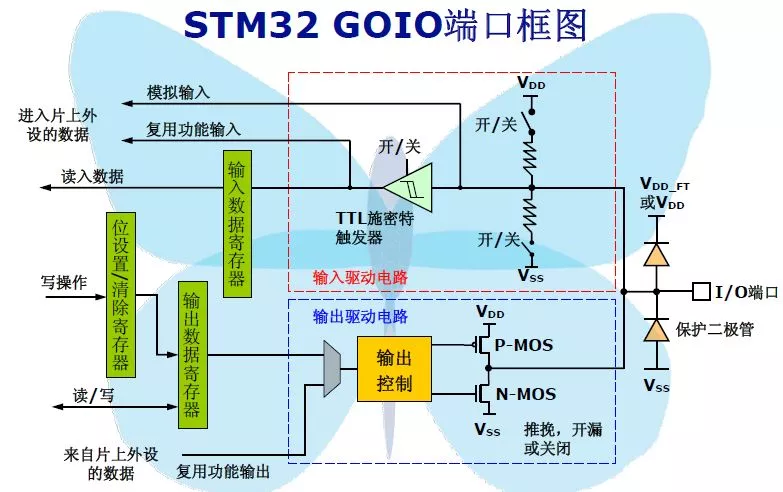

- GPIO内部通常集成两个反向串联的二极管,连接到VDD和VSS,起到钳位保护作用,防止引脚电压过高或过低。

- 总线矩阵采用轮询算法,对系统总线和DMA访问进行仲裁。

- 主要总线包括:ICode总线(取指令)、DCode总线(取数据)、系统总线、DMA总线、总线矩阵以及AHB到APB的桥接。

- 关键步骤:在使用任何外设前,必须通过设置

RCC_AHBENR或RCC_APBxENR寄存器来开启该外设的时钟。

- STM32采用小端模式存储数据。

- 内存地址映射空间被划分为8个块,每块大小为512MB。

- FLASH页的大小:小容量和中容量产品为1KB,大容量产品为2KB。

- “系统存储区”(System Memory)由ST公司固化,用户无法修改,其中存放了Bootloader程序,用于通过串口等方式对主存储区(用户程序区)进行重新编程。因此,烧录程序时通常需设置BOOT1=0,通过内置的引导程序来更新FLASH中的中断向量表和代码。

- STM32F1系列内核(Cortex-M3)的工作电压(Vcore)为1.8V。

二、 复位、GPIO与中断系统

- STM32有三种复位:系统复位、电源复位和备份域复位。

- 系统复位:除RCC_CSR中的复位标志和备份寄存器(BKP)外,所有寄存器均复位。可由外部复位引脚、看门狗、软件触发等引起。

- 电源复位:由电源上电/掉电或从待机模式返回引发。除BKP外,所有寄存器复位。

- 备份域复位:仅复位备份区域寄存器,由软件或VDD/VBAT均掉电触发。

- 单片机复位后,所有I/O端口默认处于浮空输入模式,这是为了降低功耗和防止意外损坏。

- 中断资源:STM32F103系列有60个可屏蔽中断通道,STM32F107等互联型有68个。所有型号均有16个可编程优先级和16个内核中断。

- 系统启动后,从地址

0x00000004(存储初始堆栈指针)开始执行代码,0x00000000地址保留。

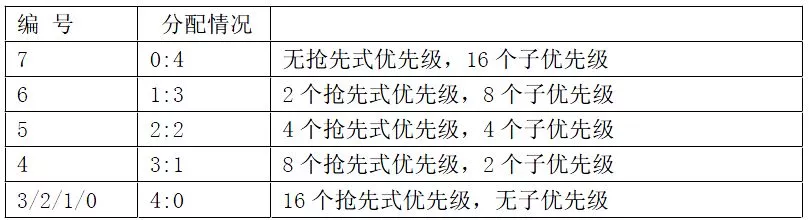

- NVIC (嵌套向量中断控制器) 管理中断优先级,分为抢占优先级(可嵌套)和子优先级(响应优先级,不可嵌套)。优先级由4位二进制位配置,共有5种分配方案。

- 中断嵌套规则:高抢占优先级中断可打断低抢占优先级中断。若抢占优先级相同,则比较子优先级,子优先级高的先响应。若两者都相同,则比较硬件中断向量号,编号小的优先。

- 上电后,默认使用16级抢占优先级(无子优先级)。但所有外部中断的优先级控制字初始为0,因此抢占优先级相同,无法嵌套,需要手动配置分组。

- NVIC寄存器组包括:ISER/ICER(中断使能/除能)、ISPR/ICPR(中断挂起/解挂)、IABR(中断活动状态)、IPR(中断优先级)。写1操作使能或清除,这种设计基于硬件实现效率考量。

- 重要:大部分中断标志位需要在中断服务函数内手动清除,否则会导致中断持续触发。

- 配置外设的通用步骤:1. 使能外设时钟;2. 定义并初始化配置结构体;3. 调用初始化函数。

三、 常用外设要点

- 串口奇偶校验:若启用奇偶校验,则

USART_InitStructure.USART_WordLength 必须设置为 USART_WordLength_9b(9位数据长度),因为校验位会占用1位。

- ADC的规则组可自定义转换顺序和通道数。注入组具有更高优先级,可在规则组转换时强行插入,适用于需要紧急采样的信号。

- 定时器输出比较模式:

- Timing:冻结,输出不变。

- Active:匹配时输出有效电平(高)。

- Inactive:匹配时输出无效电平(低)。

- Toggle:匹配时电平翻转。

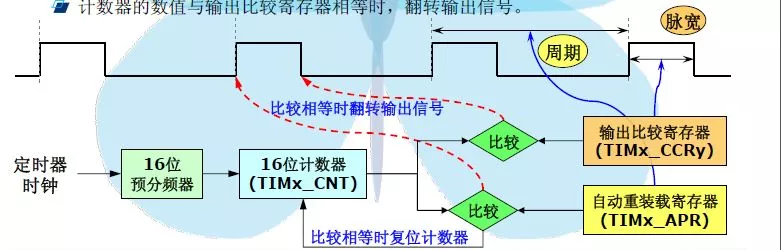

- STM32的定时器从0开始向上计数,到达设定条件(如匹配、溢出)后产生标志位,然后从0重新开始计数。这与51单片机不同。

- 最终输出信号

OCx = OCxREF + 极性控制。极性控制决定了有效电平是高还是低。

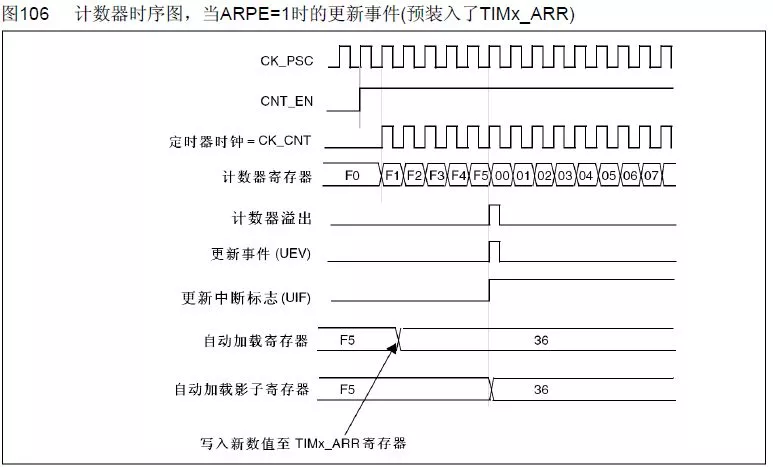

- 自动重装载寄存器 (ARR) 和影子寄存器:程序员操作的是ARR。影子寄存器是真正控制计数的“幕后”寄存器。当

ARPE(自动重装载预装载使能)位为1时,写入ARR的新值要到下一次更新事件时才更新到影子寄存器,否则立即更新。

RCC_PCLK1Config(RCC_HCLK_Div4) 表示将APB1时钟(PCLK1)进行4分频,作为其下挂载的定时器基准时钟源之一。- 配置定时器(如PWM输出)的一般流程:配置RCC时钟、NVIC中断(如需)、GPIO(复用为输出)、TIMx定时器本身。

- PWM输出能力:一个通用定时器可输出4路PWM;一个高级定时器可输出4路普通PWM外加3路带死区互补的PWM(用于驱动三相电机),共7路。理论上,一个芯片的定时器资源可产生多达30路PWM。

- 定时器PWM生成原理框图:

- 时钟路径:高级定时器时钟在APB2上,通用定时器在APB1上。APB1默认2分频(36MHz),但给定时器时会有一个x2的倍频器,因此通用定时器时钟可达72MHz。若APB1未分频,则定时器时钟直接等于APB1时钟。

TIM_SetAutoreload() 用于改变PWM频率,TIM_SetCompare1() 用于改变通道1的占空比。

- 电机驱动对比:有刷电机启动力矩大;无刷电机运行力矩大,通过霍尔传感器检测转子位置进行电子换向。

- 死区时间在驱动桥式电路(如三相逆变)中必不可少,用于防止上下桥臂直通短路,确保开关管有足够时间彻底关断。

- 高级定时器的刹车功能可在故障时硬件自动强制PWM输出为安全状态(固定占空比或固定电平),实现紧急制动。

- 生成精确、稳定的PWM信号,推荐使用专门的 PWM模式,其他比较输出模式可能存在相位偏移。

- 对内部FLASH进行编程(写)操作前,必须先解锁,操作完成后需再加锁。FLASH特性是“写0易,写1难”,只能将1写成0,擦除操作是将整页恢复为1。

- 程序下载方式:

- ICP (在线编程):通过JTAG/SWD接口直接烧写,用于开发阶段。

- IAP (在应用编程):通过芯片上的接口(如USART、USB、CAN)接收数据并更新自身FLASH,用于产品固件升级。

- FLASH构成:主存储器(存放用户代码)、信息块(包含启动配置)、系统存储器(存放出厂Bootloader,不可修改)。

- 注意:在对FLASH执行写或擦除操作时,不能同时进行读操作,否则会锁住总线导致操作失败或系统挂起。

- 对FLASH进行操作时,必须保证 HIS(高速内部RC振荡器) 或HSE已经开启并稳定。

- 看门狗类型:

- IWDG (独立看门狗):基于独立的LSI时钟,即使主时钟失效也能工作。

- WWDG (窗口看门狗):时钟来源于APB1,需要在特定时间窗口内刷新。

- SPI接口的最高理论通信频率为

fpclk/2,当APB1时钟为36MHz时,SPI最高速率为18MHz;APB2时钟为72MHz时,挂载其上的SPI可达36MHz。

- 高级定时器(TIM1/TIM8)输出PWM时,需额外使能 主输出 (

TIM_CtrlPWMOutputs(ENABLE)),通用定时器无此要求。TIM6和TIM7是基本定时器,无PWM输出功能。

四、 内存管理与总结

- 程序编译后的内存分布:

- Code:程序代码。

- RO-data:只读常量(const变量)。

- RW-data:已初始化的全局变量和静态变量。

- ZI-data:未初始化的或初始化为0的全局/静态变量。

- Code和RO-data、RW-data的初始值存放在FLASH中。

- RW-data(运行时)和ZI-data存放在RAM中。

- 启动时,RW-data的初始值从FLASH拷贝到RAM。

- 以STM32F103ZET6为例,“Z”代表144引脚封装,其中可用GPIO引脚为112个(即PA、PB、PC、PD、PE、PF、PG口,每组16个,共7组)。

掌握以上50个要点,能帮助开发者更深入地理解STM32的计算机基础与操作系统底层机制,为编写高效、稳定的嵌入式系统程序打下坚实基础。这些笔记整理自实践与官方资料,欢迎在云栈社区交流探讨更多技术细节。 |