STM32的GPIO介绍

GPIO,即通用输入/输出端口,是STM32微控制器上可由软件直接控制的物理引脚。这些引脚是与外部世界交互的桥梁,开发者通过它们可以实现与外部设备的通信、控制执行器,或者采集传感器数据。

以STM32F103ZET6这款144引脚芯片为例,它包含了7组通用输入/输出端口,分别是GPIOA到GPIOG。每组端口拥有16个引脚,通常简写为PAx、PBx、PCx等,其中x的取值范围是0到15。

除了基本的GPIO功能,STM32的大部分引脚还具有复用功能,可以配置为串口、I2C、SPI等片上外设的专用引脚,这部分功能涉及端口复用与重映射机制。

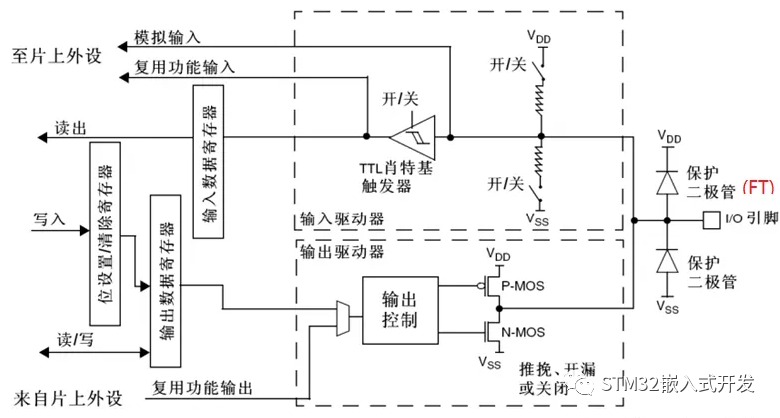

GPIO基本结构

每一个GPIO内部都有一套精心设计的电路结构,这套结构决定了引脚的行为模式。理解它是掌握GPIO工作原理的关键。

电路图分析

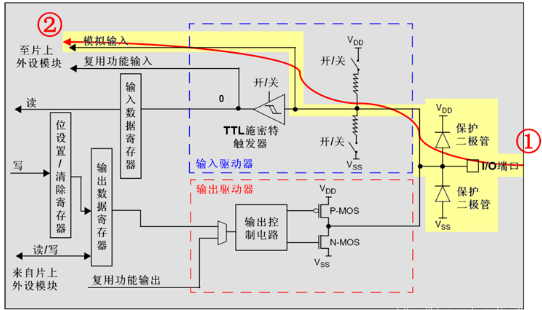

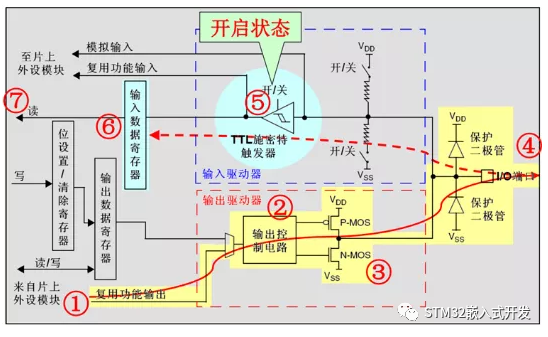

上图清晰地展示了一个标准GPIO口的内部架构,主要包含以下几个核心部分:

- 保护二极管:引脚两侧的二极管构成了电压钳位保护电路。当引脚上的电压高于供电电压

VDD时,上方的二极管导通;当电压低于地VSS时,下方的二极管导通。这能有效防止异常高压或低压涌入芯片内部,造成永久损坏。但请注意,这并不意味着可以直接驱动大功率负载,驱动此类设备仍需外加功率放大或隔离电路。

- P-MOS管和N-MOS管:这对互补的MOSFET(金属-氧化物半导体场效应晶体管)是输出级的核心。它们的协同工作方式,直接决定了GPIO是处于“推挽输出”还是“开漏输出”模式。

- TTL肖特基触发器:这是一个信号整形电路。输入的数字信号经过它之后,会被转换为标准的0(低电平)或1(高电平)数字信号。不过,当GPIO被用作模拟输入(例如ADC采集通道)时,模拟信号会绕过这个触发器,直接送入相关外设模块,以保持信号的原始模拟特性。

一个重要的细节:在查阅《STM32中文参考手册》的GPIO引脚定义表时,你会看到“FT”标志。这代表该引脚兼容5V电平(即可以耐受5V输入);没有此标志的引脚则只能兼容3.3V电平。

STM32的GPIO工作方式

STM32的GPIO功能非常灵活,支持4种输入模式和4种输出模式,并且每种输出模式都可以配置三种不同的最大信号翻转速度(2MHz, 10MHz, 50MHz)。所有I/O口均可自由编程,但需要注意,对GPIO寄存器的操作必须以32位字(4字节)为单位进行。

GPIO的八种工作方式详解

输入模式

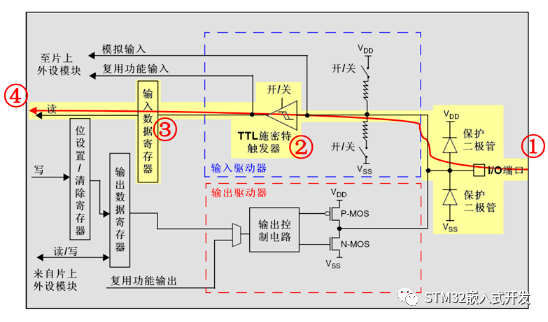

输入模式下,信号从外部引脚流入芯片内部。根据内部是否连接上拉/下拉电阻,或是否接入模拟通道,分为以下四种:

-

浮空输入 (GPIO_Mode_IN_FLOATING)

在此模式下,I/O端口的电平直接进入输入数据寄存器。引脚内部既不上拉也不下拉,处于高阻态。因此,当外部没有驱动信号(引脚悬空)时,读取到的电平值是不确定的。这种模式常用于外部接有确定驱动电路(如按键配合外部上拉电阻)的场合。

-

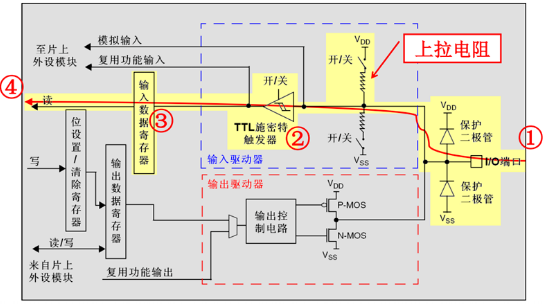

上拉输入 (GPIO_Mode_IPU)

与浮空输入类似,但内部通过一个电阻连接到VDD(高电平)。当外部无信号输入(悬空)时,内部电路会将该引脚的电平保持在高电平;只有当外部施加一个足够强的低电平时,才能将引脚拉低。这避免了悬空状态下的电平不确定性。

-

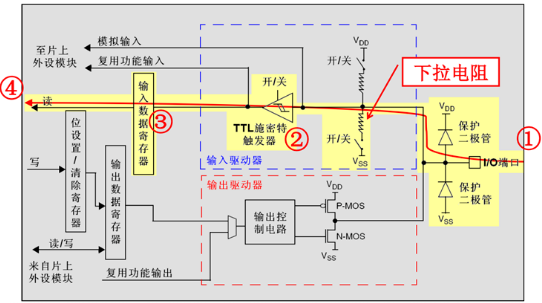

下拉输入 (GPIO_Mode_IPD)

与上拉输入相反,内部通过一个电阻连接到VSS(地,低电平)。悬空时引脚保持低电平;只有外部施加高电平时才能将其拉高。

-

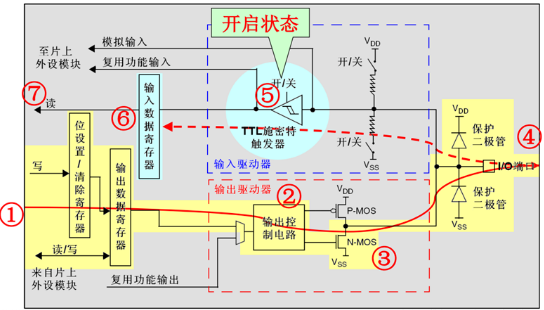

模拟输入 (GPIO_Mode_AIN)

此模式下,GPIO的模拟输入功能被启用,信号直接通往ADC(模数转换器)等模拟外设。数字信号路径(包括施密特触发器)被完全断开,以确保采集到的是纯净的模拟电压信号。这也是低功耗模式下推荐的状态,可以降低功耗。

输出模式

输出模式下,信号从芯片内部流向外部引脚。根据输出级结构的不同,分为开漏和推挽;根据信号来源是CPU直接控制还是片上外设,又分为通用输出和复用输出。

-

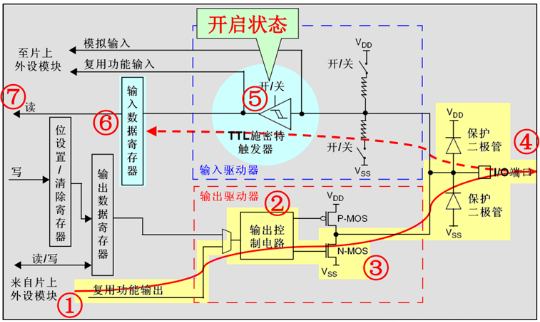

开漏输出 (GPIO_Mode_Out_OD)

在此模式下,输出级只有N-MOS管工作。当CPU向输出寄存器写入“1”时,N-MOS管关闭,此时引脚电平由外部电路决定(通常需要外接一个上拉电阻才能输出高电平);写入“0”时,N-MOS管导通,将引脚强力拉低至VSS。开漏输出的特点是可以实现“线与”逻辑,并方便进行电平转换。引脚状态依然可以被读取,但读回的不一定是CPU输出的值,而是引脚上的实际电平。

-

开漏复用输出 (GPIO_Mode_AF_OD)

此模式与开漏输出模式在电路结构上完全相同,唯一的区别是输出信号的来源。它不是来自CPU对GPIO输出数据寄存器的写操作,而是直接来自片上的复用功能外设模块(如I2C的SDA线)。

-

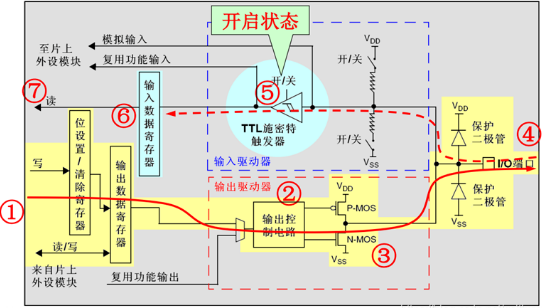

推挽输出 (GPIO_Mode_Out_PP)

这是最常用的输出模式。输出级由P-MOS和N-MOS管共同组成推挽结构。当输出“1”时,P-MOS导通,N-MOS截止,引脚被拉至高电平(VDD);当输出“0”时,P-MOS截止,N-MOS导通,引脚被拉至低电平(VSS)。这种结构使得引脚既能主动输出高电平,也能主动输出低电平,驱动能力强。读回的电平就是当前输出的电平。

-

推挽复用输出 (GPIO_Mode_AF_PP)

与开漏复用输出类似,其电路结构与推挽输出一致,但输出信号源是片上外设的复用功能输出(如USART的TX引脚)。

深入理解:推挽与开漏

什么是推挽结构?

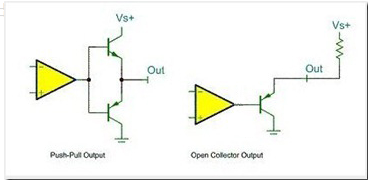

推挽结构利用两个参数对称的三极管或MOS管,受一对互补信号控制,始终保证一个导通时另一个截止。在STM32的GPIO语境下,推挽输出意味着输出级能够独立且有力地驱动引脚到高电平或低电平,其电平由输出寄存器决定。

这种结构的优点是驱动能力强、开关速度快、波形完整性好。它既可以向负载“灌入”电流(输出低电平时,电流从负载流入引脚),也可以从负载“拉出”电流(输出高电平时,电流从引脚流向负载)。

开漏输出和推挽输出的核心区别?

两者的根本区别在于输出高电平的能力:

- 开漏输出:只能强力输出低电平。输出高电平时,内部电路实际是断开(高阻)状态,需要依赖外部上拉电阻将电压拉高。这种模式便于实现总线“线与”、电平转换,但高电平驱动能力弱。

- 推挽输出:可以独立且强力地输出高电平和低电平,无需外部辅助电路。这是连接常规数字器件的标准方式。

一个简单的类比可以帮你理解这两种结构:

左图展示了推挽输出的思想:比较器输出高则上管导通输出VCC,输出低则下管导通输出GND。右图则类似于开漏输出:只有下方的晶体管工作,需要外接上拉电阻至VCC才能获得高电平。

模式速查与应用场景

为了帮助你快速选型,下图总结了八种模式及其典型应用场景:

掌握GPIO的不同工作模式,是进行精准嵌入式系统控制的基础。无论是简单的点亮LED(推挽输出),还是实现I2C总线通信(复用开漏输出),正确的模式选择都至关重要。这背后涉及对计算机基础中数字电路和信号的理解。在实际的STM32项目开发中,灵活运用这些模式,将让你能更好地驾驭这颗强大的微控制器。 |