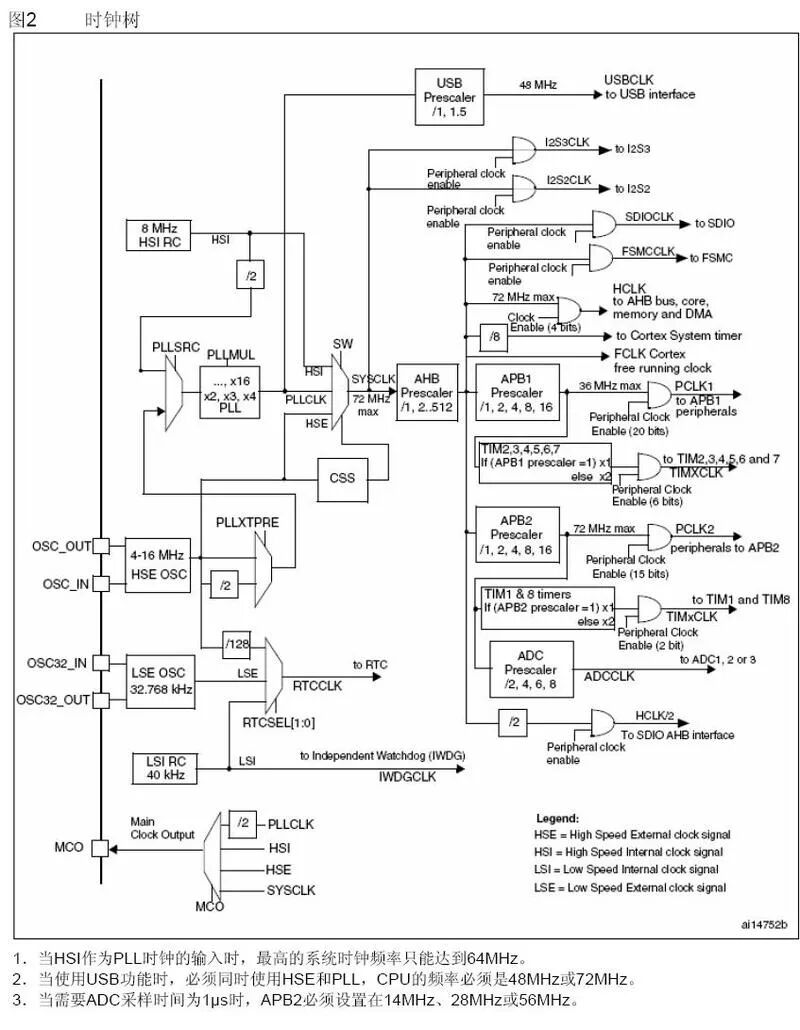

时钟信号好比是单片机的脉搏,深入理解其时钟系统,是进行稳定开发与性能优化的基础。下图展示了STM32F1xx系列经典的时钟树架构。

在STM32F1xx中,系统主要依赖五个时钟源来驱动:

- HSI:高速内部时钟,基于RC振荡器,频率固定为8MHz。

- HSE:高速外部时钟,可连接石英晶振、陶瓷谐振器或外部时钟源,频率范围通常为4MHz~16MHz。

- LSI:低速内部时钟,RC振荡器,频率约为40kHz,常用于独立看门狗。

- LSE:低速外部时钟,通常连接32.768kHz的石英晶振,为实时时钟(RTC)提供精准时基。

- PLL:锁相环倍频器,用于提升时钟频率,其最大输出频率不得超过72MHz。

SYSCLK(系统时钟)

系统时钟SYSCLK是整个芯片绝大部分功能模块的核心时钟源,其最大工作频率为72MHz。它可以由PLL、HSI或HSE直接提供。之后,SYSCLK会经过AHB总线预分频器进行分频,再分配给各个外设模块使用。

HCLK(AHB总线时钟)

HCLK直接为高性能的AHB(Advanced High-performance Bus)总线及其连接的外设提供时钟信号。它由SYSCLK分频得到,在默认不分频的情况下,HCLK的频率就等于SYSCLK。

FCLK(内核自由运行时钟)

FCLK(Free Running Clock)是一个独立运行、专为Cortex-M3内核提供的时钟。我们常说的CPU主频(xx MHz),指的就是FCLK的频率,而一个CPU时钟周期就是1/FCLK。

“自由运行”的特性意味着FCLK不依赖于系统时钟HCLK。即使在HCLK因低功耗模式而停止时,FCLK仍可能继续运行。FCLK主要用于采样中断或为调试模块计时。当处理器进入休眠状态时,正是通过FCLK来捕捉中断信号和跟踪休眠事件,从而实现快速响应。在Cortex-M3架构中,FCLK与HCLK保持着同步与平衡,以确保内核操作的延迟一致性。

PCLK(APB外设总线时钟)

PCLK为APB(Advanced Peripheral Bus)总线上的外设提供时钟。APB总线通常分为两条:APB1和APB2,它们可以拥有各自独立的预分频器(PCLK1和PCLK2)。APB2总线通常连接着一些高速外设,其最高时钟频率高于APB1总线。

理解这些时钟之间的关系,尤其是CPU主频与各总线时钟的配置,是进行外设驱动开发、功耗管理和系统性能调优的关键第一步。想深入探讨更多嵌入式底层原理,可以到云栈社区的技术板块交流学习。 |