多年来,ASML几乎就是极紫外光刻(EUV)的代名词——正是这项精密复杂的工艺,成就了当今最先进的芯片。

但随着人工智能浪潮将半导体产业推向物理与成本的新极限,这家荷兰巨头正在思考如何跳出传统光刻的边界,拓展自己的业务版图。

未来AI硬件的突破,或许不再仅仅依赖于刻蚀出更小的晶体管,更取决于对芯片制造、封装乃至扩展方式的根本性重构。

ASML的下一步计划清晰而雄心勃勃:打造先进的芯片封装设备,并探索制造更大尺寸芯片裸片(大芯粒)的可能性。这意味着,它将从一个全球唯一的EUV供应商,向AI时代更全面的半导体制造设备提供商转型。2025年10月,马尔科·皮特斯(Marco Pieters)接替任职40年的马丁·范登布林克出任首席技术官,他强调这是一项着眼长远的战略布局,而非短期调整。

他在接受路透社采访时称:“我们不只看未来5年,而是着眼未来10年、甚至15年。”

突破瓶颈:EUV的局限与3D封装的新机遇

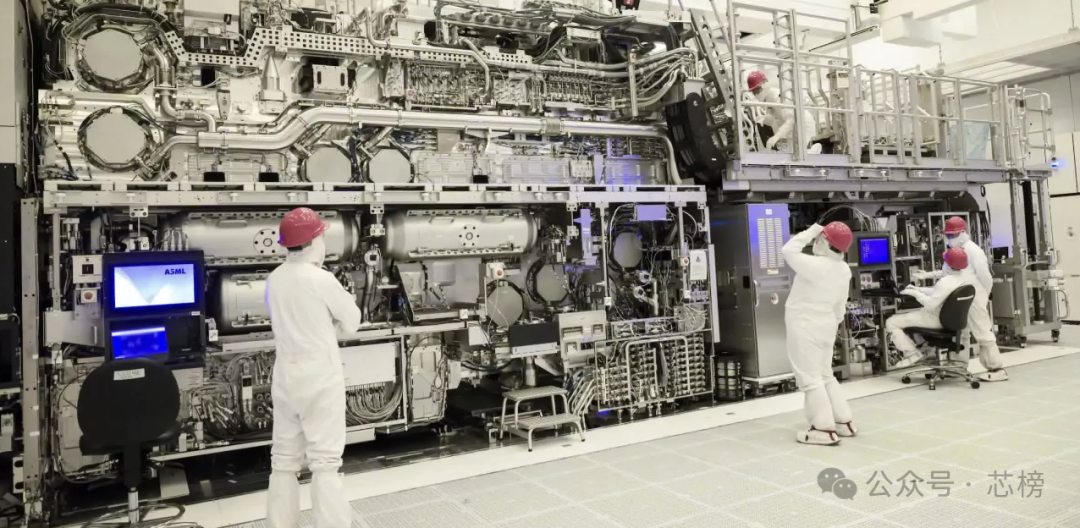

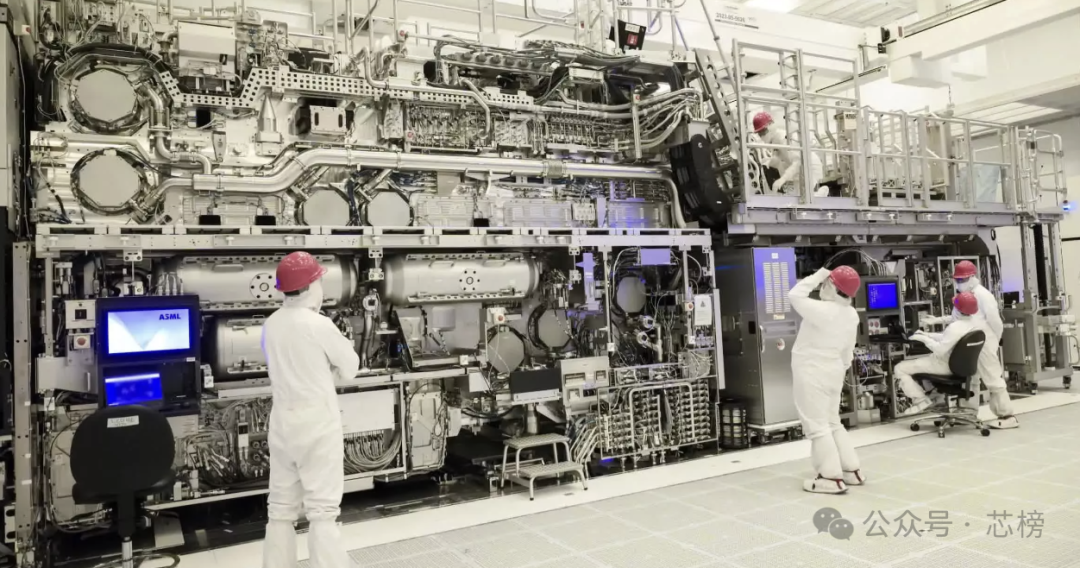

ASML的EUV设备是台积电、英特尔等巨头推进5纳米及以下先进工艺的基石。经过十余年研发与数百亿美元投入,其第二代EUV设备已接近量产,第三代也已进入早期研究阶段。

然而,成功的背后也伴随着明显的局限性。目前EUV设备的光刻面积大约只有邮票大小,这一物理限制直接制约了单颗芯片的尺寸与性能天花板。为此,ASML的工程师正试图通过光学与机械结构的重新设计来扩大光刻场域,目标是制造出物理尺寸更大、性能更强的芯片。

与此同时,一个曾经被视为常规的制造步骤——芯片与电路板的连接(即封装)——如今已演变为半导体行业最关键的瓶颈之一。随着英伟达、AMD以及存储芯片厂商海力士等公司致力于打造规模空前的芯片,它们开始采用垂直与水平堆叠技术,构建出由微型键合连接的“摩天大楼”式复杂架构。

先进封装技术能够将多块硅片集成到单一组件中,相比传统的单片芯片,可以实现更快的通信速度和更低的功耗。例如,台积电等代工厂已采用其高端封装技术,为英伟达生产旗舰级AI加速芯片。对ASML而言,这一产业趋势既是挑战,更是一个不容错过的全新商机。

技术赋能:AI驱动与多元化产品落地

AI不仅拉动了ASML下游客户的需求,也在反向重塑ASML自身设备的研发与运行方式。拥有软件部门背景的皮特斯指出,AI将被用于加速未来光刻与封装设备的控制算法和实时检测流程。

这些尖端设备在每一次晶圆加工中都会产生海量的高分辨率光学数据,利用深度学习等机器学习技术优化数据分析,可以有效减少设备停机时间、提升生产良率。

标志着这一多元化转型的首款产品已于去年面世:XT:260光刻机,它专为AI应用中的先进存储芯片设计。目前,工程师们正在研发更多系统,旨在将这些能力拓展到更复杂的逻辑芯片与3D堆叠工艺中。

为了更加聚焦于工程研发,ASML对其技术部门进行了精简。自2024年上任的首席执行官克里斯托夫·富凯(Christophe Fouquet),已将公司的发展路线明确锚定在超越EUV光刻机的业务扩张之上。

光学、精密运动控制系统与硅片处理技术的深度融合,赋予了ASML难以匹敌的技术根基。皮特斯表示,这些核心竞争力将支撑未来至少十年的全新产品线开发。规划中的大尺寸光刻机、先进键合设备与智能控制系统,将与ASML深耕四十年的光刻业务长期并存、协同发展,共同应对计算机基础架构演进带来的制造挑战。

这一系列动向不仅是ASML一家公司的战略调整,更是整个半导体设备行业面向AI时代的一次重要风向标。对于关注硬科技趋势的开发者与行业观察者而言,理解这些底层制造技术的演进,或许比追逐表面的应用更能把握未来。想了解更多前沿技术动态与深度解析,欢迎来云栈社区的开发者广场交流探讨。 |