在嵌入式开发中,中断处理函数(IRQHandler)是系统实现实时响应的关键。一个编写不当的中断服务程序,不仅可能导致功能异常,还可能引入难以调试的“幽灵”问题。本文将以恩智浦i.MXRT系列微控制器的GPIO模块为例,深入探讨中断处理函数的标准流程,并通过实际的串口波特率识别案例,剖析常见陷阱及其解决方案。

一、GPIO模块中断机制简介

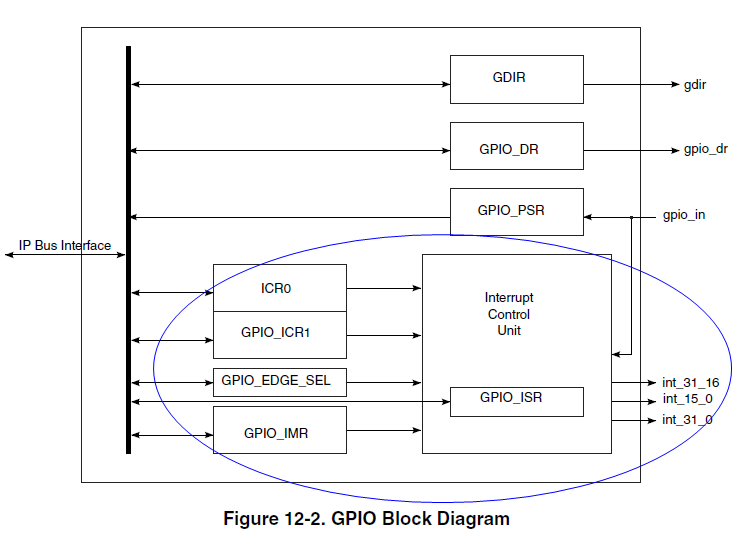

GPIO(通用输入输出)是MCU中最基础的外设之一。在i.MXRT中,除了基本的电平读写功能,GPIO模块通常还集成了强大的边沿检测与中断控制单元,这使其能够胜任诸如按键检测、脉冲计数等需要快速响应的任务。

1.1 GPIO基础功能设计

以i.MXRT1011为例,每组GPIO最多包含32个引脚,其核心是三个32位寄存器,它们共同构成了最基本的Computer Architecture中外设控制逻辑:

GDIR[31:0] - 配置引脚的输入/输出方向(仅在IOMUXC中配置为GPIO模式时生效)

DR[31:0] - 设置引脚输出电平

PSR[31:0] - 锁存引脚输入电平(以ipg_clk_s时钟采样)

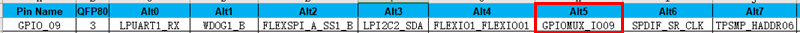

要操作这些GPIO寄存器,前提是在IOMUXC(IO复用控制器)模块中将目标引脚的功能模式设置为GPIO。例如,用于串口波特率检测的GPIO_09引脚,其复用功能选择表中,Alt5对应GPIO功能。

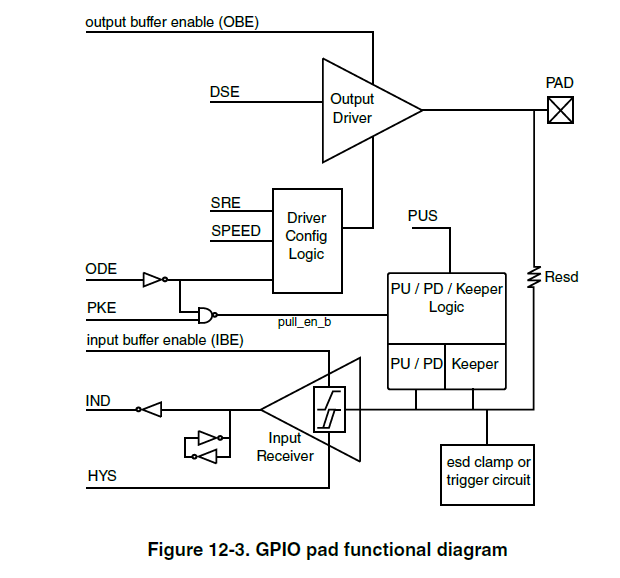

配置为GPIO模式后,还需根据电气特性配置Pad(焊盘)属性,如驱动强度、压摆率、上下拉电阻等。下图展示了一个典型的GPIO Pad内部电路结构。

在串口波特率检测场景下,需要将GPIO_09配置为输入模式并使能内部上拉(因为UART空闲时为高电平)。具体配置代码如下:

#include "fsl_iomuxc.h"

void io_pin_config(void)

{

CLOCK_EnableClock(kCLOCK_Iomuxc);

IOMUXC_SetPinMux(

IOMUXC_GPIO_09_GPIOMUX_IO09,

0U);

IOMUXC_SetPinConfig(

IOMUXC_GPIO_09_GPIOMUX_IO09,

0x01B0A0U);

}

1.2 GPIO中断功能设计

为了拓展应用,GPIO模块通常集成了中断控制单元。当引脚被配置为输入时,可以通过以下寄存器组来配置和响应边沿或电平变化中断:

EDGE_SEL[31:0] - 配置是否使能引脚双边沿检测

ICRx[31:0] - 配置低电平/高电平/上升沿/下降沿四种检测模式(当EDGE_SEL未使能双边沿时)

IMR[31:0] - 中断使能寄存器

ISR[31:0] - 中断状态寄存器

在i.MXRT中,为了节省中断控制资源,通常将16个GPIO引脚编为一组,共享一个中断号。例如,i.MXRT1011的中断向量表中定义如下:

typedef enum IRQn {

// ... 其他中断

GPIO1_Combined_0_15_IRQn = 70,

GPIO1_Combined_16_31_IRQn = 71,

GPIO2_Combined_0_15_IRQn = 72,

GPIO5_Combined_0_15_IRQn = 73,

// ...

} IRQn_Type;

在波特率检测案例中,我们需要将GPIO_09配置为下降沿触发中断,代码如下:

#include "fsl_gpio.h"

void io_func_config(void)

{

gpio_pin_config_t sw_config = {

kGPIO_DigitalInput,

0,

kGPIO_IntFallingEdge,

};

GPIO_PinInit(GPIO1, 9, &sw_config);

GPIO_PortEnableInterrupts(GPIO1, 1U << 9);

NVIC_SetPriority(GPIO1_Combined_0_15_IRQn, 1);

NVIC_EnableIRQ(GPIO1_Combined_0_15_IRQn);

}

二、中断处理函数(IRQHandler)的标准流程与问题剖析

现在,我们进入核心部分。假设上位机以115200bps的波特率发送特定的握手信号(0x5A, 0xA6),理论上会在GPIO_09上产生7个下降沿。我们来看一个最初版本的中断处理函数存在哪些问题。

2.1 有瑕疵的中断处理函数实现

2.1.1 问题一:无效中断的重复执行

最初的中断处理函数如下:

uint32_t s_irqCount = 0;

void GPIO1_Combined_0_15_IRQHandler(void)

{

s_irqCount++;

GPIO1->DR_TOGGLE = 1U << 10;

uint32_t interrupt_flag = (1U << 9);

if ((GPIO_GetPinsInterruptFlags(GPIO1) & interrupt_flag) && s_pin_irq_func)

{

s_pin_irq_func();

GPIO_ClearPinsInterruptFlags(GPIO1, interrupt_flag);

}

}

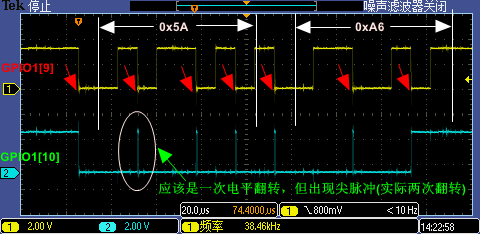

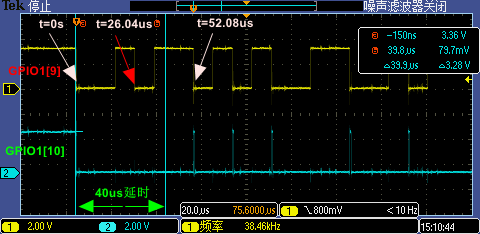

我们期望s_irqCount在识别结束后等于7,但实际测试值为12,多执行了5次。然而,核心回调函数s_pin_irq_func确实只执行了7次。通过用另一个GPIO1_10引脚翻转来辅助观测,示波器波形揭示了问题:每个下降沿竟然连续触发了两次中断处理函数。

根源分析:这与ARM Cortex-M4/M7内核的勘误文档838869描述的情况有关。当CPU运行速度(如500MHz)远高于外设寄存器写入速度时,如果在中断函数末尾才清除中断标志,可能会导致CPU在标志位被物理清除前,再次检测到其“置位”状态,从而立即重入中断。回调函数未被误执行,仅仅是因为在判断if语句时,标志位“恰好”被清除了,但这种依赖时序的行为并不可靠。

2.1.2 问题二:密集中断下的响应丢失

中断处理的一个基本原则是“快进快出”。为了模拟中断服务程序执行过长的情况,我们在第一次中断响应中故意添加了40us的延时。

uint32_t s_irqCount = 0;

uint32_t s_irqDelay = 40;

void GPIO1_Combined_0_15_IRQHandler(void)

{

s_irqCount++;

GPIO1->DR_TOGGLE = 1U << 10;

uint32_t interrupt_flag = (1U << 9);

if ((GPIO_GetPinsInterruptFlags(GPIO1) & interrupt_flag) && s_pin_irq_func)

{

s_pin_irq_func();

if (s_irqDelay)

{

microseconds_delay(s_irqDelay);

s_irqDelay = 0;

}

GPIO_ClearPinsInterruptFlags(GPIO1, interrupt_flag);

}

}

在115200bps下,位周期约为8.68us,第一个下降沿到第二个下降沿约26us。40us的延时将导致无法及时响应第二个下降沿。测试结果令人担忧:s_pin_irq_func只执行了6次,漏掉了一次。这是因为在第一次中断服务程序执行期间发生的第二次中断,其状态位可能被第一次中断退出前的清除操作“一并”清除了。

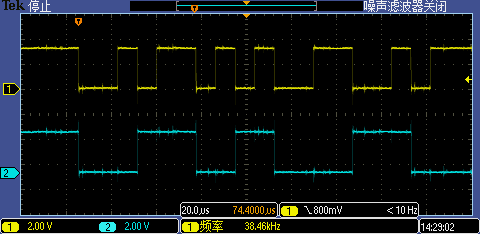

2.2 针对性解决方案

2.2.1 解决无效重入:确保标志位清除

根据勘误文档建议,在清除中断标志后,应插入一条数据同步屏障(DSB)指令,或通过回读状态寄存器来确保写入操作已完成。

void GPIO1_Combined_0_15_IRQHandler(void)

{

GPIO1->DR_TOGGLE = 1U << 10;

uint32_t interrupt_flag = (1U << 9);

if ((GPIO_GetPinsInterruptFlags(GPIO1) & interrupt_flag) && s_pin_irq_func)

{

s_pin_irq_func();

GPIO_ClearPinsInterruptFlags(GPIO1, interrupt_flag);

__DSB();

}

}

改进后,波形恢复正常,无效重入问题得以解决。

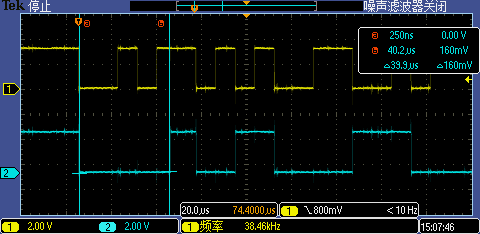

2.2.2 缓解中断丢失:优先清除标志

要减少因处理时间过长而丢失后续中断的风险,一个有效策略是尽早清除中断标志。即使中断服务程序还在执行,新的边沿到来会再次置起标志位,从而保证不会丢失。

void GPIO1_Combined_0_15_IRQHandler(void)

{

GPIO1->DR_TOGGLE = 1U << 10;

uint32_t interrupt_flag = (1U << 9);

if ((GPIO_GetPinsInterruptFlags(GPIO1) & interrupt_flag) && s_pin_irq_func)

{

GPIO_ClearPinsInterruptFlags(GPIO1, interrupt_flag);

__DSB();

s_pin_irq_func();

if (s_irqDelay)

{

microseconds_delay(s_irqDelay);

s_irqDelay = 0;

}

}

}

这种方法确保了第二次下降沿的中断状态位能够被记录,尽管其响应时刻的精确性无法保证,但对于波特率识别场景,功能得以恢复。但请注意,如果在第一次中断处理期间发生了两次以上的同类中断,此方法仍可能丢失事件。

2.3 中断处理函数的标准四步流程

综合以上分析与实践,一个稳健的中断处理函数应遵循以下标准流程:

- 确认中断源:检查具体的中断状态标志位(对于共享中断号的情况尤为重要)。

- 立即清除标志:尽快清除已响应的中断标志,为接收下一次中断做好准备。

- 确保清除完成:使用

DSB指令或回读操作,确保清除操作已对CPU可见,防止错误重入。

- 执行核心任务:执行实际的中断处理工作。此部分应尽可能简短,理想情况下仅记录必要信息(如置位标志、写入队列),将耗时操作留给主循环。

标准模板如下:

void xxx_IRQHandler(void)

{

if (xxx_IsInterruptFlagSet() && s_irq_func)

{

xxx_ClearInterruptFlag();

__DSB();

s_irq_func();

}

}

三、番外:i.MXRT中特殊的GPIO1低8位中断

值得一提的是,在部分i.MXRT型号(如RT1062)中,GPIO1的低8位引脚(GPIO1[7:0])享有“特殊待遇”,它们除了归属于GPIO1_Combined_0_15_IRQn这个组合中断外,还各自拥有独立的中断号,这在需要极高响应精度或复杂中断优先级管理的场景下非常有用。

typedef enum IRQn {

// ...

GPIO1_INT0_IRQn = 72,

GPIO1_INT1_IRQn = 73,

// ... 直到 GPIO1_INT7_IRQn = 79

GPIO1_Combined_0_15_IRQn = 80,

// ...

} IRQn_Type;

通过以上以i.MXRT GPIO为例的深入探讨,我们不仅理解了中断处理函数的标准流程,更重要的是学会了如何Debugging实际项目中可能出现的中断相关问题。编写中断服务程序时,时刻牢记“清除标志、快速执行”的原则,是构建稳定可靠嵌入式系统的基石。希望这篇详解能对你的开发工作有所帮助。更多关于Memory Management、内核机制等深度内容,欢迎在云栈社区交流探讨。