内存制造商正积极寻求将混合键合(Hybrid Bonding)工具作为关键的差异化竞争手段,SK海力士已释放出转向生产规模化应用的信号。

SK海力士的设备采购标志着其正转向在大规模HBM制造中扩展混合键合技术。来自应用材料(Applied Materials)与BESI(BE Semiconductor Industries)的集成解决方案旨在降低工艺复杂度,并解决由CMP(化学机械抛光)驱动的关键挑战。

混合键合是在异质集成中实现精细间距(Fine Pitch)和高密度堆叠的关键技术。

HBM:AI与HPC的支柱

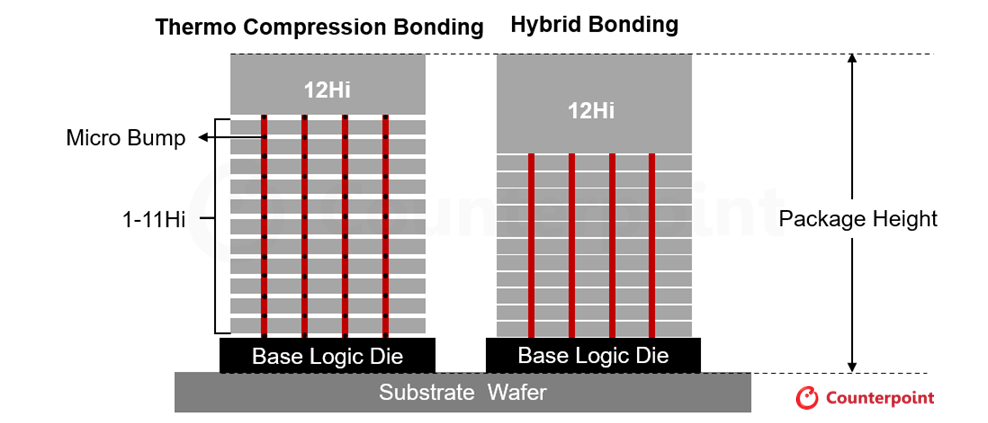

高带宽内存(HBM)已成为人工智能(AI)和高性能计算(HPC)的关键驱动力,提供了大型语言模型等数据密集型工作负载所需的带宽和效率。HBM通常在基础逻辑层(Base Die)上堆叠12-16层DRAM裸片,并与GPU集成在一起。目前,这些堆叠依赖于微凸点(Micro-bump)互连,使用诸如带模制底部填充的热压分层回流焊(MR-MUF)或带非导电薄膜的热压键合(TC-NCF)等方法。

然而,微凸点正逐渐成为限制信号完整性、功率效率和散热性能的关键瓶颈。随着堆叠高度增加到20层以上,GPU封装内的物理高度和集成限制变得更加突出。

热压键合 (TCB) vs. 混合键合(数据来源:Counterpoint Research, BESI)

向混合键合转变

为了克服这些限制,行业正转向混合键合,该技术能够实现:更精细的互连间距、缩短裸片间距、降低堆叠高度、更高的带宽和能效。

尽管JEDEC放宽了HBM高度规范,允许在多达16层的产品中继续使用TCB,但三星电子、SK海力士和美光科技等领先内存厂商正积极推进HBM4及更高版本的混合键合技术,以满足下一代AI需求。

CMP:混合键合的关键助力

化学机械抛光(CMP)是HBM制造的基础,确保裸片堆叠所需的平整度、铜(Cu)高度控制和无缺陷表面。

在TCB中,CMP起辅助作用,因为微凸点可以容忍表面偏差。在混合键合中,CMP变得至关重要,因为键合依赖于超平整、原子级光滑的表面。

任何CMP缺陷(如铜凹陷 dishing、侵蚀或污染)都会直接影响良率、电阻和可靠性。这使CMP从一个工艺步骤提升为决定HBM4及更高版本性能、互连密度和缩放的关键因素。

协同优化:应用材料 + BESI

应用材料与BESI的合作将CMP、表面准备和混合键合集成到一个受控的单一流程中。

- 结合了应用材料在CMP和材料工程方面的优势,以及BESI在混合键合和芯片放置领域的领先地位。

- 降低了工艺复杂度、波动性和缺陷风险。

- 提高了对准精度和键合良率。

SK海力士采购集成式混合键合工具反映了其解决混合键合关键挑战的战略举措,特别是围绕CMP驱动的表面均匀性、铜凹陷、颗粒缺陷和超严苛粗糙度控制。该集成平台直接致力于解决这些关键瓶颈,实现更稳定的制造,降低良率风险,并加速混合键合向大规模生产的过渡。

关键挑战

HBM标准放宽风险: JEDEC增加允许的HBM高度可能会推迟混合键合的应用,延长TCB的生命周期,并给设备需求带来不确定性。

工艺敏感性: 混合键合对CMP质量高度敏感,尽管电性能优越,但凹陷、污染和空隙等缺陷会增加电阻并影响良率。

对内存厂商的影响

在短期内,推迟混合键合可以:降低资本支出强度,利用成熟的TCB工艺获得更好的良率。

然而,由于性能要求的提升,长期采用混合键合仍是必然趋势。一个关键驱动因素是NVIDIA,其AI工作负载需要更高的带宽和效率。三星、SK海力士和美光等供应商将HBM路线图与NVIDIA的要求挂钩,这意味着更强的性能需求可能会加速混合键合的采用。

SK海力士在AI服务器中使用的HBM及其他芯片的质量和供应领先地位,在当前AI基础设施繁荣阶段至关重要。根据Counterpoint Research关于生成式AI内存解决方案的报告,SK海力士继续在高带宽内存领域领跑,其创新包括:存储单元设计的创新(前道工艺改进)、后端堆叠增强以及在基础逻辑芯片中集成逻辑电路(IVC)进行电压控制。此外,随着AI部署加速,内存挤压正在加剧,导致结构性供应短缺可能持续到2030年。然而,2028年可能会成为转折点,届时新一波生产集群将开始上量。

HBM5将是混合键合的真正爆发点

HBM5将成为混合键合真正的转折点,支持20层以上的堆叠、更精细的间距和更高水平的带宽,同时需要在CMP、良率和成本方面取得突破以实现大规模制造。

对于SK海力士而言,早期采用应用材料和BESI的集成解决方案提供了战略优势,使其能够满足带宽、延迟、功耗和速度方面的未来要求,无论过渡期的标准是否放宽。利用应用材料的工艺模块(CVD, PVD, ECD, CMP, 表面准备)经验和Besi的混合键合技术,将为实现先进、大批量芯片生产所需的稳定性和一致性奠定必要基础。

我们预计SK海力士将在2029-2030年推出HBM5,与下一代AI GPU周期对齐,混合键合将在HBM5节点达到大规模应用。

结论

当HBM缩放超过约16层以及AI性能需求上升时,微凸点封装已接近极限。混合键合提供了一条可扩展的路径:亚 10µm(<10µm)的互连间距(相比之下微凸点为20µm-40µm)、更高的带宽和能源效率、与以逻辑芯片为中心的集成兼容。

随着HBM越来越接近逻辑节点的工艺要求,混合键合对于维持性能缩放变得不可或缺。由应用材料和BESI主导的CMP与键合协同优化,正成为这一转型的关键赋能者。

SK海力士从应用材料和BESI采购集成式混合键合工具,将解决HBM制造中的关键挑战,同时提供满足下一代性能需求的战略优势,维持其HBM领导地位,并驱动营收增长和市场份额提升。

原文链接: https://counterpointresearch.com/en/insights/Hybrid-Bonding-Expands-from-Logic-to-Memory-SK-Hynix-Applied-Materials-BESI-Drive-Co-optimization-to-Scale-Next-gen-HBM

(来源:counterpoint)

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

了解更深入的计算机基础知识,欢迎访问云栈社区,获取更多专业的技术分享与讨论。