AI进化得太快了。主流模型从稠密大语言模型转向大规模混合专家(MoE),推理负载飙升,还得支撑Agentic AI——那些能自主规划、多轮推理的智能体,甚至要驱动世界模型进行模拟想象。老硬件只知道堆浮点算力,已经跟不上新工作负载对效率、延迟和带宽的要求。

谷歌第八代TPU正是为此而生。它没有做一颗通吃所有场景的芯片,而是拆成了TPU 8t(预训练专用)和TPU 8i(推理部署专用)。两款芯片针对AI生命周期不同阶段的瓶颈专门优化,配合Arm架构的Axion CPU解放数据准备的主机瓶颈,整体效率比上一代提升非常显著。无论是要跑预训练的第一个token,还是多轮推理的最后一步,都能找到最高效的路径。

谷歌第八代TPU

为什么需要两款芯片?需求从来就不一样

预训练、后训练、实时推理这三个阶段,对硬件的要求差异极大。一颗芯片打全场,结果就是每个场景都做不到最优,白白浪费算力和成本。

所以谷歌直接拆出两条产品线,它们同属谷歌云AI超级计算机的核心,共享基础设计,但各自解决不同的瓶颈。全系列都集成了Arm架构的Axion CPU作为主控,扛住复杂的数据预处理和调度,保证TPU始终有数据可吃,不会空转等待。

TPU 8t:为大规模预训练而生的性能猛兽

TPU 8t专门优化大规模预训练和embedding密集型负载,延用了谷歌成熟的3D环面网络拓扑。一个超级pod就能放下9600颗芯片,几百个pod并行也能维持吞吐量,不拖训练后腿。

1. SparseCore解决稀疏计算瓶颈

SparseCore是TPU 8t的核心,专门处理embedding查询这类不规则内存访问。所有数据相关的“全收集”操作都卸载给SparseCore,避免了通用芯片上常见的空操作瓶颈,矩阵乘法单元MXU可以专心做自己的事。

2. VPU与MXU并行,提升算力利用率

TPU 8t重新平衡了向量处理单元(VPU)的规模,让量化、softmax、层归一化等向量操作与MXU的矩阵乘法更好地重叠执行。原来芯片做完矩阵乘法还得等向量处理完才能启动下一轮,现在两个活儿一起干,芯片不摸鱼,每块浮点算力都能用满。

3. 原生FP4支持,MXU吞吐直接翻倍

首次加入原生4位浮点(FP4),直击内存带宽瓶颈。更低精度不会损伤大模型精度,却能让MXU吞吐量翻倍。每个参数占用的位数更少,搬运的数据更少,能耗更低,还能把更大的模型层塞进本地缓存,算力利用率拉满。

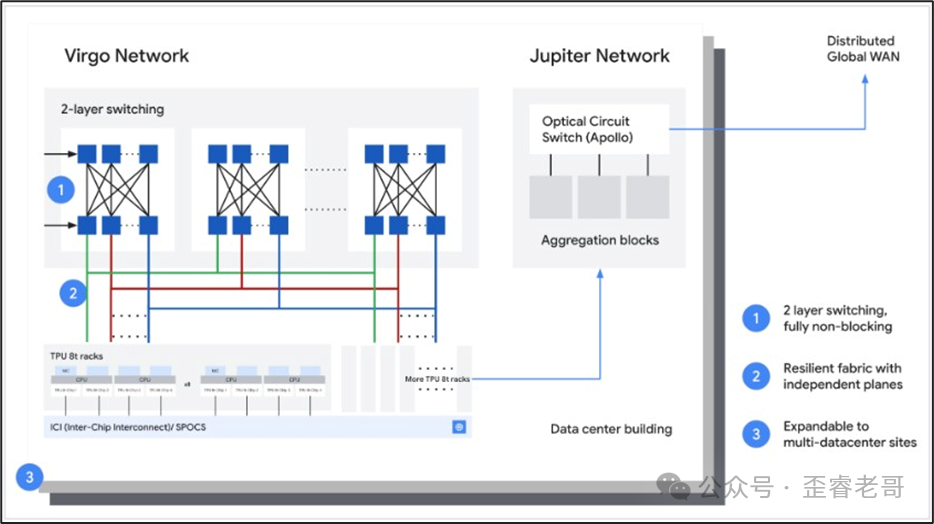

4. Virgo新网络,数据中心带宽最高提升4倍

TPU 8t换上了全新的Virgo网络架构。它采用高基数交换机,做成扁平的两层无阻塞拓扑,比传统数据中心跳数更少、延迟更低。多平面设计通过独立控制域连接芯片,机架还能接入Jupiter南北向骨架,访问计算和存储服务。

对比上一代,芯片间互联(ICI)带宽翻倍,数据中心扩展带宽最高提升4倍。配合JAX和Pathways,一个训练集群能扩展到超过100万颗TPU芯片;Virgo网络可连接13.4万颗TPU 8t,整个fabric提供47Pb/s的无阻塞对剖带宽,总算力突破160万exaFLOPS,且接近线性扩展。

TPU 8t机架连接Virgo fabric示意图

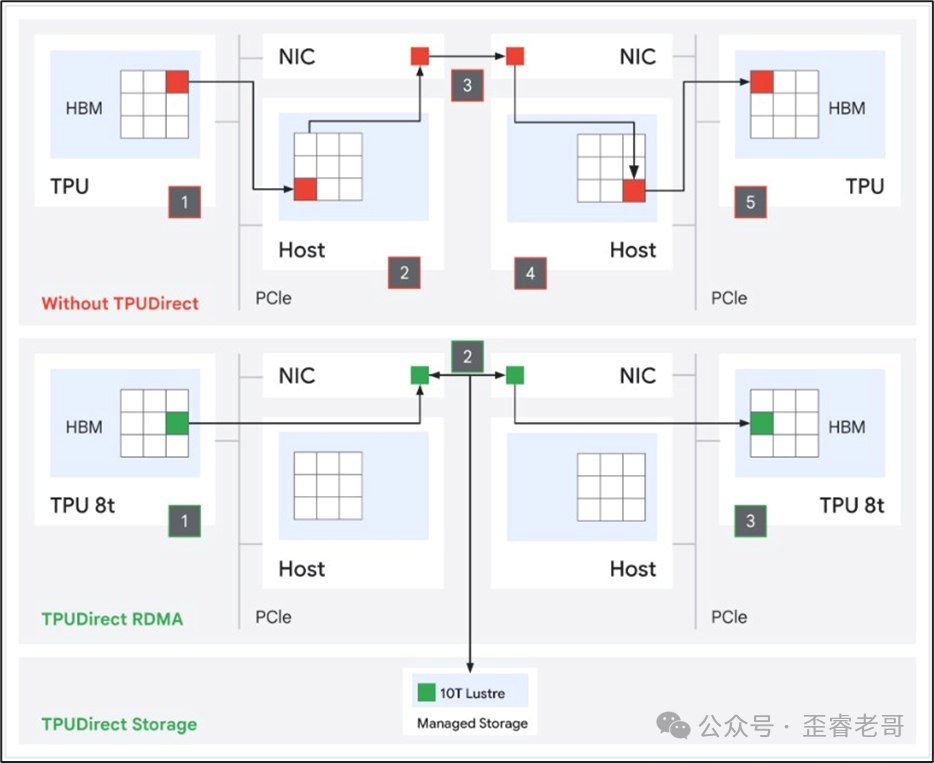

5. TPUDirect技术,存储访问快10倍

TPU 8t加入了TPUDirect RDMA和TPUDirect Storage,数据不再绕经主机CPU和内存,而是直接在TPU的HBM与网卡、存储之间传输。RDMA降低了TPU之间通信的延迟和主机瓶颈,有效带宽大幅提升;TPUDirect Storage直接让TPU访问高速存储,大规模数据传输带宽翻倍,芯片能吃到满速数据。

配上10T Lustre托管存储,百PB级数据直送芯片,再也不用担心数据跟不上导致训练延期。对比上一代Ironwood TPU,存储访问速度足足快了10倍。

有无TPUDirect Storage的数据路径对比图

TPU 8i:后训练与高并发推理的专家

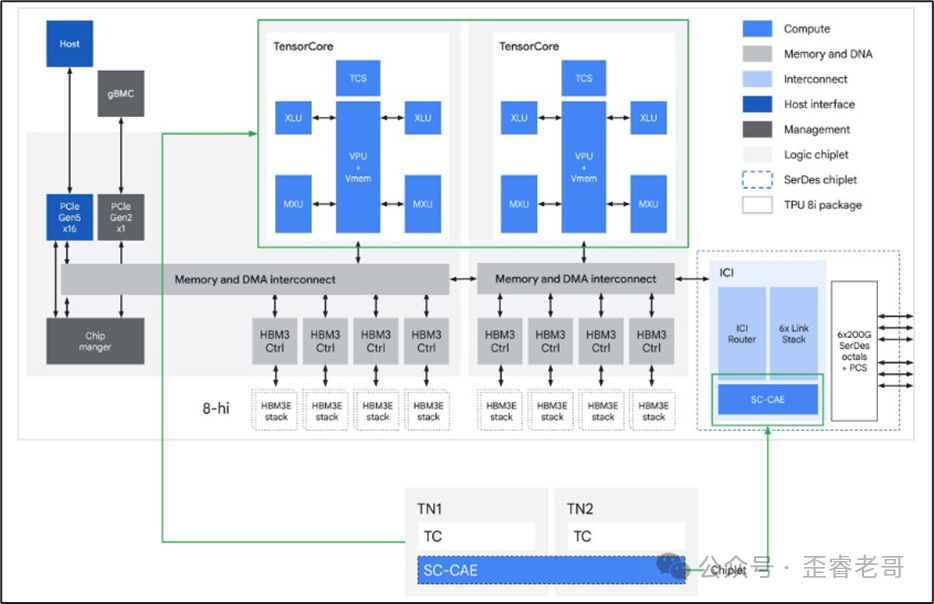

TPU 8i专为后训练采样和高并发推理优化,搭载谷歌目前容量最大的片上SRAM、全新的集合加速引擎(CAE),以及专门为推理设计的Boardfly网络拓扑。

1. 超大SRAM,终结长上下文等待

片上SRAM容量翻了3倍,能把更大的KV缓存全部放在芯片上。长上下文解码时,核心不必苦苦等待数据,空闲时间骤减,推理速度自然上去。

TPU 8i ASIC模块框图

2. 集合加速引擎CAE,集体操作延迟降低5倍

采样和自回归推理最头疼的就是不同核心之间的结果聚合同步。TPU 8i用硬件CAE单元来做聚合,几乎零延迟,特别适合自回归解码和思维链推理这类同步密集步骤。

每颗TPU 8i有两个张量核心在核心裸片上,一颗CAE放在小芯片上,取代了上一代Ironwood TPU核心裸片上的4个SparseCore。硬件加速后,片上集体操作的延迟直接降低5倍。更少的时间花在同步上,就能撑起更高并发,同时运行上百万个智能体也不在话下。

3. Boardfly新拓扑,全对全通信延迟砍半

预训练常用的3D环面拓扑虽然适合邻居间通信,但面对MoE和推理中任意芯片都可能与任意芯片通信的场景,跳数过多,延迟太高。

TPU 8i换上Boardfly拓扑,高基数设计最多连接1152颗芯片,直接缩短网络直径。对于MoE和推理模型最核心的全对全通信,Boardfly把延迟降低了最多50%。

拿1024颗芯片的pod算一笔账就明白了:

- 3D环面结构为8×8×16,最远芯片要走4+4+8=16跳;

- Boardfly拓扑下,最远芯片只需7跳,跳数直接减少56%,尾巴延迟显著下降,CAE再也不用空等数据。

TPU 8i Boardfly拓扑层级结构示意图

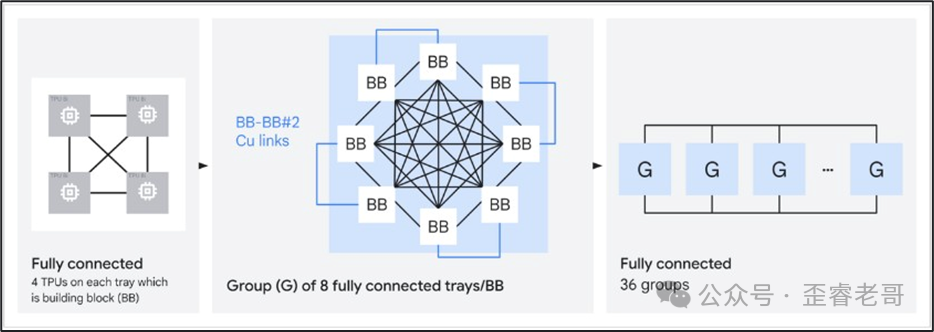

Boardfly采用三层结构:

- 第一层,基础块,每个托盘用内部ICI链路做成4芯片环,预留16个外部接口;

- 第二层,本地组,8个板用铜线全连接成一个组,用11个接口做组内通信;

- 第三层,pod结构,一个pod塞36个组,最多1024颗活跃芯片,用光线路由器连接,任意芯片通信最多7跳就能抵达。

一表看尽两台机器的关键参数

| 特性 |

TPU 8t |

TPU 8i |

| 核心场景 |

大规模预训练 |

采样、部署、推理 |

| 网络拓扑 |

3D环面 |

Boardfly |

| 专用硬件 |

SparseCore(embedding处理) |

CAE集合加速引擎 |

| HBM容量 |

216GB |

288GB |

| 片上SRAM |

128MB |

384MB |

| FP4峰值算力 |

12.6 PFLOPs |

10.1 PFLOPs |

| HBM带宽 |

6528 GB/s |

8601 GB/s(约为8t的1.3倍) |

| 主控CPU |

Arm Axion |

Arm Axion |

软件栈:不丢性能,还让开发更顺滑

硬件再强也要软件配。第八代TPU延续了性能优先的软件栈,既不用手写底层代码,也不会牺牲效能:

- Pallas与Mosaic:原生支持Pallas——谷歌自定义的内核语言,能用Python写硬件感知的内核,将TPU 8i的CAE和TPU 8t的SparseCore性能榨干。

- 原生PyTorch支持:TPU已预览支持原生PyTorch,现有的PyTorch模型几乎不用大改就能迁移,Eager Mode等常用特性全部保留。

- 可移植性:原本跑在Ironwood上的JAX、PyTorch、Keras代码,直接就能在这代TPU上扩展。XLA会自动处理不同拓扑和CAE同步的复杂转换,你只需要关心模型,不用管互联。

性能提升到底有多大?看这组对比就清楚

谷歌坚持软硬件协同设计,这一代的收益非常直接:

- 训练性价比:TPU 8t对比上一代Ironwood TPU,大规模训练的每美元性能最高提升2.7倍。

- 推理性价比:TPU 8i对比上一代,大规模MoE模型低延迟推理场景,每美元性能最高提升80%。

- 能效比:两款芯片的每瓦性能都最高提升2倍,这对可持续的大规模AI扩展至关重要。

这才是Agent时代硬件该有的样子

AI已经进入Agentic AI时代,能做规划、能在反馈循环里学习的推理智能体,与原来针对传统训练和事务推理优化的老硬件,运算特征根本不同。

谷歌没有硬堆通用算力,而是直接拆分产品线,与DeepMind深度合作从整体重构,正是看准了这一点:未来的AI基础设施,必然是专业化分工,而不是一颗芯片打全场。

类似的观点,在云栈社区的技术讨论中也常常被提及。

引用:https://cloud.google.com/blog/products/compute/tpu-8t-and-tpu-8i-technical-deep-dive