在累加或乘累加运算中,合理选择位宽至关重要。一旦位宽设置不当,就可能发生溢出错误。溢出通常分为上溢(Overflow)和下溢(Underflow),前者指计算结果超出了数据格式能表示的最大值,后者则指结果小于最小值。

Xilinx DSP48E 模块提供了专门的 overflow 和 underflow 输出端口来检测这类问题,但这需要结合其模式检测(Pattern Detection)功能一同使用。本文将以一个乘累加操作为例,详细说明如何配置以实现溢出监控。

假设我们的累加器输出数据格式为 fix<4,0>,即一个4位有符号二进制数。该格式能够表示的数值范围为 [-8, 7],分辨率为1。

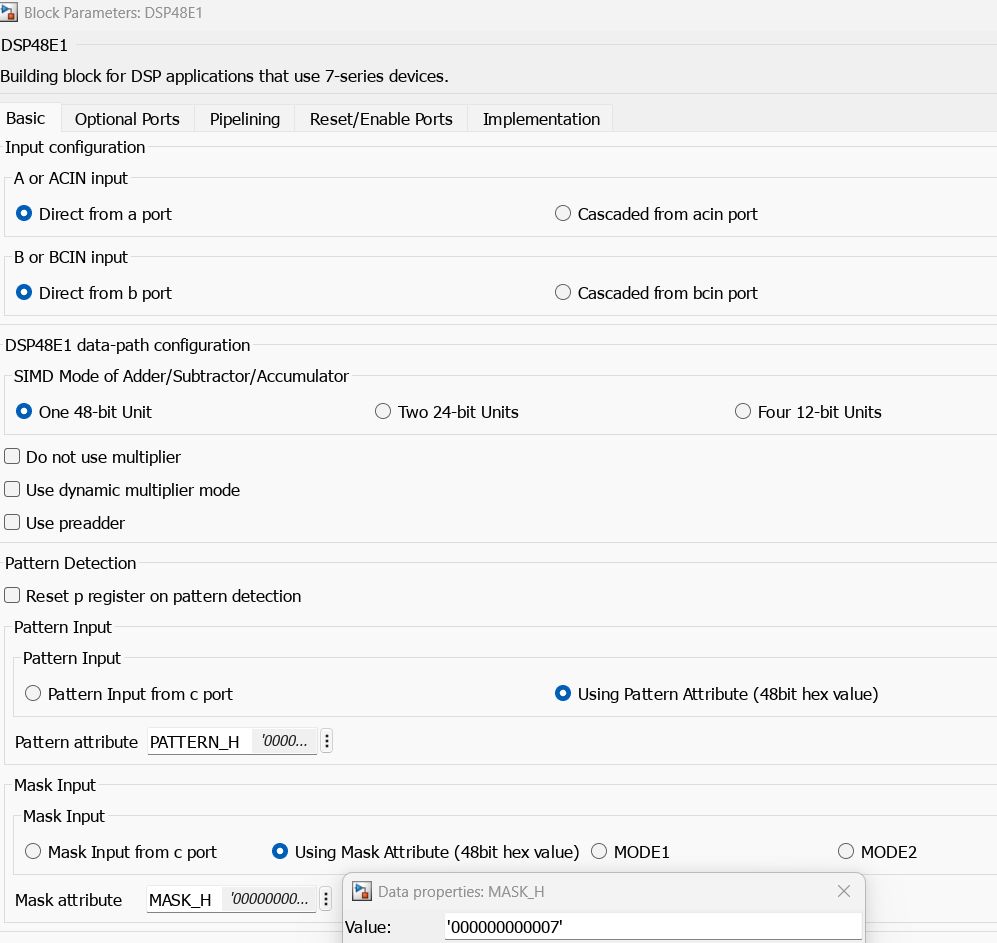

要启用DSP48E的溢出检测功能,关键在于正确配置模式检测器及其关联的掩码(MASK)。掩码值应设置为 (2^N)-1,其中 N 等于目标数据格式字长减1。对于本例的 fix<4,0> 格式,N=3,因此 MASK = 2^3 - 1 = 7。注意,需要将此值转换为48位的十六进制形式进行配置。此设置意味着模式检测器将忽略输出端口 P 的低3位。

一个4位有符号二进制数能表示的最大值是 4‘b0111(十进制7),最小值是 4’b1000(十进制-8)。在DSP48E中,我们需要将 PATTERN 属性设置为全0,并确保 patterndetect 和 patternbdetect 端口被启用。

图1:DSP48E1模块配置界面,需启用模式检测并设置MASK与PATTERN

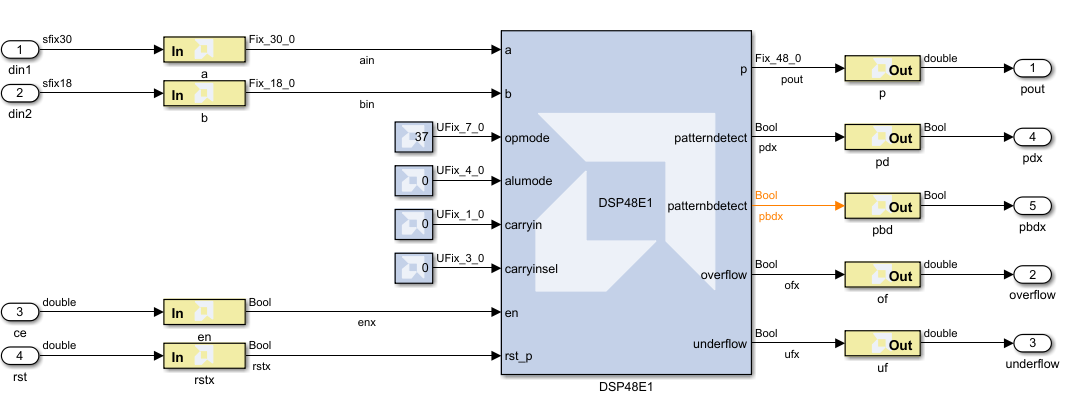

对应的硬件电路结构如下图所示。请务必注意,P 端口的输出寄存器必须启用,即 PREG 需设置为1。

图2:实现溢出检测功能的DSP48E1模块内部数据路径框图

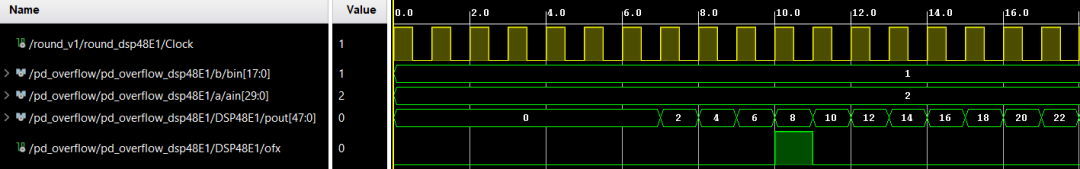

完成上述配置后,我们来看仿真结果。下图展示了上溢(Overflow)的检测情况:当输出结果达到8时,overflow 信号拉高,并持续一个时钟周期。

图3:上溢(Overflow)检测仿真波形图

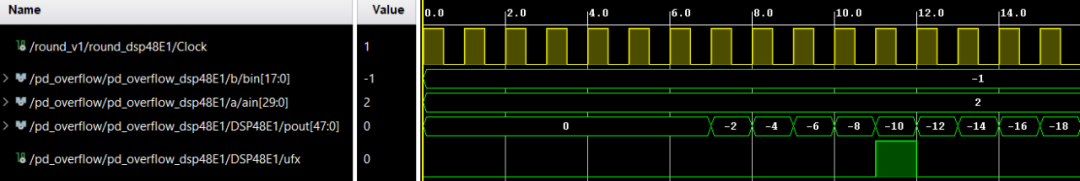

同理,下图展示了下溢(Underflow)的检测情况:当输出结果为-10时,underflow 信号拉高,同样持续一个时钟周期。

图4:下溢(Underflow)检测仿真波形图

通过合理配置DSP48E的模式检测功能,我们可以高效、精准地捕捉运算中的溢出异常,为高可靠性FPGA设计提供保障。希望这篇关于DSP48E溢出检测的实战解析对你有帮助。欢迎在云栈社区交流更多数字信号处理与FPGA设计经验。 |