对于包含锁存器的设计,静态时序分析 (STA) 会应用一个称为 时间借用 的概念。如果你在设计中使用锁存器并在时序报告中看到相关提示,理解这个概念至关重要。

本文首先解释时间借用的核心思想,随后探讨 STA 工具在分析锁存器设计时如何具体应用这一机制。

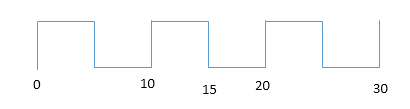

假设时钟周期为 10 个时间单位,占空比为 50%,其波形如下:

图1:周期为10个时间单位的时钟波形

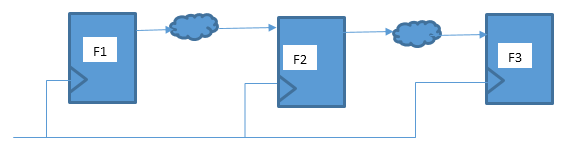

同时,考虑一个简单的三级触发器电路:

图2:F1、F2、F3三级触发器级联示意图

为了简化分析,我们假设所有触发器的建立时间和保持时间均为 0,时钟偏斜和时钟延迟也为 0。

在 0 时刻从 F1 发出的数据,必须在 10 时刻之前到达 F2 才能被正确捕获。同理,从 F2 发出的数据也有 10 个时间单位传送到 F3,并在下一个时钟沿被采样。

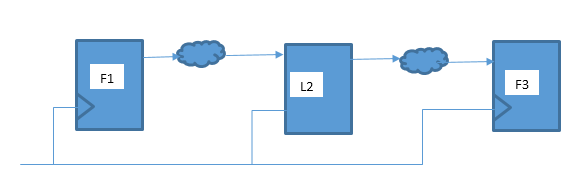

现在,我们将中间的触发器 F2 替换为一个由同一时钟驱动的锁存器 L2:

图3:中间级为锁存器L2的电路结构

让我们先理解时间借用的概念,之后再讨论 STA 的具体分析。

从 F1 到 L2 的路径分析:

如果数据在 10 时刻之前到达锁存器输入端,它会像在触发器前一样等待。但关键区别在于,如果数据在 10 时刻之后到达呢?锁存器 L2 在 10 到 15 的时间段内是“透明”的。因此,只要数据在 15 时刻之前到达,L2 仍然能够捕获并使用它。

例如,若数据在 12 时刻到达 L2,这意味着锁存器为这条路径提供了 2 个时间单位的额外裕量(相较于触发器)。在这个例子中,L2 能提供的最大优势(即最大可借用时间)是 5 个时间单位(透明窗口的宽度)。

从 L2 到 F3 的路径分析:

数据在 12 时刻从 L2 输出,并需要在 20 时刻被 F3 采样。因此,留给这条路径的时间只有 8 个时间单位(20 - 12)。

时间借用的本质:

在全触发器的电路中,F2 到 F3 的路径本有 10 个时间单位。但在当前电路中,它少了 2 个时间单位。这 2 个时间单位被前一级路径(F1 到 L2)“借用”了。

馈入锁存器的路径 获得了额外的 2 个时间单位以满足时序,因此 锁存器之后的路径 不得不从其原有的 10 个时间单位份额中“让出”这 2 个单位。

关键点总结:

馈入锁存器的路径可以从后续路径借用时间(最大不超过锁存器的透明窗口)。实际借用的时间量是路径满足时序所需的最小值(受限于最大可借用时间)。

- 本例最大可借用时间量 = 5 个时间单位。

- 本例实际借用时间量 = 2 个时间单位。

这意味着,除了默认的 10 个时间单位外,F1 到 L2 的路径又额外“使用”了 2 个单位才满足时序要求。

理解了基本概念后,我们来看 STA 工具如何对这类设计进行分析。

建立时间分析:

对于在 0 时刻由 F1 发出的数据,L2 在 0 到 5 的时间窗口内是开放的,可以捕获数据。

STA 工具会将 0 时刻视为 L2 的捕获沿,并附带一个 5 个时间单位的借用容量。同时,从 L2 到 F3 的路径分析为:在 0 时刻发送,在 10 时刻于 F3 处捕获。因此,整体从 F1 到 F3 的路径总时间预算为 10,其中最多 5 个单位可用于 L2 之前的部分,剩余部分用于 L2 之后。

保持时间分析:

保持时间分析要确保前一个周期的数据不会被新数据干扰。F1 在 0 时刻发送的数据,可能在 0 到 5 期间被 L2 捕获。

那么,F1 在下一个周期(10 时刻)发送的数据呢?如果它在 5 时刻之前到达 L2,就会干扰 0 时刻的数据。因此,STA 工具会针对 F1 在 10 时刻发送的数据和 L2 在 5 时刻的捕获沿,执行一次保持时间检查,确保新数据不会过早到达。

通过对时间借用机制的剖析,我们可以更好地理解锁存器在时序路径上的独特行为,这对于进行深层次的数字电路设计与分析非常有帮助。想了解更多底层原理与设计优化,欢迎在 云栈社区 的“基础与综合”版块交流探讨。