瑞芯微(Rockchip)的发展历程颇具代表性。从2001年以解决复读机“变速不变调”难题起家,到随后在MP3/MP4市场和安卓平板处理器领域取得成功,再逐步拓展至物联网、AI、智能家居及汽车电子等广阔领域。如今,瑞芯微已成为领先的AIoT处理器芯片提供商,其产品不仅具备强大的NPU算力和丰富的音视频接口,更在不断集成满足工业场景需求的高速通信接口。

本文聚焦于瑞芯微最新在RK3506和RK3576等处理器上集成的一个高度灵活的并行总线接口——FlexBus。

灵活配置的并行总线FlexBus

FlexBus是瑞芯微专为处理器与外部设备通信设计的高度灵活的并行总线接口。其主要特点体现在以下两方面:

- 协议配置灵活:它能够通过软件配置和逻辑设计,模拟标准或不规则的外部设备协议时序,从而适配如ADC、DAC、FPGA等多种外设。

- 传输高效:支持2/4/8/16bit的可变位宽并行传输,提供多达16根数据线(分为2组),时钟速率最高可达100MHz,确保了高速数据传输能力。

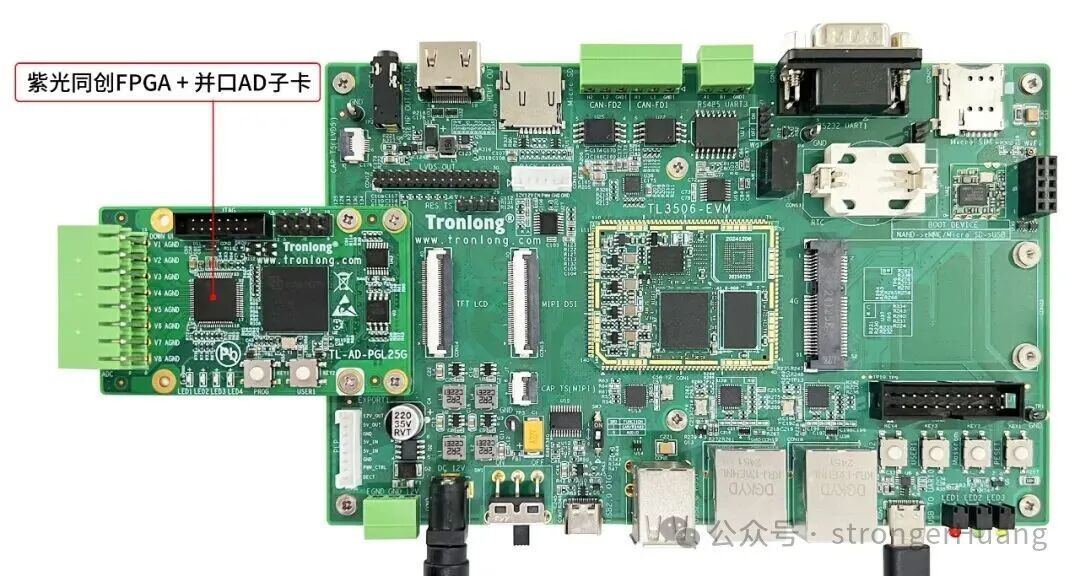

图1:集成FlexBus接口的瑞芯微RK3506评估板

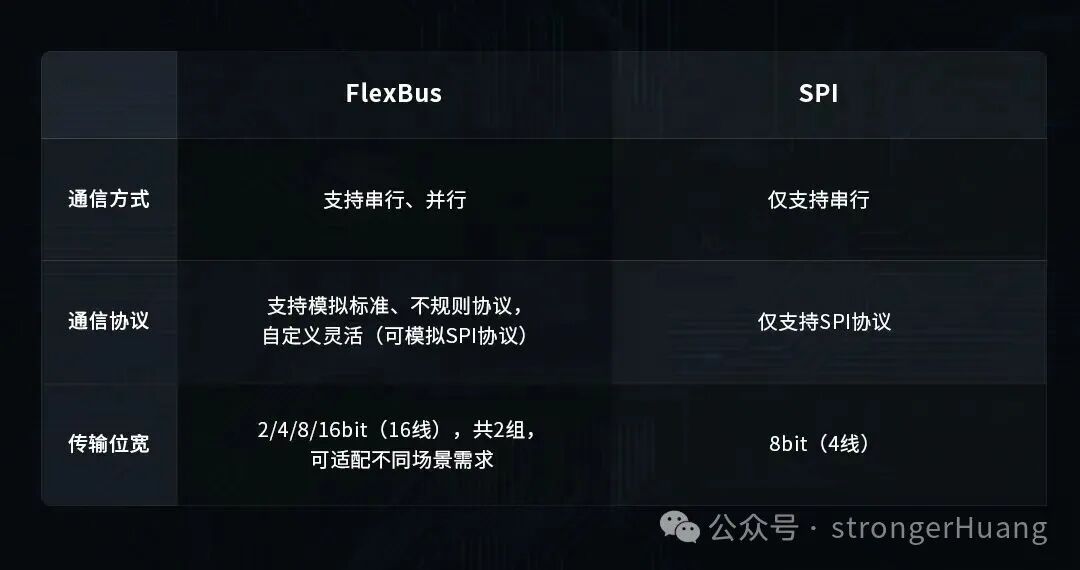

FlexBus与标准SPI的区别

很多人会好奇FlexBus与常见的SPI接口有何不同。尽管在未进行特定协议配置时,FlexBus的工作方式可能与SPI有相似之处,但它是为更复杂的工业场景量身打造的,具备独特优势。

图2:FlexBus与SPI在通信方式、协议和位宽上的对比

简单来说,SPI能实现的功能,FlexBus都可以完成,并且在协议模拟和位宽选择上更加灵活;而在一些SPI受限于固定协议和串行传输的场景中,FlexBus能够提供更好的解决方案,例如直接利用数据线模拟ADC芯片采集所需的复杂控制时序。

FlexBus的典型应用场景

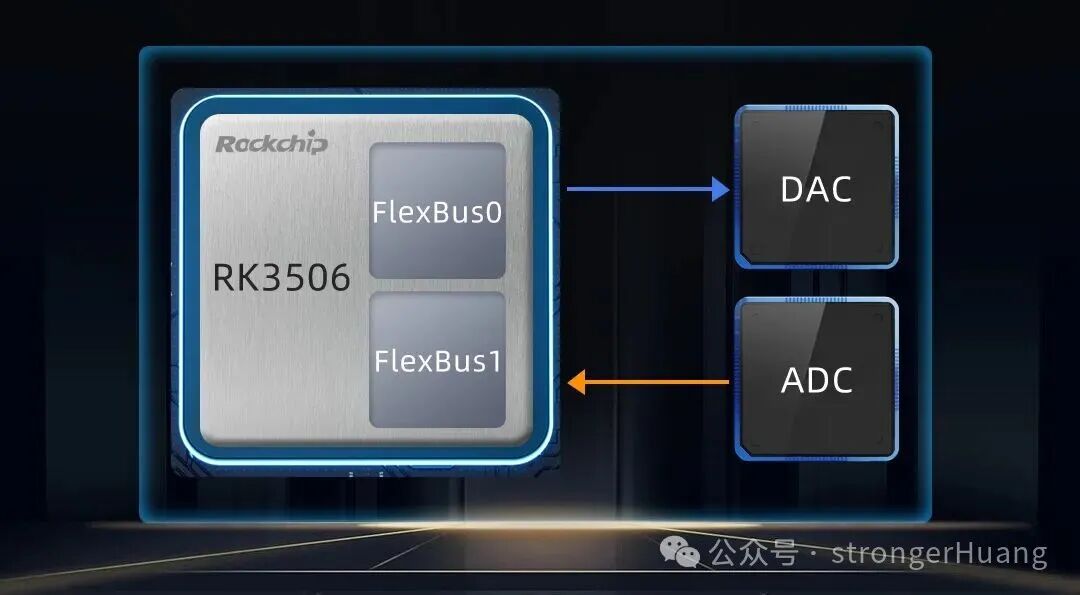

1. 低成本ADC/DAC扩展

FlexBus可用于实现最高200KSPS采样率、8/16通道的数据采集系统,非常适合电力监测、工业传感器信号采集等高精度场景。由于处理器集成了两组独立的FlexBus接口,因此可以同步进行模数(ADC)和数模(DAC)扩展,大大拓宽了应用范围。

图3:RK3506处理器通过FlexBus接口扩展ADC和DAC的示意图

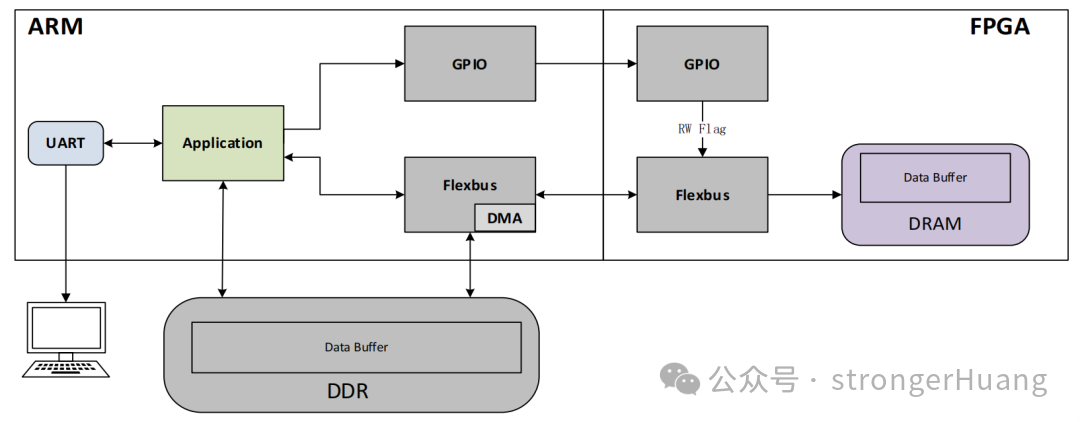

2. 与FPGA的高速数据交互

FlexBus能够实现ARM处理器与FPGA之间的高速并行通信,这在网络与系统通信架构中是一种高效的数据交换方式。

- ARM端:运行Linux系统,可以灵活设置数据包大小、传输循环次数,并对读写数据进行校验,实时监控误码率和传输速率。

- FPGA端:实现FlexBus Slave功能,将ARM端(Master)发送的数据存储至FPGA片内DRAM;当ARM发起读请求时,FPGA再从DRAM中读取数据通过FlexBus回传。

图4:ARM应用处理器与FPGA通过FlexBus及DMA进行高速数据交换的架构图

基于RK3506处理器的实测数据显示,通过FlexBus与FPGA的通信速率可达68MB/s以上,足以满足多数工业应用对传输速率的要求。

备注:RK3506/RK3576的FlexBus接口与DSMC(双倍数据速率存储器控制器)并口复用引脚。如果配置为DSMC并口模式,ARM与FPGA之间的实测通信速率可高达400MB/s以上。

通过上述介绍,我们可以看到瑞芯微FlexBus接口在工业控制、数据采集和异构计算等领域展现出的高度灵活性与强大性能。对于从事相关领域开发的工程师而言,深入了解此类专用接口是构建高效、可靠系统的关键。如果你想了解更多底层通信接口的实现细节或与其他开发者交流经验,欢迎访问云栈社区的相关技术板块。 |