平台: Vivado 2018.3

芯片: xcku115-flva1517-2-i (active)

参考官方文档: Xilinx_Answer_64761_Ultrascale_Devices

利用 PCIe 接口实现 FPGA 的部分重配置,首先需要理解其背后的动机。PCIe 作为一种即插即用的总线协议,要求系统在上电后能快速枚举设备。主机将读取每个设备请求的地址空间大小,并为其分配基地址。因此,在主机查询 PCIe 接口时,相关逻辑必须准备就绪,否则设备将无法被正确识别和寻址。

此外,PCIe 规范明确要求:系统上电后,复位信号必须在 100 毫秒内取消断言,并且 PCIe 端口必须在复位取消后的 20 毫秒内准备好进行链路训练。这通常被称为“100 毫秒启动时间要求”。

为了满足这一严苛的时序要求,Xilinx 提出了 Tandem Configuration(串联配置) 方案。该方案采用两阶段配置方法,并支持多种应用场景:

| 模式 |

描述 |

| Tandem PROM |

从闪存中加载单个包含两个阶段的全位流文件。 |

| Tandem PCIe |

从闪存加载第一阶段位流,然后通过 PCIe 链路将第二阶段位流传输至 MCAP。 |

| Tandem with Field Updates |

在初始 Tandem 配置后,保持 PCIe 链路活动,用于更新整个用户设计。 |

| Tandem + Partial Reconfiguration |

Tandem 配置后,可进行任意大小或数量的部分重配置。 |

| Partial Reconfiguration over PCIe (PR over PCIe) |

标准配置后,使用 PCIe / MCAP 作为部分比特流的传输路径进行动态重构。 |

本文将聚焦于 PR over PCIe 模式,演示如何启用 PCIe 的 MCAP 链路来实现运行时部分逻辑更新。

FPGA 配置方式对比

通常,FPGA 可以通过多种接口进行配置,它们各有特点:

| 接口 |

工作原理与特点 |

| JTAG |

使用专用调试电缆进行烧录,需要物理连接,常用于开发调试。 |

| ICAP |

通过 FPGA 内部的配置访问端口,由 FPGA 自身逻辑控制重配置过程。 |

| MCAP |

主机通过 PCIe 接口直接向 FPGA 发送配置文件,实现远程或系统内编程。 |

使用 MCAP 技术的优势在于,它允许在不中断系统 PCIe 设备枚举、不重启主机的前提下,动态修改 FPGA 的特定功能模块。这非常适合于需要在线升级或功能切换的应用场景。

注意: 这种通过 PCIe MCAP 进行重配置的方式,目前主要支持 UltraScale 及更新系列 的器件。

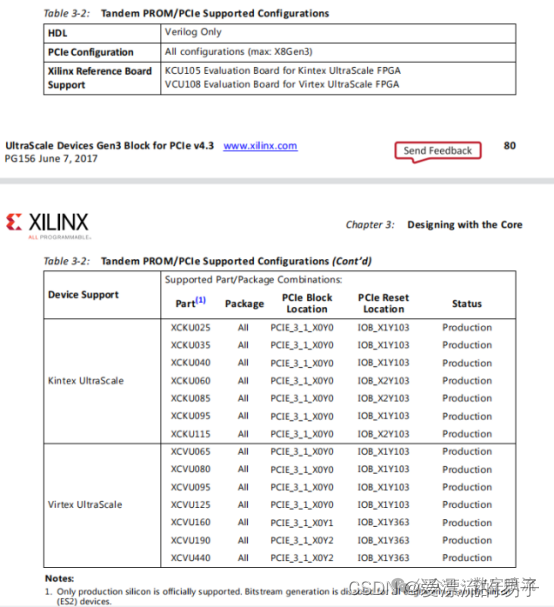

表: 支持 Tandem PROM/PCIe 配置的 UltraScale 器件列表 (摘自 Xilinx PG156)

Tandem PROM 与 Tandem PCIe 流程解析

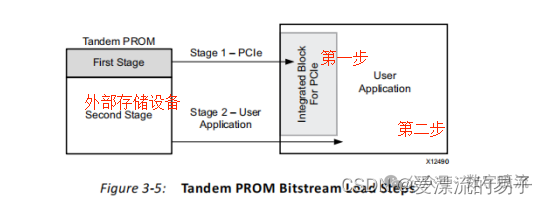

Tandem PROM 方案将完整的位流分割为两部分,均从本地配置存储器(如 PROM)加载。第一部分配置设计的 PCIe 相关逻辑,第二部分配置 FPGA 的其余用户逻辑。

Tandem PROM 配置流程: 第一阶段通过 PCIe 块启动,第二阶段从外部存储加载。

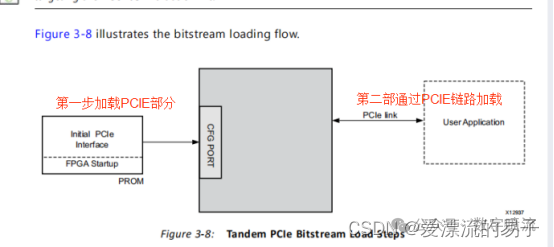

Tandem PCIe 方案与其类似。第一阶段仅配置与 PCIe 操作相关的必要逻辑,使得 PCIe 端口能快速被系统枚举。随后,第二阶段的用户逻辑位流通过已建立的 PCIe 链路进行传输。

Tandem PCIe 配置流程: 第一阶段从 PROM 加载 PCIe 逻辑,第二阶段通过 PCIe 链路加载。

实战: 在 Vivado 中实现 PR over PCIe

以下步骤基于 Vivado 2018.3 和 Kintex UltraScale 器件。

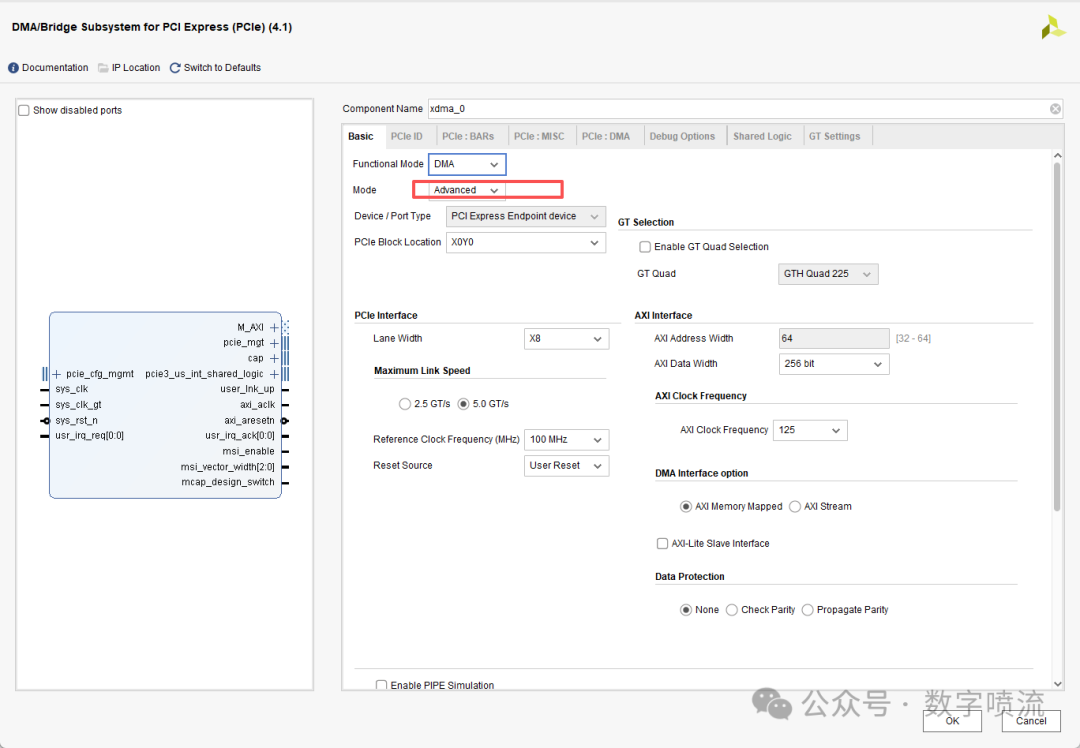

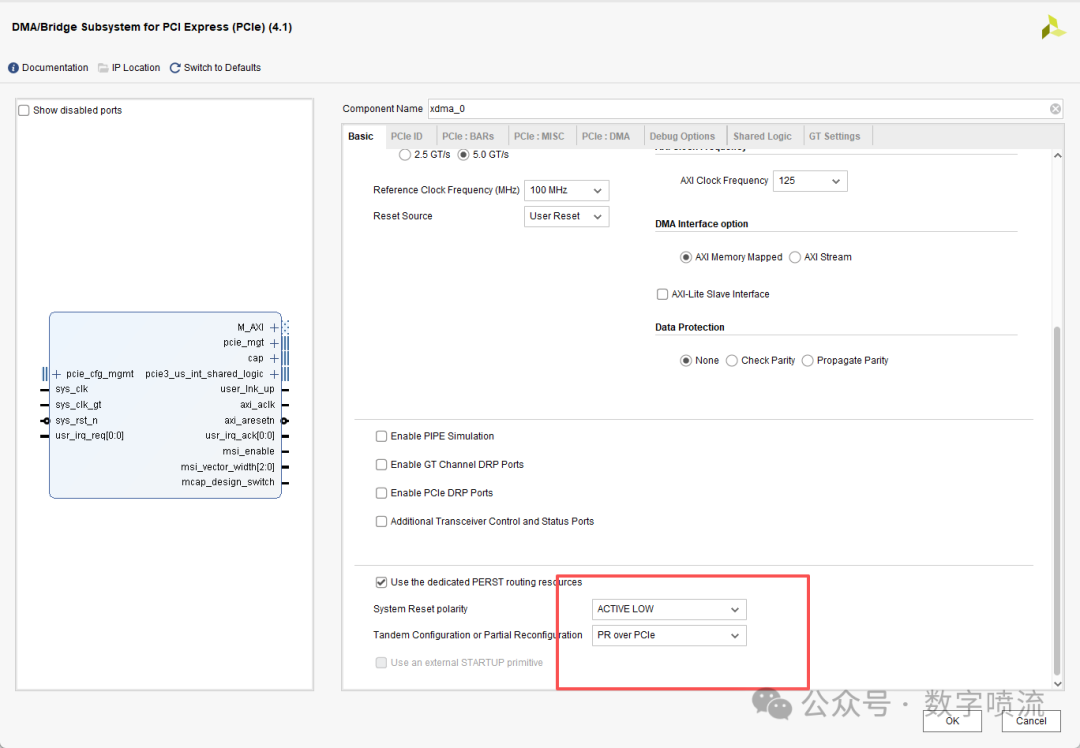

1. 配置 PCIe DMA IP (XDMA)

在 IP Catalog 中打开 “DMA/Bridge Subsystem for PCI Express (PCIe)”。

- 将 Functional Mode 设置为

DMA。

- 在 Basic 标签页下的 Tandem Configuration or Partial Reconfiguration 选项中,选择

PR over PCIe。

- 根据硬件连接,配置合适的 Lane Width、Max Link Speed 和 Reference Clock。

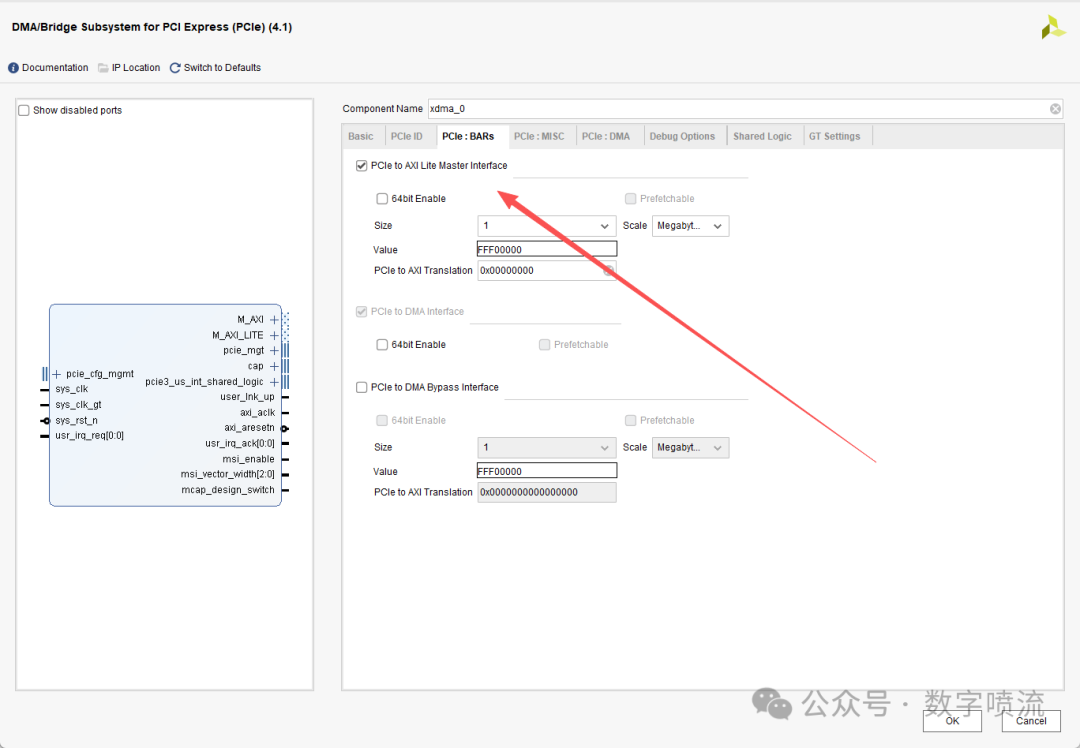

- 在 PCIe ID 标签页中,启用 PCIe to AXI Lite Master Interface,用于实现主机对 FPGA 内寄存器的读写控制。

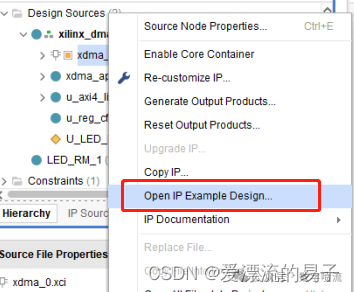

完成 IP 定制后,右键点击该 IP,选择 “Open IP Example Design” 创建一个示例工程。

2. 添加用户自定义逻辑

在打开的示例工程中,添加自己的 AXI4-Lite 接口转换模块、寄存器控制模块,以及用于部分重配置的模块。本例创建两个可重配置模块:LED_RM_0 和 LED_RM_1。

LED_RM_0: 输出固定的 2‘b00。LED_RM_1: 输出固定的 2‘b11。

LED_RM_0 模块的核心代码如下:

module LED_RM_0(

input wire sys_clk,

input wire rst_n,

output reg [1:0] led

);

always @ (posedge sys_clk or negedge rst_n) begin

if(rst_n == 1'b0)

led <= 2'b0;

else

led <= 2'b0; // 输出 00

end

endmodule

LED_RM_1 模块中,仅需更改 always 块内的赋值语句:

always @ (posedge sys_clk or negedge rst_n) begin

if(rst_n == 1'b0)

led <= 2'b0;

else

led <= 2'b11; // 输出 11

end

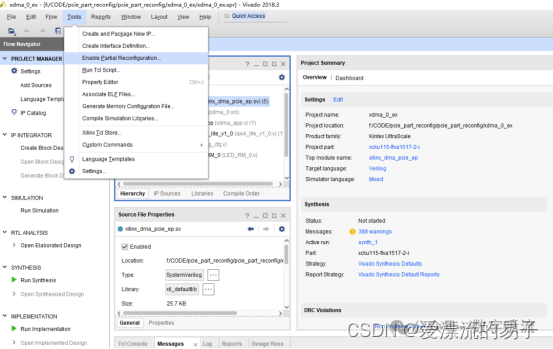

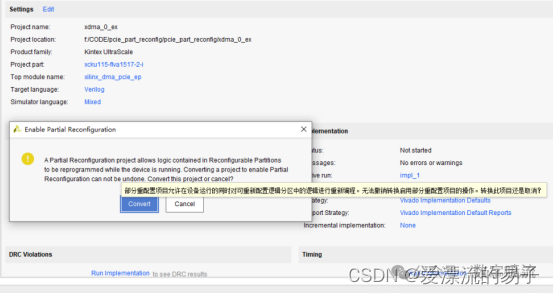

3. 启用部分重配置功能

在 Vivado 菜单栏,点击 Tools -> Enable Partial Reconfiguration。

在弹出的对话框中确认转换工程。

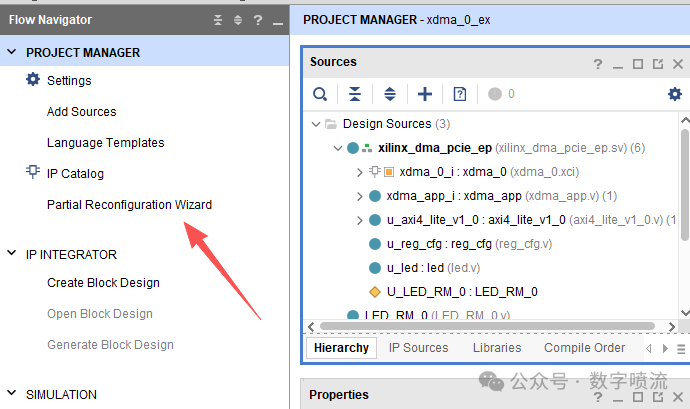

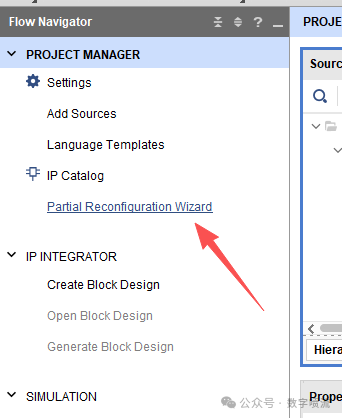

启用后,在 Flow Navigator 的 PROJECT MANAGER 下会出现 Partial Reconfiguration Wizard 选项。

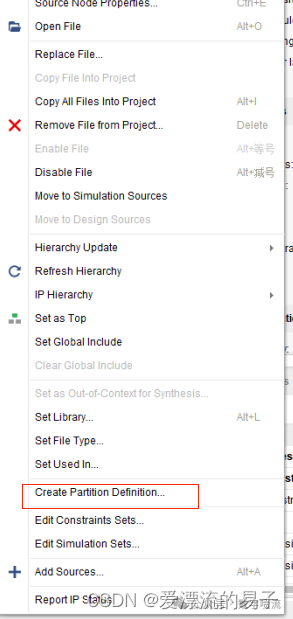

4. 定义可重配置分区

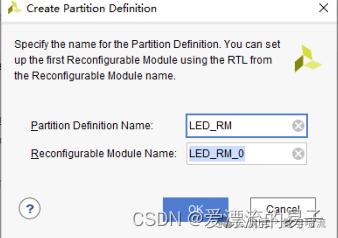

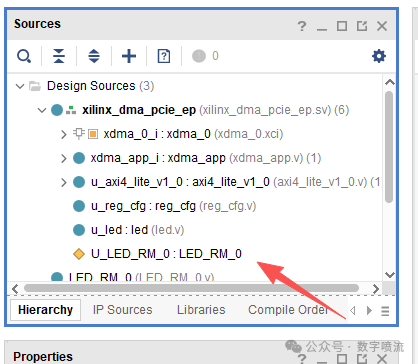

在 Sources 窗口中,右键点击要重配置的模块(如 LED_RM_0),选择 Create Partition Definition...。

为分区指定一个名称,例如 LED_RM。

创建成功后,该模块在层次结构中的图标会变为菱形,表示它是一个可重配置分区。

5. 使用 Partial Reconfiguration Wizard 进行配置

打开 Partial Reconfiguration Wizard。

介绍向导功能的初始页面。

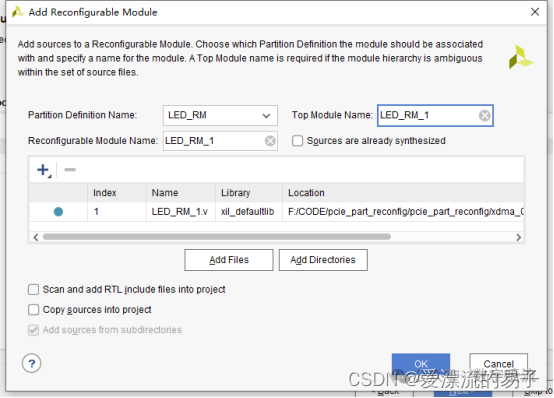

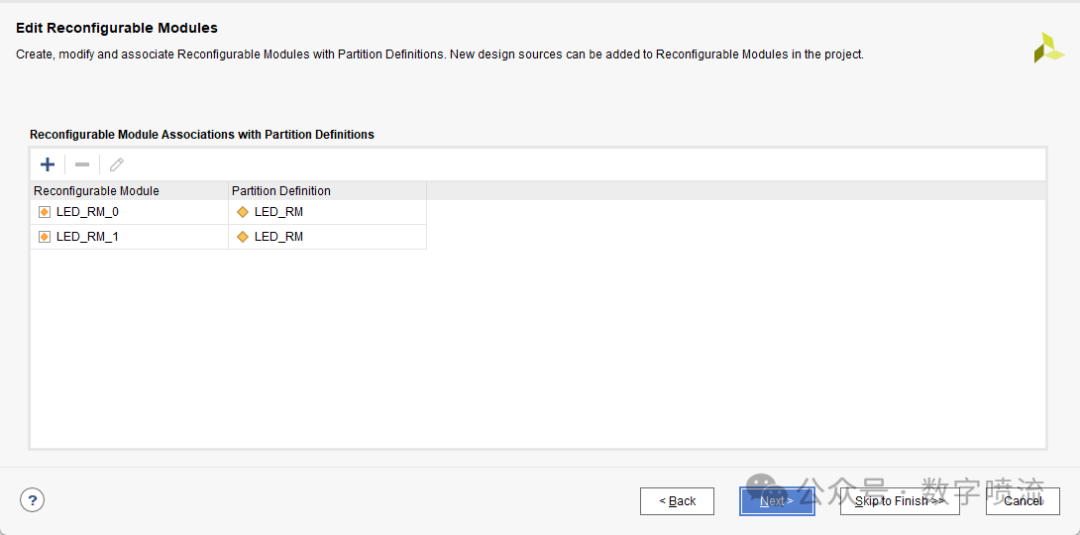

- 添加可重配置模块: 在

Reconfigurable Modules 步骤,为之前创建的 LED_RM 分区添加另一个模块 LED_RM_1。

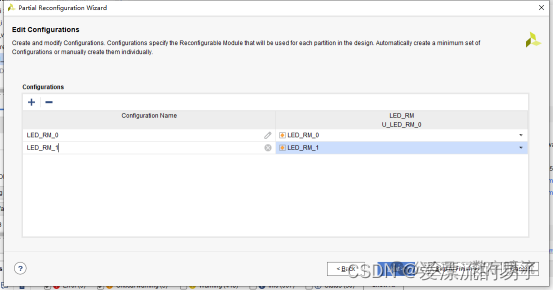

- 创建配置: 在

Configurations 步骤,点击 “+” 号自动创建配置。系统会为每个可重配置模块生成一个配置(如 LED_RM_0, LED_RM_1)。

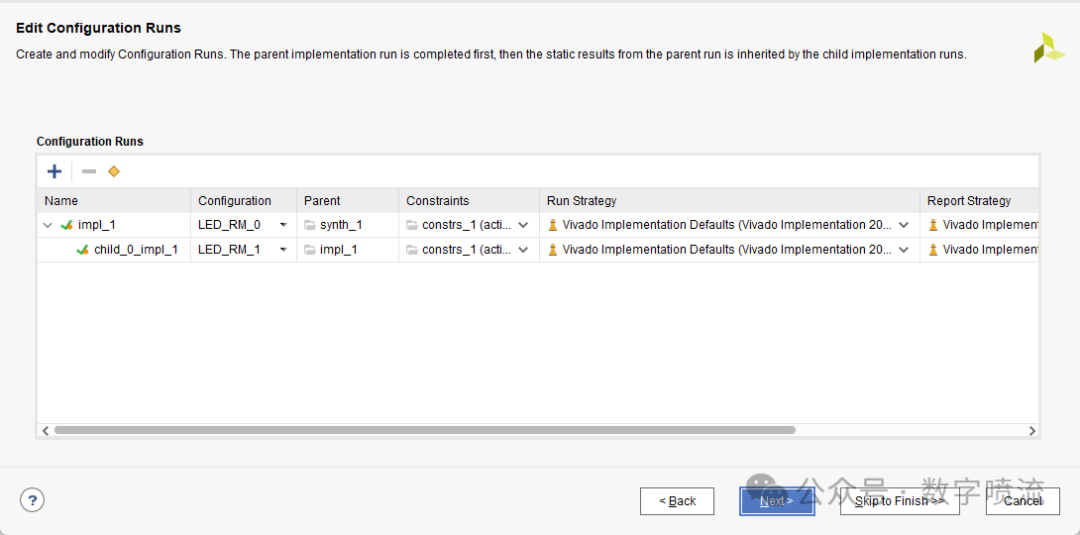

- 创建配置运行: 在

Configuration Runs 步骤,再次点击 “+” 号自动创建运行。这将生成一个父运行(impl_1,对应初始配置)和一个子运行(child_0_impl_1,对应重配置)。

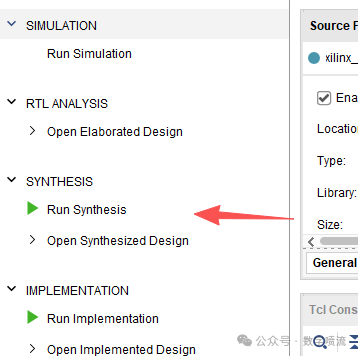

6. 综合与布局规划

完成向导配置后,运行综合(Run Synthesis)。

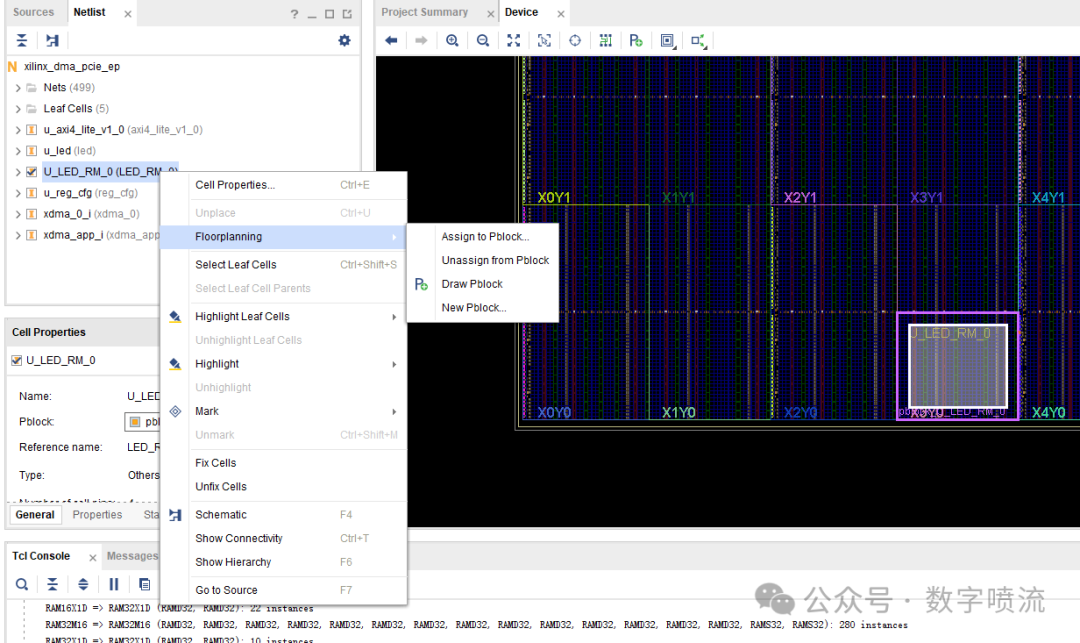

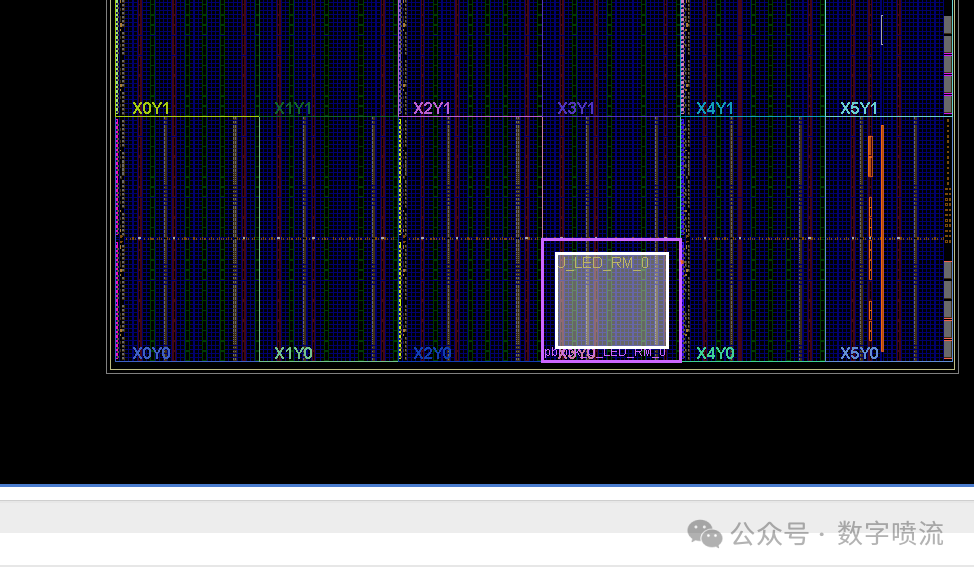

综合完成后,打开综合后的设计(Open Synthesized Design)。在 Netlist 窗口中选中可重配置模块实例(如 U_LED_RM_0),右键选择 Floorplanning -> Draw Pblock,在芯片视图上框选一个物理区域作为该可重配置模块的专属位置。

绘制一个合理的区域,确保资源充足且不影响静态逻辑。

此操作会自动在约束文件(XDC)中添加 Pblock 约束。

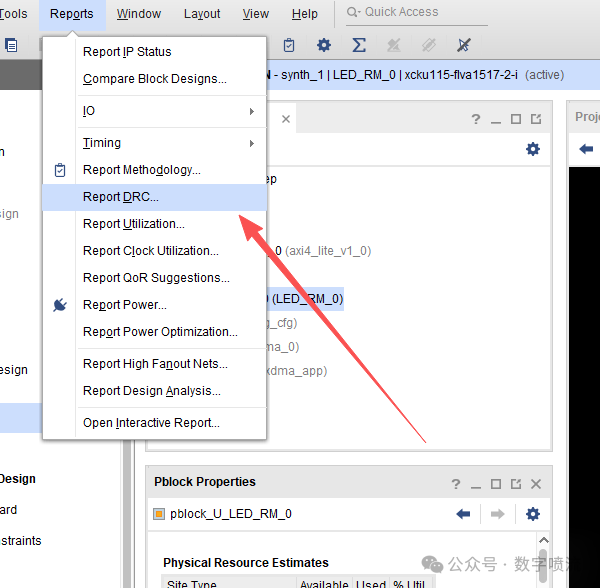

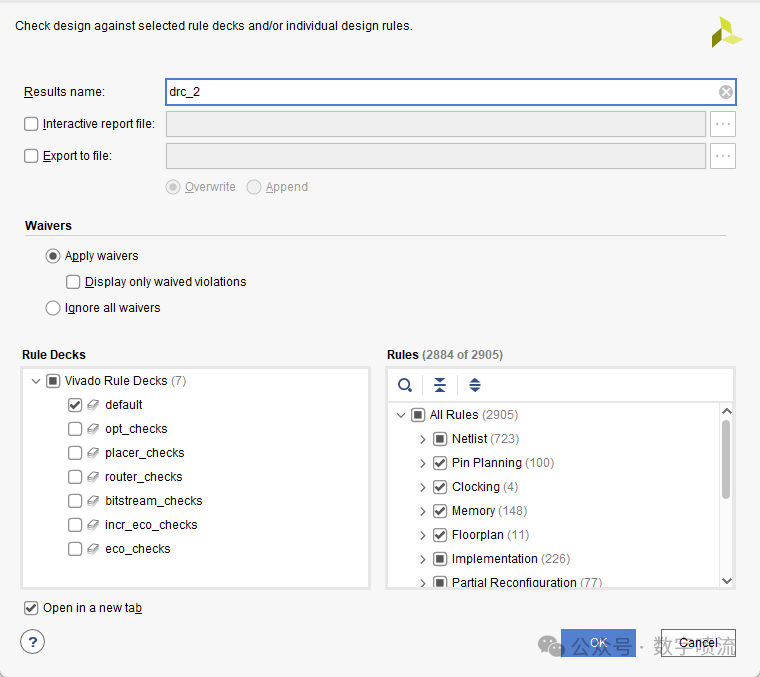

7. 设计规则检查 (DRC)

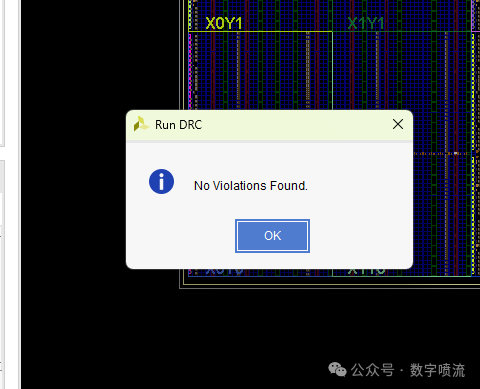

在菜单栏选择 Tools -> Report -> Report DRC...,检查部分重配置相关的设计规则,确保 Pblock 设置和设计符合要求。

如果一切设置正确,DRC 报告应显示无冲突。

8. 实现设计与生成比特流

运行实现(Run Implementation)并生成比特流(Generate Bitstream)。

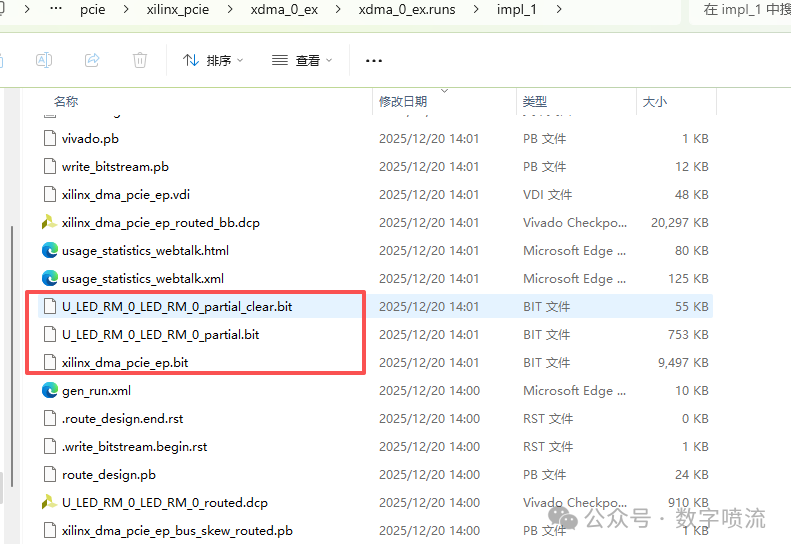

生成完成后,在工程 impl_1 目录下可以找到以下关键文件:

xilinx_dma_pcie_ep.bit: 静态比特流,包含整个设计的静态逻辑和初始可重配置模块。U_LED_RM_0_LED_RM_0_partial.bit: 部分比特流,对应 LED_RM_0 模块的逻辑。U_LED_RM_0_LED_RM_0_partial_clear.bit: 清除比特流,用于将可重配置区域清空。

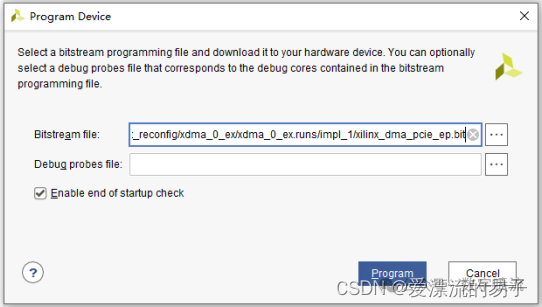

首先,使用 Vivado Hardware Manager 将 静态比特流 (xilinx_dma_pcie_ep.bit) 下载到 FPGA 中。

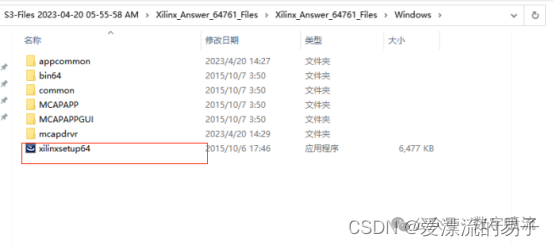

安装与使用 MCAP 配置工具

动态重配置需要通过主机上的 MCAP 驱动和工具完成。工具在官方文档 Xilinx_Answer_64761 的附件中提供。

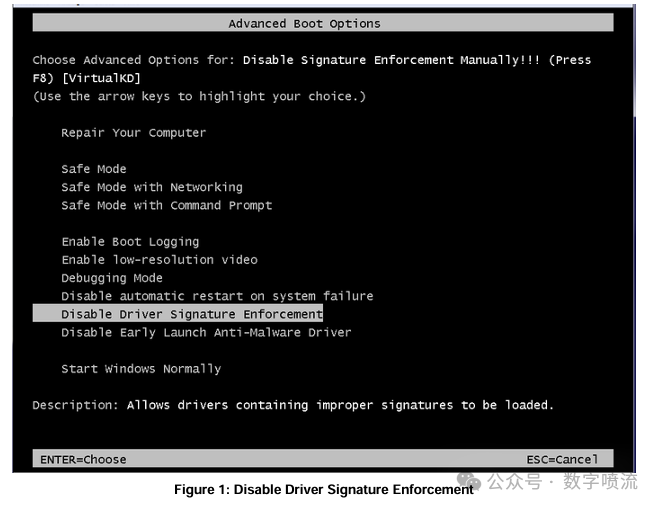

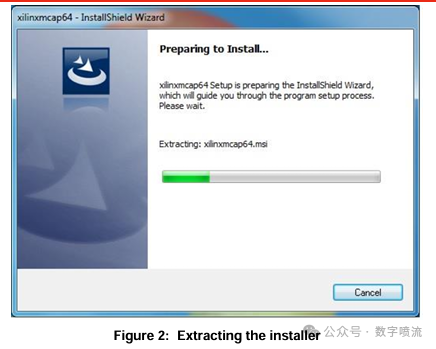

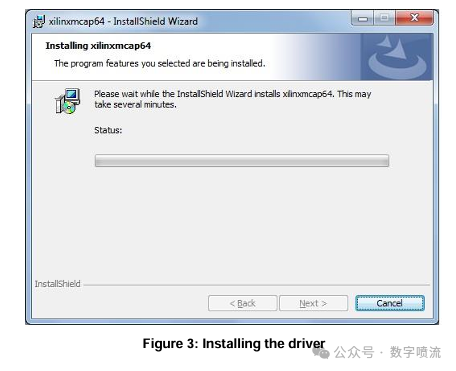

安装注意事项:

- 该驱动适用于 Windows 7 64位系统。

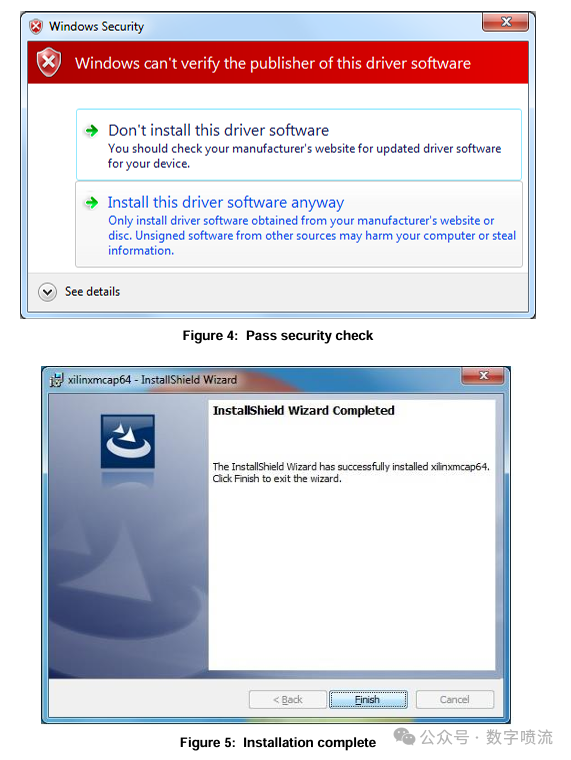

- 安装前需在系统启动时 禁用驱动程序强制签名(开机按 F8 选择)。

- 按照提示安装

xilinxmcapi64 程序包,遇到安全警告时选择“始终安装此驱动程序软件”。

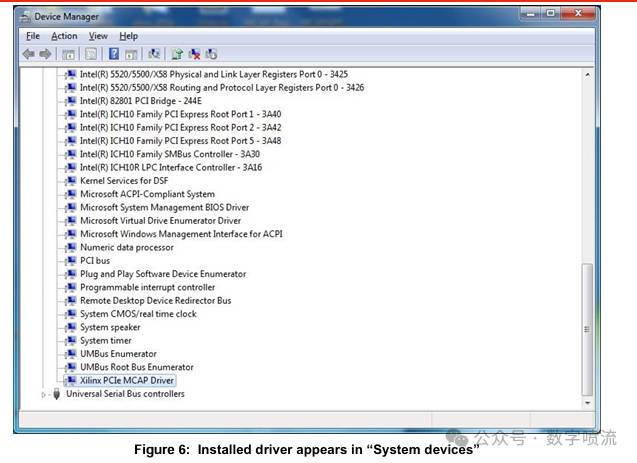

安装成功后,在设备管理器的“系统设备”中可以看到 Xilinx PCIe MCAP Driver。

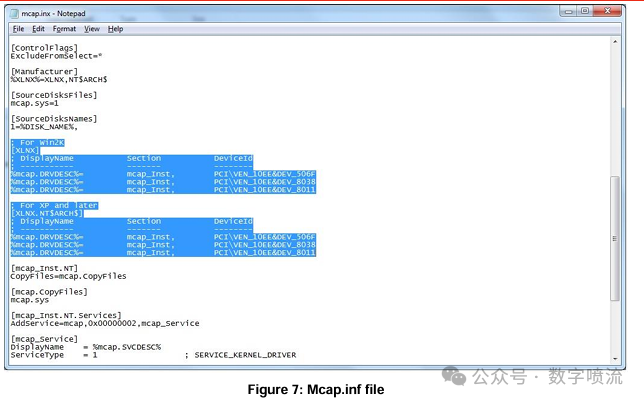

添加自定义设备ID:

如果您的 FPGA 设备 ID 不在默认列表中,可以编辑驱动安装目录下的 mcap.inf 文件(默认路径:C:\Program Files (x86)\Xilinx\MCAP\mcap64),参照已有格式添加您的 VEN_XXXX&DEV_YYYY。

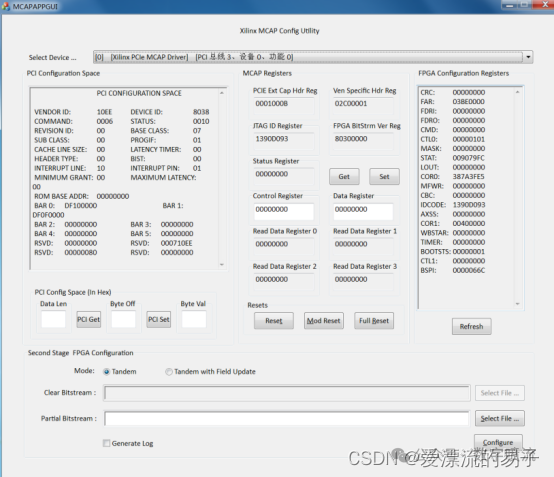

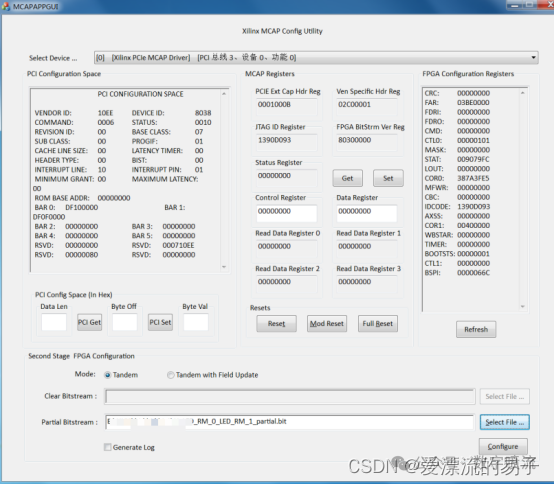

使用 GUI 工具进行重配置:

安装后,运行 MCAPAPPGUI.exe。

- 选择已枚举的 FPGA 设备。

- 在 Second Stage FPGA Configuration 部分,选择 Tandem with Field Update 模式。

- 点击 Select File...,浏览并选择生成的部分比特流文件(如

U_LED_RM_0_LED_RM_1_partial.bit)。

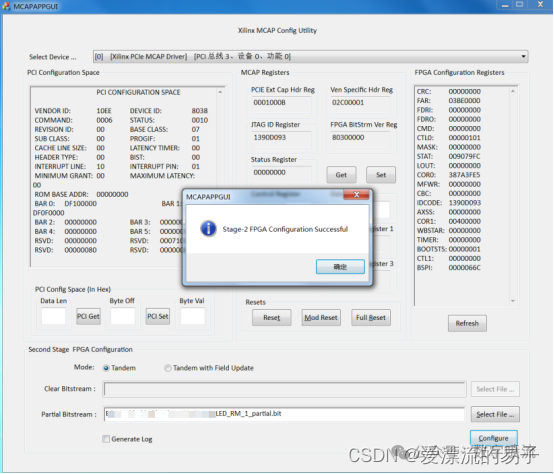

- 点击 Configure 按钮。

配置成功后,工具会弹出提示。

验证重配置效果

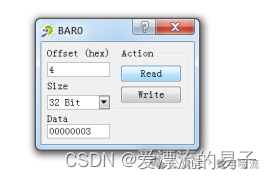

在本例中,我们设计了两个可重配置模块(LED_RM_0 和 LED_RM_1),它们通过一个映射到 PCIe BAR0 空间的寄存器输出不同的值。我们可以借助 Computer Science 中的总线访问原理,使用 Windriver 或类似工具来读取该寄存器的值,以验证重配置是否生效。

- 初始配置(

LED_RM_0)时,读取 BAR0 + 0x4 地址,值应为 0x00000000。

- 通过 MCAP 工具加载

LED_RM_1 的部分比特流后,再次读取同一地址,值应变为 0x00000003。

这种验证方式直观地证明了 FPGA 内部的逻辑在系统持续运行、PCIe链路保持活跃的情况下,已经发生了动态改变。

总结

通过上述步骤,我们完成了基于 Xilinx UltraScale FPGA 和 PCIe MCAP 接口的部分重配置全流程。该技术的关键在于利用 Tandem PCIe 或 PR over PCIe 模式满足启动时序,并通过 Vivado 的 Partial Reconfiguration Wizard 规范地管理可重配置模块与物理约束。最终,结合官方 MCAP 驱动工具,实现了在操作系统层面的远程动态功能更新。

这个过程涉及从硬件描述语言编码、EDA工具流程到驱动软件使用的完整链条,是深入理解现代 FPGA 动态可重构系统的一个绝佳实践。如果在实践过程中遇到问题,欢迎到 云栈社区 的对应板块与广大开发者交流讨论。