计算机系统常被类比为人体,而CPU (Central Processing Unit)正是其核心大脑,负责处理所有计算任务。

从智能手机的骁龙、苹果A系列芯片,到个人电脑的Intel酷睿、AMD锐龙处理器,这些微小的硅片决定了设备的运行效率。你是否曾好奇,这个指甲盖大小的组件内部是如何工作的?今天,我们将深入拆解CPU,从基础模块到架构设计,带你掌握计算机的核心原理。

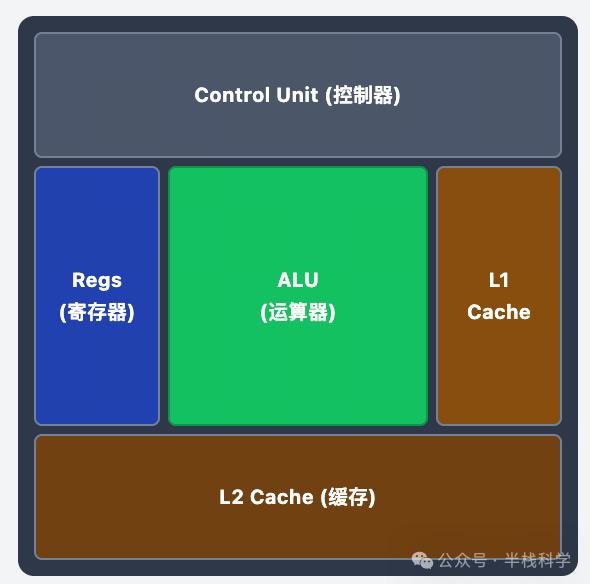

CPU的核心组成模块

现代CPU虽包含数百亿个晶体管,但其功能可简化为几个关键部分。点击下方图解,了解每个模块的作用。

1. 控制单元 (Control Unit)

控制单元如同交响乐团的指挥,不直接参与计算,而是负责读取指令、解码并协调其他部件工作。它决定数据流向和下一步操作,确保各模块有序运行。

2. 寄存器 (Registers)

寄存器是CPU内部速度最快、容量最小的存储单元,类似手边的草稿纸,存放立即参与计算的数据。其访问速度极快,通常不足一个时钟周期。

3. 算术逻辑单元 (ALU)

ALU是CPU中的计算核心,专门处理算术运算(如加减乘除)和逻辑运算(如与或非)。所有实际计算任务都在这里完成。

4. 高速缓存 (L1/L2 Cache)

高速缓存位于CPU与内存之间,作为数据缓冲区,预先加载CPU可能需要的指令和数据。L1缓存速度最快但容量最小,L2和L3缓存稍慢但容量更大。没有缓存,CPU将大量时间浪费在等待内存数据传输上。

冯·诺依曼架构与哈佛架构对比

CPU设计有两种经典范式,它们定义了指令和数据的存储与访问方式。

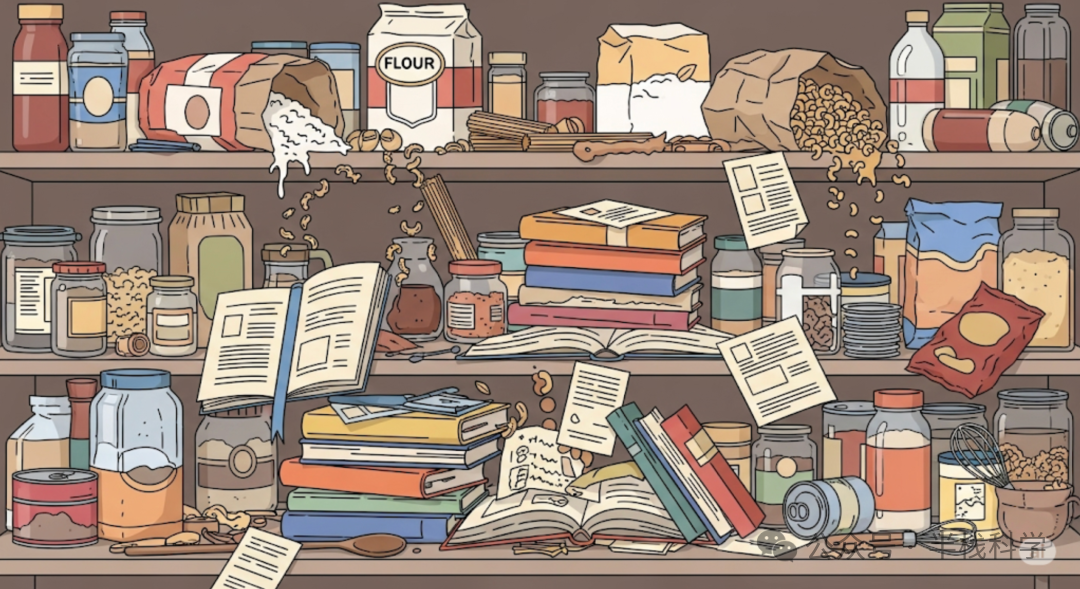

冯·诺依曼架构

核心特点:指令和数据共享同一内存空间和总线。

比喻:想象一个厨房,食材(数据)和菜谱(指令)混放在同一个柜子里。每次只能取一件物品,要么拿菜谱,要么取食材,无法并行操作。

缺点:容易形成性能瓶颈,CPU高速计算能力受限于单一总线的数据传输速度。

哈佛架构

核心特点:指令和数据分别存储于独立的内存单元,并通过分离的总线传输。

比喻:厨房设有两个专用柜子,一个存放食材,另一个存放菜谱。可以同时左手拿菜谱、右手取食材,效率显著提升。

应用场景:常见于数字信号处理器(DSP)和嵌入式单片机系统。

现代架构的融合: 当前PC和移动设备多采用改进型哈佛架构。在外部内存层面,它呈现冯·诺依曼特征(统一存储);而在CPU内部(如L1缓存),指令和数据分开存储,兼顾了性能与成本效益。

指令集设计:RISC与CISC之争

RISC (精简指令集计算机)

- 特点:指令数量少、格式固定、执行速度快

- 优势:功耗低、适合移动设备和嵌入式系统

- 代表:ARM架构(广泛用于手机、平板)

CISC (复杂指令集计算机)

- 特点:指令丰富、功能复杂、单指令完成多操作

- 优势:代码密度高、向后兼容性好

- 代表:x86架构(主导PC和服务器市场)

技术融合趋势: 随着硬件发展,RISC与CISC界限逐渐模糊。x86架构在内部将复杂指令拆解为微指令执行,而ARM架构也逐步增加指令复杂度以提升性能。

未来发展方向:异构计算与先进封装

传统CPU核心已无法满足多样化的计算需求,2024-2025年的焦点转向异构计算。

-

NPU (神经网络处理器)

NPU 专为AI大模型优化,如Intel Core Ultra和Apple M3/M4芯片中的NPU模块,能够高效处理矩阵运算,同时保持极低功耗。

-

小芯片技术 (Chiplets)

采用模块化设计,将不同工艺制造的CPU、GPU和I/O单元封装在一起,类似拼装乐高,降低成本并提高生产良率。

-

3D堆叠技术

如AMD的3D V-Cache,直接在CPU核心上垂直堆叠缓存层,大幅提升游戏和专业应用的性能表现。

|