在芯片验证的世界里,UVM(Universal Verification Methodology)搭建了一座精密的验证工厂。而其中的Driver组件,就如同生产线上最关键的一线“操作员”——它负责将抽象的、高层级的交易(transaction)转化为真实的、符合时序的物理信号,从而驱动被测设计(DUT, Design Under Test)运行。

可以说,精准驾驭数据流是验证成败的关键,而Driver正是实现这一目标的“灵魂车手”。

Driver的核心职责:协议与信号的翻译官

在UVM验证环境中,Driver扮演着严格的协议实现者角色。它的核心任务非常明确,主要集中在以下三个方面:

- 协议转换:将

sequence item(一种封装了抽象数据的类)所承载的信息,翻译并驱动到DUT物理接口上,形成具体的信号波形。

- 时序控制:严格遵循总线或接口协议的时序要求,在正确的时钟周期驱动或采样信号,模拟真实环境。

- 流量控制:与上层的

Sequencer协同工作,控制数据包的发送节奏,防止数据过载或饥饿,这对于软件测试场景下的异常压力测试尤为重要。

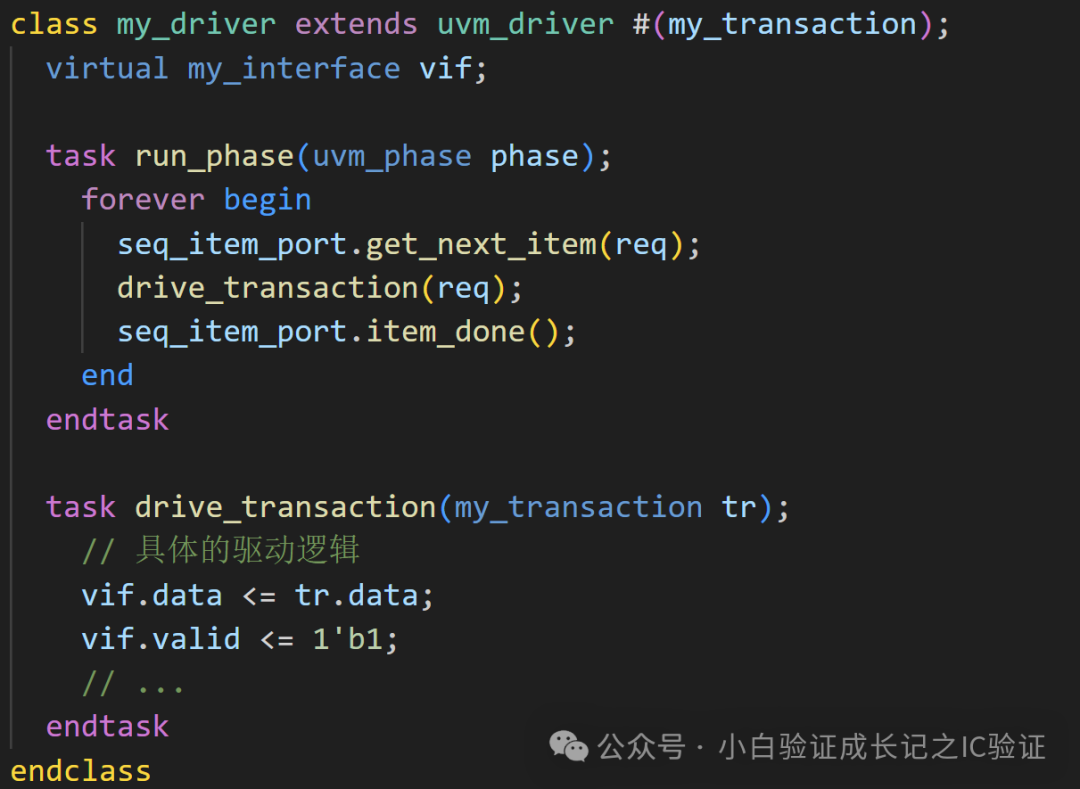

其典型的结构如下所示,它继承自uvm_driver基类,并通过虚拟接口(virtual interface)与DUT的实际引脚相连。

协作架构:与Sequencer的高效流水线

Driver并非孤立工作。它通过TLM(Transaction Level Modeling)端口与Sequencer紧密连接,形成一个高效的生产者-消费者模型:

Sequence → Sequence Item → Sequencer → Driver → DUT

这种架构带来了显著的优点:

- 解耦:激励生成(

Sequence)的逻辑与具体的驱动(Driver)逻辑分离,两者可以独立开发和维护。

- 灵活性:无需修改

Driver,通过更换不同的Sequence即可动态改变测试场景和激励序列。

- 可重用性:一个设计良好的

Driver可以被不同的测试用例和验证环境复用,提高了验证组件的利用率。

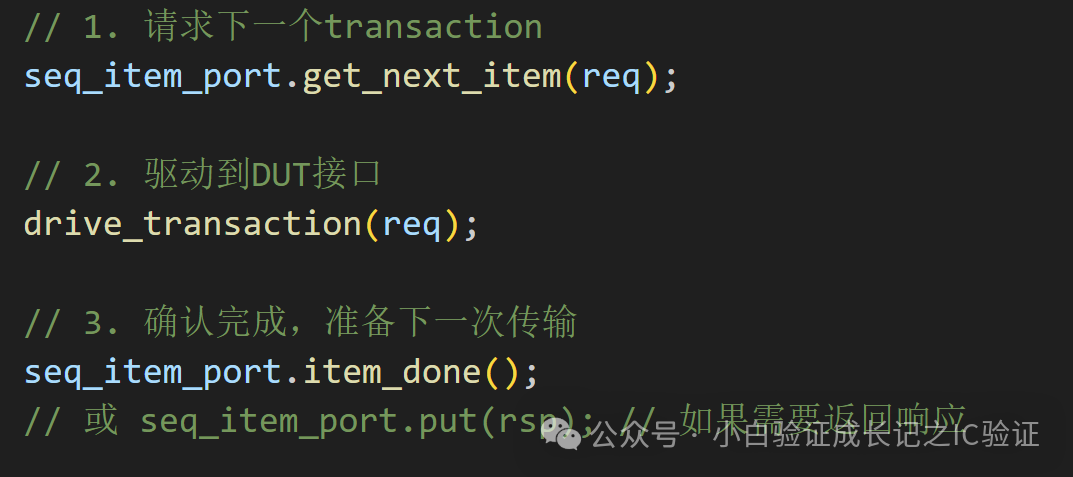

交互“三步曲”:Driver的工作循环

Driver与Sequencer的每一次数据交互都遵循一个精密而固定的流程,通常在其主要的run_phase任务中通过一个forever循环实现。这个过程可以清晰地分解为三个步骤:

- 请求事务:通过

seq_item_port.get_next_item(req)方法,向连接的Sequencer申请下一个需要驱动的transaction对象。

- 驱动事务:调用用户自定义的

drive_transaction(req)任务,将transaction中的数据按照协议时序,驱动到虚拟接口vif的信号上。

- 完成确认:使用

seq_item_port.item_done()通知Sequencer当前事务已处理完毕。如果需要向Sequence返回响应,也可以使用seq_item_port.put(rsp)。

Driver设计的最佳实践

要构建一个健壮、可重用且易于调试的Driver,需要遵循一些关键的设计原则:

- 保持职责单一:Driver只负责信号驱动,切勿在其中嵌入激励生成或检查逻辑。

- 协议参数化:将协议中的时序参数(如时钟周期、建立保持时间)定义为可配置变量,便于策略调整和维护。

- 支持多种模式:通过UVM的

config_db机制,使Driver能够灵活配置为正常、错误注入、性能监测等不同工作模式,这对构建全面的运维 & 测试流程很有帮助。

- 增强可调试性:在关键节点添加合理的

uvm_info调试信息和功能覆盖点(coverpoint),方便问题定位。

- 健壮的错误处理:设计优雅的异常处理机制,例如处理协议错误或超时,避免验证环境陷入死锁。

总结

UVM Driver虽处于验证环境的最“底层”,直接与硬件接口打交道,但却是确保验证准确性和高效性的基石。一个优秀的Driver设计,就如同一位技艺精湛的赛车手,必须对“赛道”(接口协议)了如指掌,对“赛车”(DUT特性)性能心中有数,方能在复杂的验证场景中精准操控数据流。

深入理解并掌握Driver的设计精髓,意味着你将从被动的验证执行者,转变为主动的环境掌控者。如果你对UVM或芯片验证的其他方面有更多疑问,欢迎在云栈社区与其他开发者交流探讨,共同驱动前沿技术的验证实践。 |