在高速PCB的布局评审过程中,针对USB3.0这类背面接口区域的参考平面是否需要“掏空”处理,设计团队内部时常会产生分歧。今天,我们就结合大厂的规范要求,深入探讨一下这个关乎信号稳定性的设计细节。

大厂对高速接口的设计要求

对于USB3.0、HDMI、PCIe、SATA等高速信号接口的设计,主流芯片厂商的规范通常有明确要求。

-

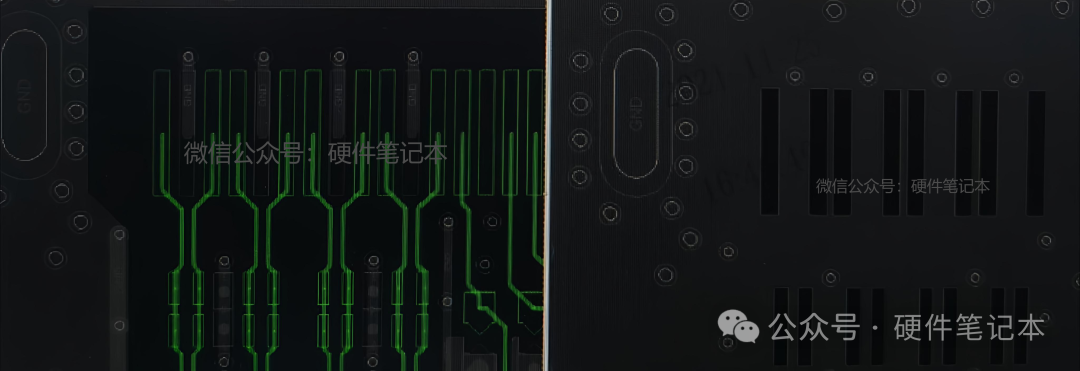

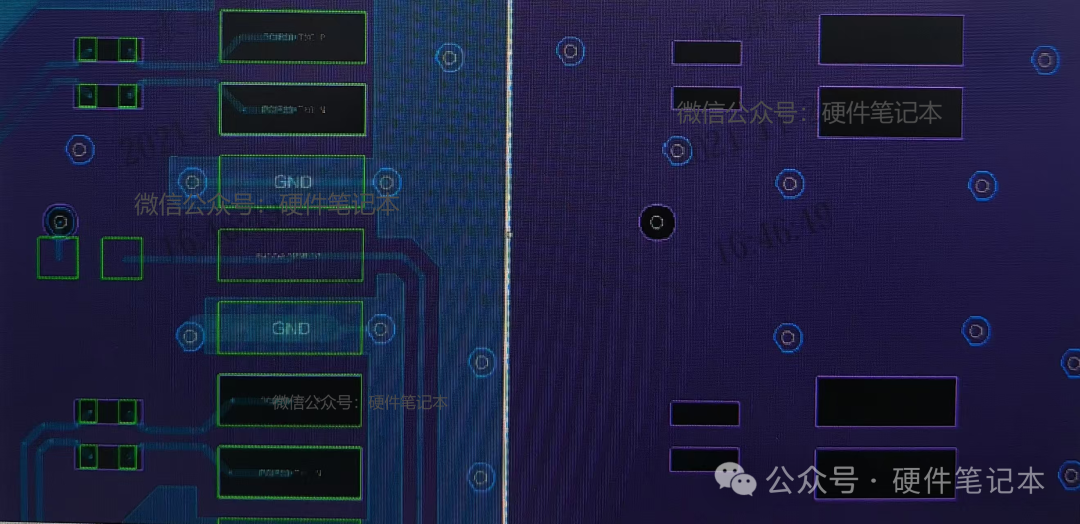

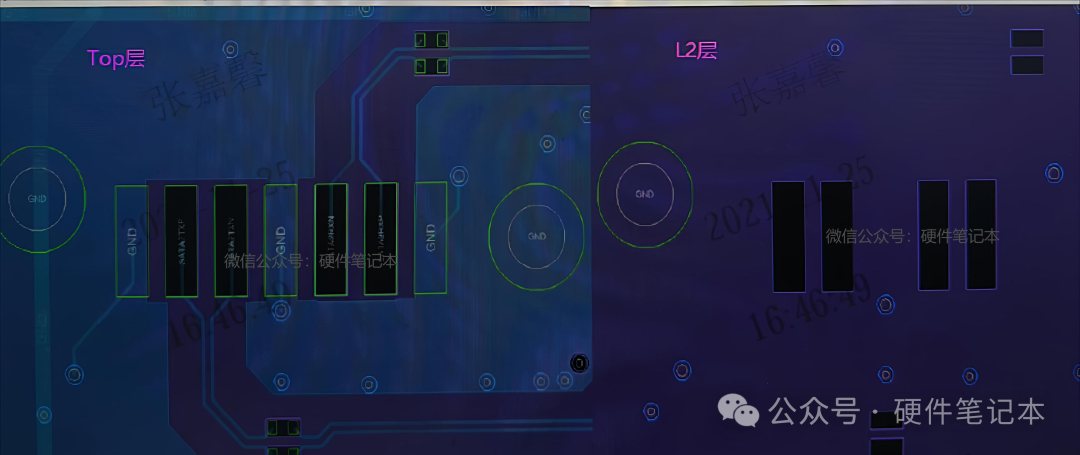

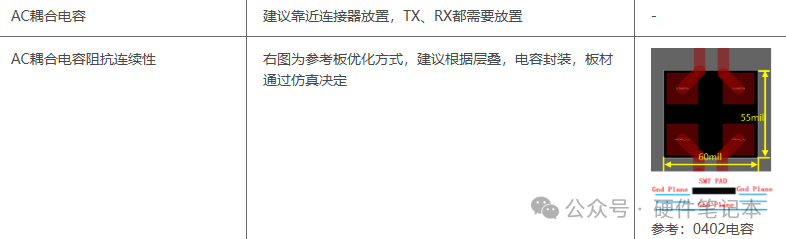

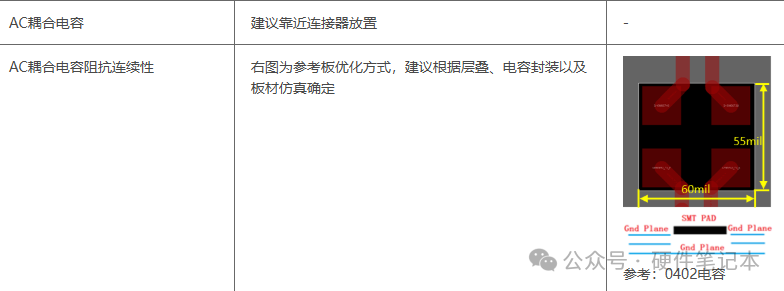

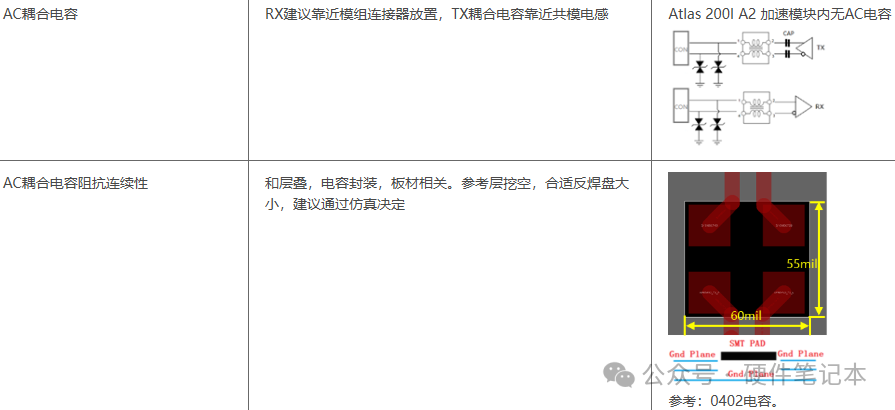

USB3.0接口:连接器焊盘以及AC耦合电容焊盘的正下方,必须将相邻的参考层(通常是GND层)挖空,以确保传输线阻抗的连续性。挖空区域的尺寸不应小于封装焊盘本身的尺寸。

-

HDMI接口:连接器焊盘以及用于静电防护的TVS管焊盘下方,同样需要挖空一层参考层以保证阻抗连续,挖空尺寸不小于焊盘尺寸。

-

PCIe接口:插槽焊盘和AC耦合电容焊盘下方需进行参考层挖空处理,尺寸要求同上。

-

SATA接口:连接器焊盘和AC耦合电容焊盘下方也需遵循相同的挖空规则。

从原理上理解参考层挖空的要求

为什么需要挖空参考层?

如上所述,各大厂规范的核心目的都是为了维持阻抗连续性。像HDMI 2.1速率高达12Gbps的信号,对阻抗波动异常敏感。焊盘及TVS管焊盘区域容易引起阻抗突变,主要原因有二:

- 焊盘厚度增加:相较于纤细的传输线,焊盘更厚,导致该区域的局部电容增大,从而引起阻抗下降。

- TVS管寄生电容:TVS(静电放电保护)器件本身存在寄生电容(典型值在0.5pF到2pF之间),在高频下会进一步拉低信号路径的阻抗。

为了应对这些导致阻抗降低的因素,挖空紧邻的参考层(GND或电源平面)就成为一个关键对策:

- 减少寄生电容:移除了参考层,焊盘与平面之间的耦合电容显著减小,从而补偿了因焊盘变厚或TVS管引入的额外容性负载。

- 维持阻抗匹配:最终目的是让信号在整个路径上看到的阻抗尽可能接近设计目标值(例如差分90Ω或100Ω)。

下图汇总了各高速接口的传输线阻抗设计要求及对应的优化建议示意图:

为什么挖空尺寸必须≥焊盘尺寸?

这主要基于两点考虑:

- 电场分布影响:高速信号的电场并非严格局限在焊盘正下方,会向周围扩散(边缘场效应)。如果挖空区域小于焊盘,参考层的边缘仍会与焊盘边缘的电场发生耦合,引入不必要的寄生电容。

- 制造公差考虑:PCB加工存在层与层之间的对位误差。将挖空区域设计得略大于焊盘,可以确保在实际生产中,挖空范围能够完全覆盖焊盘区域,避免因对位偏差导致部分焊盘下方仍有参考层。

总结来说,在高速接口的焊盘和TVS管下方挖空参考层,本质是通过精细控制电磁场分布来优化传输线阻抗连续性,是保障高速信号完整性的一个关键且有效的设计手段。 这一规范背后涉及对计算机体系结构中信号与系统深层次原理的应用。

参考链接:

https://support.huawei.com/enterprise/zh/doc/EDOC1100304822/16ac287

希望这篇针对具体设计规范的分析,能为大家在高速PCB设计,特别是布局规划时提供清晰的参考。在实际工程中,除了遵循通用规则,结合具体的叠层结构、板材和封装使用仿真工具进行验证,往往是达到最佳性能的必要步骤。如果你在硬件设计中有其他心得或疑问,欢迎在云栈社区的技术板块与我们进一步交流探讨。 |