今天咱们来聊聊一个让不少硬件工程师朋友又爱又恨的话题——EMC(电磁兼容)。无论是新手设计第一块板子,还是老手迭代成熟产品,EMC整改测试往往都是项目周期里最耗心力、最容易“踩坑”的环节。最近,我看到一份由赛元官方整理的《EMC性能优化指南》,内容颇为扎实,图文并茂,很多点都说到了实际工作的痛处。借此机会分享出来,并结合一些个人经历,希望能给同行们提供一份实用的自查与避坑参考。

从一次整改经历说起

搞过硬件项目的朋友都知道,新项目第一次送实验室做EMC认证,十有八九会被“打回来”。为了心里有底,我们通常会在正式送测前自己先做摸底测试。这让我想起一个挺折腾的案例:当时一个项目卡在了HDMI接口的辐射超标问题上。我们几乎尝试了所有板上能想到的办法——加滤波电路、加强屏蔽、更换磁环,但效果都不理想。折腾了近两周,最后发现问题竟然出在HDMI线缆本身的屏蔽处理上。换了几种不同品牌和工艺的线材后,辐射值终于达标了。这件事给我提了个醒:EMC问题有时并不在你的核心电路板上,外围的连接线、结构件,甚至一个不起眼的接插件,都可能是问题的关键。这也反映了系统化思维在电磁兼容设计中的重要性,更多关于系统级设计与调试的思路,可以在 云栈社区 的硬件板块中找到同行们的实践经验分享。

EMC指南的核心:四大问题与系统化解法

这份指南的好,在于它把复杂的EMC挑战系统地归纳为四个主要方面,并给出了从原理到实操的清晰指引。

1. EMI:你的设备别干扰别人

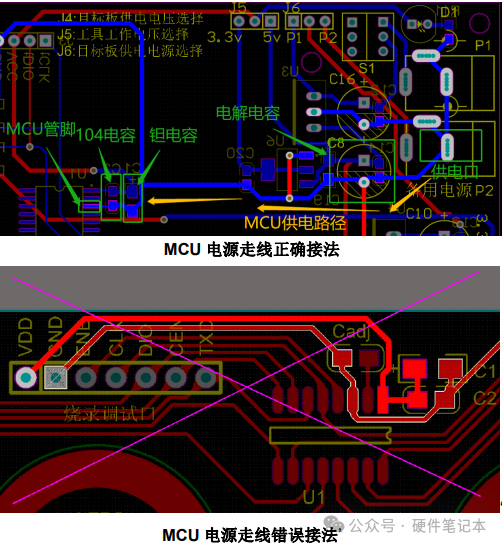

EMI(电磁干扰)关注的是设备自身产生的电磁噪声是否会干扰其他设备或环境。指南涵盖了传导骚扰、辐射骚扰、骚扰功率等常见测试项。其核心的硬件设计建议非常直观,例如在电源滤波布局上:

上图清晰展示了两种接法:正确接法要求电源线必须先经过电解电容和104瓷片电容滤波,再进入MCU的VDD和VSS引脚;而错误接法中,电容被“晾”在了走线一旁,几乎无法起到滤波作用,噪声直接灌入了芯片。指南还建议可将电解电容替换为容值不小于10uF的钽电容以提升性能。这种图文对照的方式,新手能快速理解并模仿,老手也能即刻用以自查。

如果测试超标,指南提供了清晰的排查思路:检查是否是MCU的系统时钟或其倍频、触摸扫描频率的谐波导致了干扰。解决办法包括降低时钟频率、调整触摸扫描频率等。

2. CS:抵抗外界的射频干扰

CS(传导骚扰抗扰度)测试考察的是设备抵抗从电源线或信号线耦合进来的外界射频干扰的能力。指南列出了相应的测试等级与标准,并给出了通用的硬件改善方法,例如为电缆增加滤波器或磁环、优化电源滤波电路、注意PCB的敷铜方式以减少环路天线效应等。

对于触摸按键这类易受干扰的应用,指南给出了专项建议:可以在触摸通道上串联一个电阻(阻值可在510Ω至5.6KΩ间调整),同时在软件层面增大触发阈值和确认次数,双管齐下来提升按键的抗干扰能力。这涉及到对信号完整性与系统稳定性的深入理解,相关的基础理论可以在 计算机基础 知识库中进行系统性的学习。

3. EFT:应对电网中的“尖峰脉冲”

EFT(电快速瞬变脉冲群抗扰度)模拟的是现实中电网因继电器、开关等动作产生的一连串快速尖峰脉冲干扰。这部分再次强调了电源滤波电路布局的至关重要性:必须避免电源和地线形成大的包围环路,尤其是将MCU包裹在内的环路,这会成为一个高效的干扰接收天线。

软件上也需要配合加固:将未使用的IO口设置为固定的输出状态;在通信协议中加入校验和重发等容错机制;充分利用看门狗定时器,确保系统受干扰后能自动复位恢复。

4. ESD:构建静电防护体系

ESD(静电放电抗扰度)是产品可靠性的基本防线。指南从芯片级的测试模型讲起,重点落在PCB设计和结构设计的防护上。

- PCB设计:通过合理的敷铜、电路分区、增加TVS等ESD防护器件,为静电提供低阻抗的泄放路径。

- 结构设计:采用绝缘处理、确保金属部件良好接地、保持足够的电气安全间隙,从物理上阻止静电引入内部电路。

- 软件加固:初始化配置好IO口状态,通信中加入校验,对ADC采样进行软件滤波等,提升系统鲁棒性。这些防护措施本质上是建立一套多层次的安全体系,其思想与构建可靠的 网络/系统 有相通之处,都是通过冗余和隔离来保障核心功能。

一份实用的设计自查清单

结合指南内容和实践经验,你可以从以下几个层面快速审视自己的设计:

- 电源路径:检查电源进入板卡后,是否先经过滤波电容再到达各芯片?电容是否紧靠芯片电源引脚?

- 信号完整性:对敏感信号(如时钟、复位)和高速信号,是否考虑了匹配、屏蔽或滤波?

- 接地策略:地平面是否完整?数字地、模拟地、功率地的分割与单点连接是否正确?

- 结构接口:线缆出入口、金属面板、接缝处是否有相应的滤波或接地处理?

- 软件容错:代码中是否对关键操作、通信数据进行了超时、重试、校验等保护?

关于资料与学习

本文提及的《赛元EMC性能优化指南》原文档,据资料显示可通过关注相关技术公众号并发送特定关键词获取。请注意,该文档版权归原作者所有,仅可用于个人学习与技术交流,请勿用于任何商业用途。

电磁兼容设计是一门需要理论与实践紧密结合的学问。这份图文指南的价值在于它提供了清晰的、可操作的设计正误对比和问题排查脉络,非常适合作为手边的一份速查参考。希望这份梳理和其中的案例,能帮助你在下一次面对EMC挑战时,多一份从容,少走一些弯路。记住,好的EMC设计,是从画第一根线、摆第一颗器件时就开始的。 |