在2025年的国际固态电路峰会(ISSCC)上,博通(Broadcom)展示了一款引人瞩目的6.4Tb/s共封装光学专用芯片。这款芯片采用业界领先的7纳米FinFET工艺制造,单颗芯片内部集成了64个入口路径直接驱动跨阻放大器(Ingress Path Direct-Drive TIA)和64个出口路径重定时分段式马赫-曾德尔调制器驱动器,旨在为下一代数据中心与AI集群提供超高带宽、高能效的光互连解决方案。

据博通介绍,这款7纳米ASIC通过与光子集成电路(PIC)进行3D异构封装,实现了高达4.2 pJ/b的卓越能效。在106.25Gb/s的PAM-4传输速率下,其接收端的TIA灵敏度优于-11dBm,误码率下限优于1E-9。发射端的光信号质量同样出色,测得的瞬态色散眼图闭合代价仅为1.48dB,消光比达到4.57dB。

随着横向扩展的AI训练集群对带宽需求的爆炸式增长,传统可插拔光模块在密度、功耗和成本上面临挑战。共封装光学技术作为一种关键的异构集成方案,通过将光子芯片与网络交换ASIC紧密集成,缩短了电互连距离,从而显著降低了系统功耗、复杂性和信号完整性风险,成为应对未来带宽挑战的重要方向。

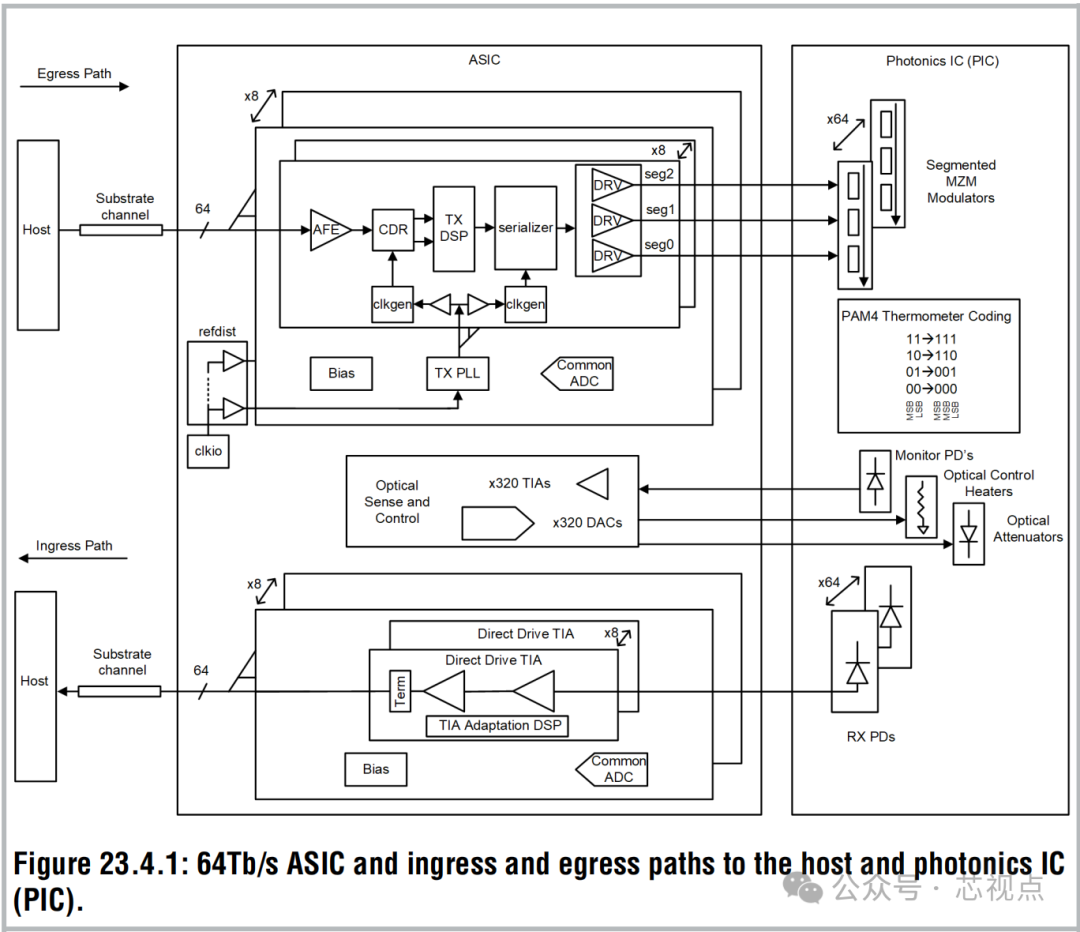

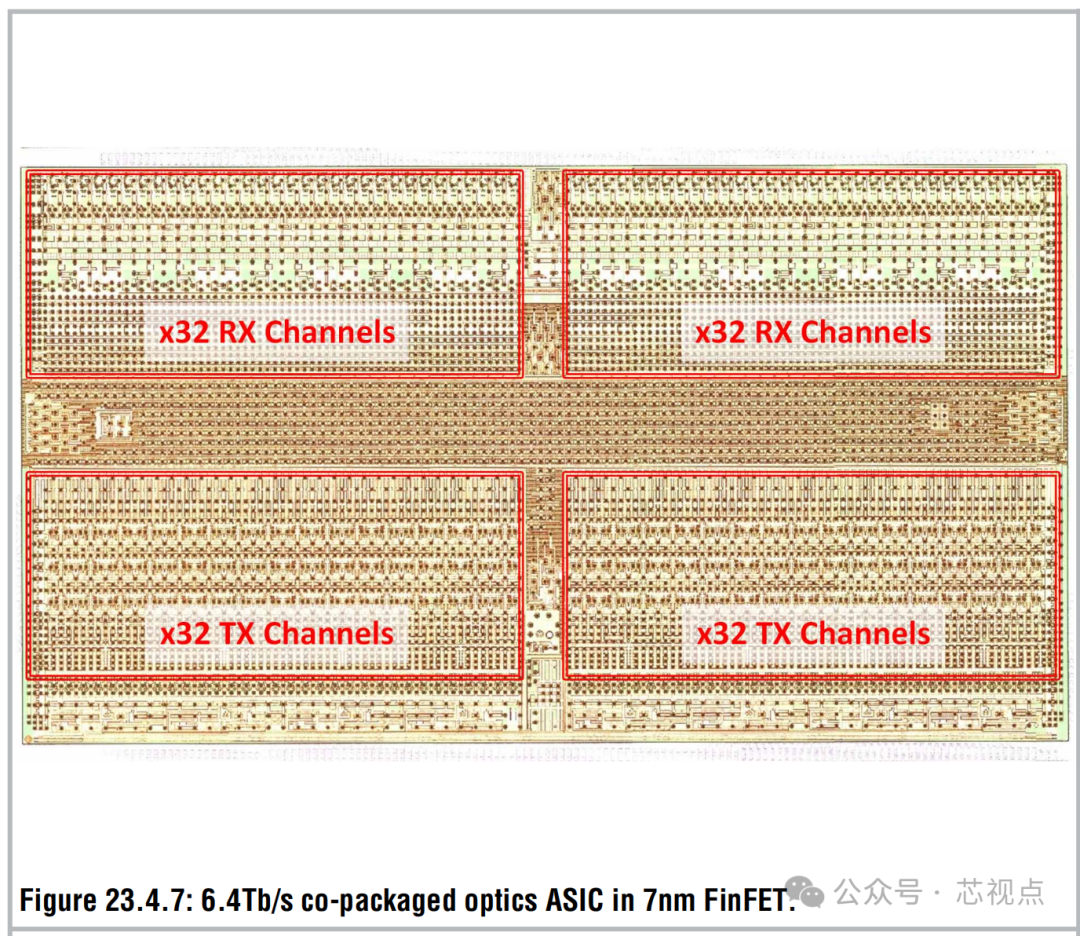

本文介绍的正是博通为CPO应用打造的一款6.4Tb/s重定时器ASIC。下图展示了其整体架构,实现了64个106.25Gb/s PAM-4通道的单片集成。

这些通道直接与PIC的线路侧相连:发送端驱动64个分段式马赫-曾德尔调制器,接收端则连接64个光电二极管。在发送路径上,模拟前端之后连接时钟数据恢复单元,对来自主机接口的数据进行重定时与解串行化处理。CDR由发送锁相环产生的时钟驱动,解串后的数据总线通过发送端数字信号处理器馈送至MZM驱动器。这里采用PAM-4信号的温度计编码,允许使用最高有效位数据同时驱动两个调制器段。

接收路径则采用了基于DSP自适应算法的跨阻放大器。TIA的输出通过有机基板直接驱动主机侧的交换ASIC。此外,该ASIC内部还集成了320个监控光电二极管读出通道和320个用于热调谐的加热器数模转换器,以实现对PIC的光学性能监测与控制。

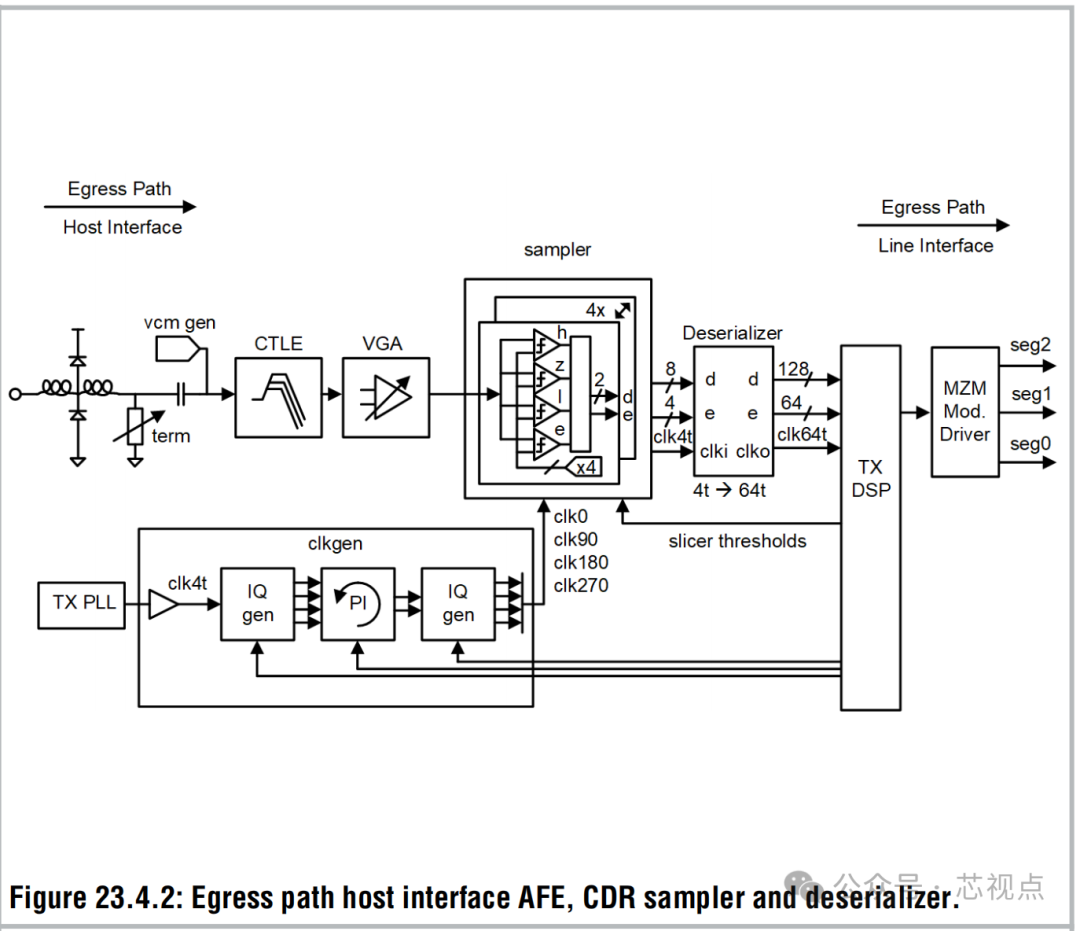

出口路径(发送)的主机侧接口设计如下图所示。输入信号经过校准终端,以电容耦合方式接入连续时间线性均衡器。CTLE利用带宽扩展T型线圈进行输入端的静电防护滤波,其输入共模电压由可编程DAC设定。CTLE驱动可变增益放大器,VGA再驱动一个4倍时间交织的采样器。CTLE和VGA均采用了电阻校准和T型线圈来扩展带宽。

CDR所需的四个采样相位,由发送锁相环时钟通过专门的时钟生成模块产生。该模块中,一个基于数字延迟锁相环的正交时钟发生器驱动一个相位插值器,随后第二个正交时钟发生器产生0°、90°、180°和270°的精确采样时钟。四组采样器将数据和误差信息送入解串器,解串器最终以更高的时钟速率向发送DSP输出128位数据和64位误差信息。发送DSP内含时钟恢复环路,实现CDR适配功能,并将处理后的PAM-4最高有效位和最低有效位数据送往线路侧。DSP中的采样器阈值适配算法,使用16个9位DAC来精细调整每个采样器组的4个判决门限。

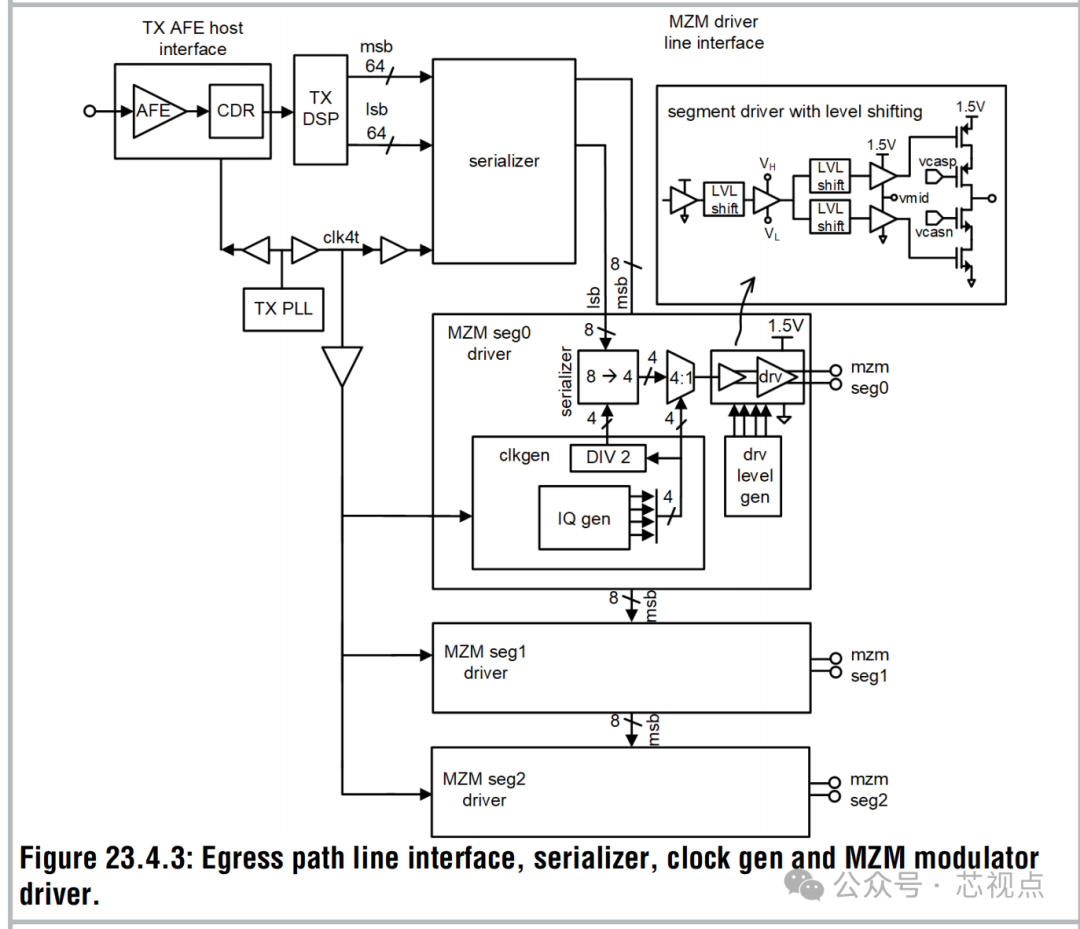

出口路径的线路侧接口设计如图所示。串行器首先将来自发送DSP的64位重定时并行数据转换为8位数据流。这些处于8倍时钟域的数据总线随后被分配到3个驱动段,其中第一个段驱动最低有效位,后两个段驱动最高有效位。

发送锁相环的时钟被分布到三个MZM驱动段。每个段内的本地时钟发生器通过正交时钟生成模块校正时钟失真,并生成四个相位。来自IQ发生器的校准时钟驱动段驱动器最后两级串行器。一个4:1复用器的输出,通过一个两级电平转换预驱动器转换为1.5V的NRZ信号,该预驱动器驱动堆叠输出级的PMOS和NMOS栅极。预驱动电压和共源共栅电压则由段内的电平生成低压差线性稳压器和DAC产生。

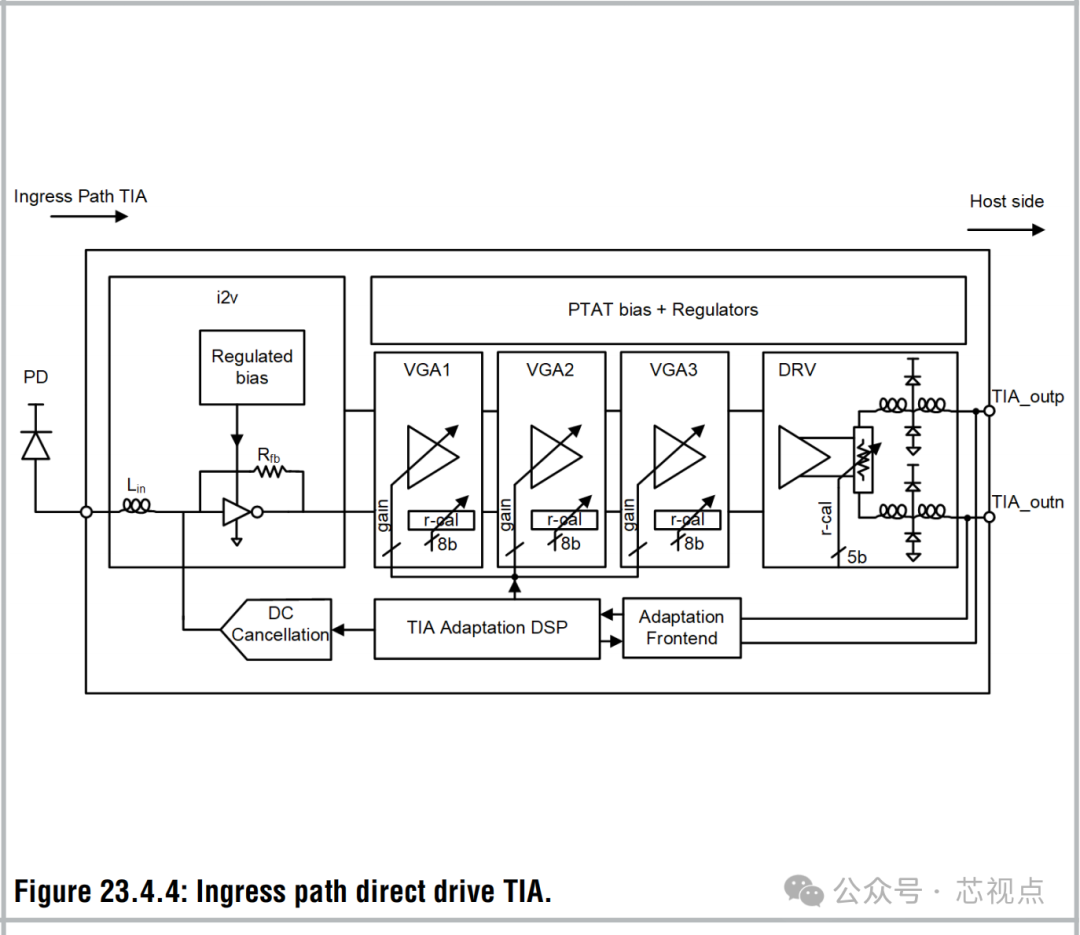

入口路径(接收)的核心是一个直接驱动的跨阻放大器,其架构如下图所示。在线路侧,光电二极管的阳极连接到一个电流-电压转换器。输入电感用于谐振补偿输入寄生电容,从而扩展带宽。

I2V核心是一个带有反馈电阻和稳压偏置电流的反相器结构。I2V级以伪差分方式驱动第一个可变增益放大器,之后的信号路径通过VGA2、VGA3和输出驱动器保持全差分。各级VGA和驱动器均采用T型线圈扩展带宽,并使用8位可调校准负载电阻进行阻抗匹配。增益调节通过数字增益控制代码实现。输出驱动器则采用5位终端校准,并驱动ESD保护电路和输出焊盘。TIA的差分输出通过有机基板直接驱动主机交换ASIC。

每个通道的TIA都通过一个本地DSP进行数字自适应。该DSP通过控制VGA增益控制字来调节信号幅度,并通过一个连接至TIA输入端的直流消除DAC来抵消直流偏移。自适应所需的信息由一个专门的前端模块提供给DSP。每个VGA提供约6dB的增益,增益步进为0.2dB。TIA的标称输入参考电流噪声密度为15pA/√Hz,功耗低于50mW。此外,每个TIA通道还集成了本地的与绝对温度成正比偏置电路和电源稳压器。

这款CPO ASIC采用7纳米FinFET工艺制造,芯片显微照片如下所示。单片芯片上集成了64个收发通道、发送锁相环、辅助公共电路以及模数/数模转换器等组件。

完整的6.4Tb/s光引擎由这款7纳米ASIC与PIC通过3D封装技术构建而成。多个这样的光引擎可以与主机网络ASIC共封装,从而实现吞吐量的灵活扩展。

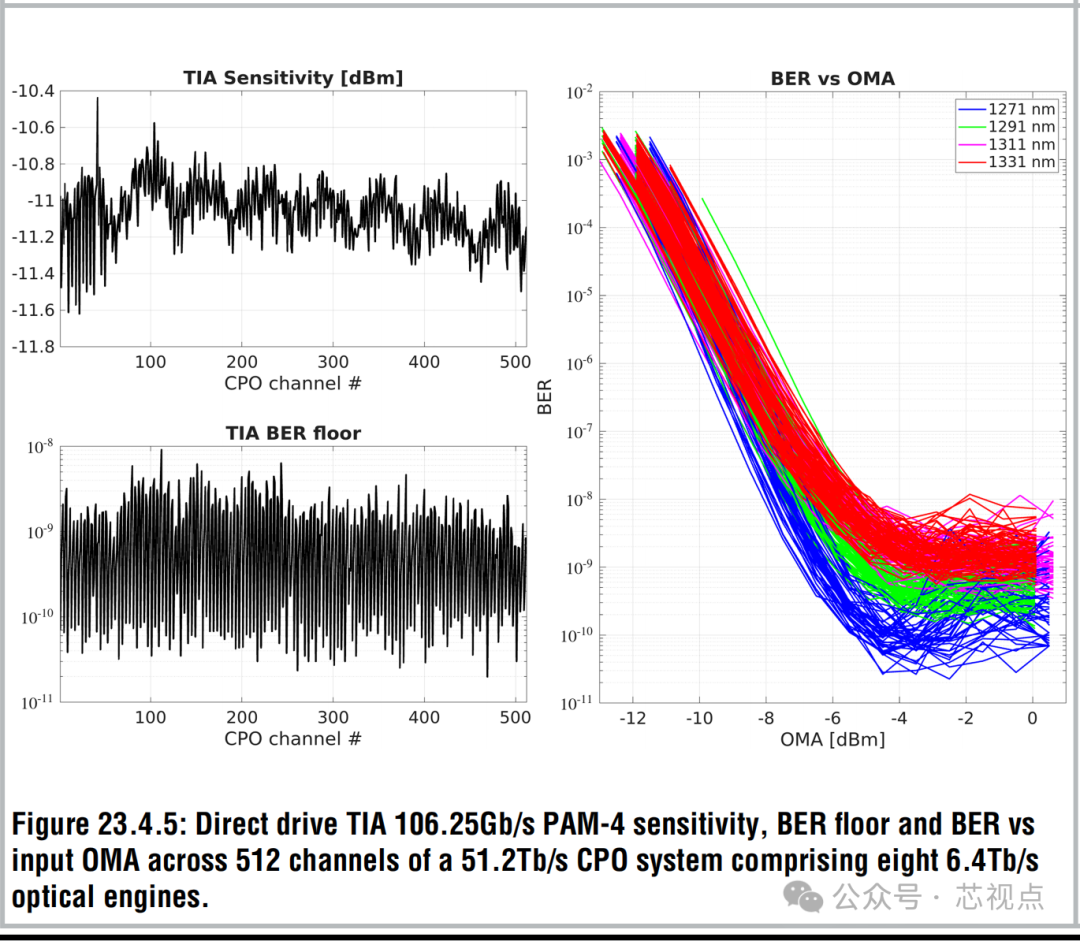

接收路径的性能通过一个由8个6.4Tb/s光引擎构成的51.2Tb/s CPO系统进行了验证,测试结果如下图所示。

图中展示了直接驱动TIA在四个不同波长下的性能,其输出已由主机网络ASIC进行均衡。测试覆盖了512个通道,TIA的平均灵敏度优于-11dBm,平均误码率下限优于1E-9。在106.25Gb/s的PAM-4速率下,发射端的预前向纠错误码率优于1E-9,超过99.98%的通道实现了无误码传输。

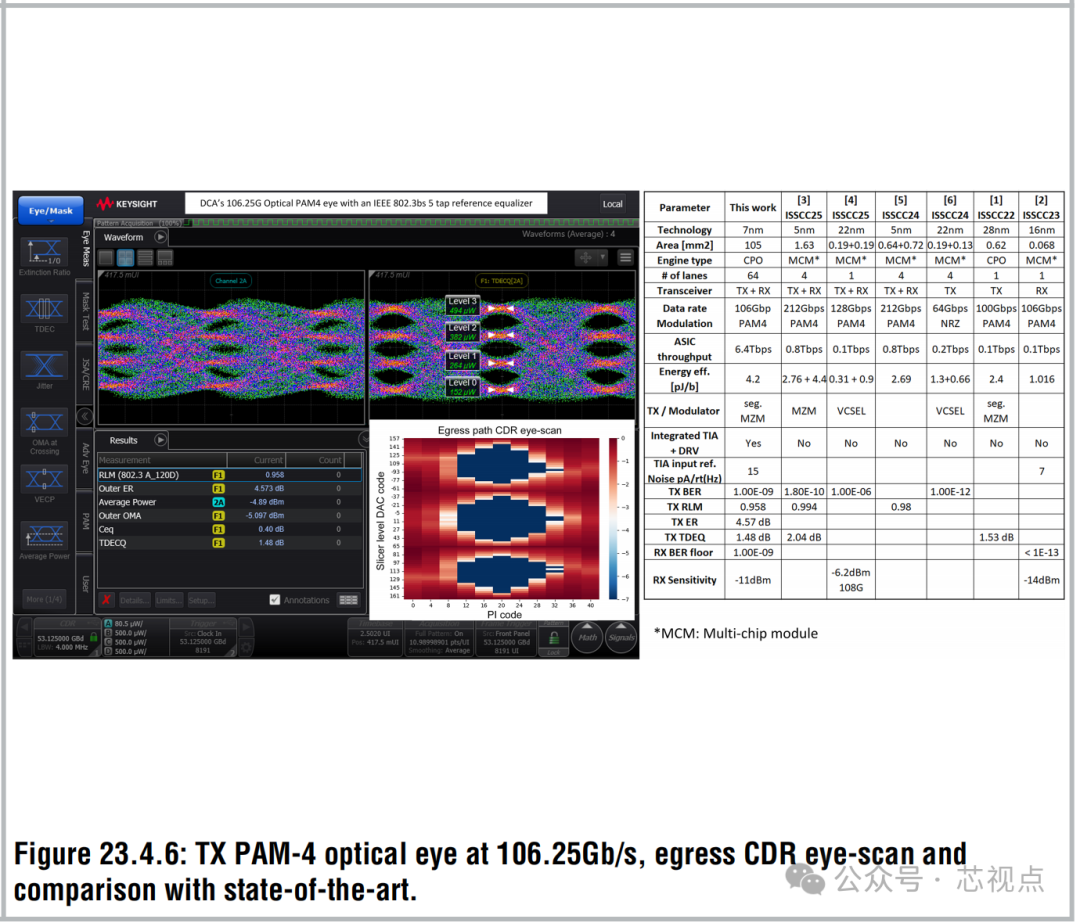

发射端的信号质量通过眼图扫描和直接测量进行评估。由发送DSP捕获的CDR眼图扫描结果显示出一个开放的PAM-4眼图。使用示波器测量PRBS-13码型得到的光学PAM-4眼图如下,测量中应用了符合IEEE 802.3bs标准的5抽头前馈均衡器作为参考接收均衡器。

最终测得发射端的瞬态色散眼图闭合代价为1.48dB,外消光比为4.57dB,比率电平失配为0.958。与当前最新的光互连收发器技术相比,博通的这款6.4Tb/s CPO ASIC在集成度与吞吐量上达到了领先水平,单芯片支持64条106.25Gb/s PAM-4通道,并以4.2pJ/b的能效,为下一代数据中心与高性能计算网络提供了强大的互连核心。

对于此类高带宽、低功耗互连技术的深入剖析与更多前沿ASIC设计分享,欢迎关注云栈社区的技术讨论。