为什么总是在电路里摆两个0.1uF和0.01uF的电容?这背后其实涉及了电磁兼容(EMC)防护中关于旁路与去耦的核心知识。

旁路和去耦

在电路设计中,旁路电容(Bypass Capacitor)和去耦电容(Decoupling Capacitor)是经常被提及的两个概念,但它们的区别与作用却常常让人混淆。

要理解这两个词,我们不妨回到它们的英文原意。

Bypass在英文中有“绕行”、“抄近路”的意思,这完美地描述了它在电路中的功能,如下图所示。

而Coupling是“耦合”的意思,指的是一个系统(A)中的信号变化对另一个系统(B)产生了影响。Decoupling自然就是“解耦”,即减弱或消除这种不希望的影响。

电路中的旁路和去耦

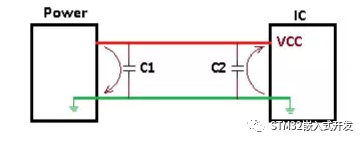

在典型的电源供电电路中,一个直流电源(Power)为芯片(IC)供电,工程师通常会在电源路径上并联两个电容,具体布局如下图所示。

旁路

如果电源(Power)输入端受到了来自外部的干扰(通常是高频噪声),这些干扰可能会直接传导到IC,导致其工作异常。此时,在靠近电源输入端放置的电容C1就发挥了“旁路”作用。

由于电容对直流电呈高阻态(开路),但对交流电(尤其是高频信号)呈低阻态。高频干扰信号因此会“抄近路”,优先通过低阻抗的电容C1流回地(GND),而不是继续前行去骚扰IC。这里的C1就是典型的旁路电容。

去耦

另一方面,集成电路(IC)本身在工作时,尤其是启动瞬间或内部状态高速切换时,会产生快速的电流需求波动。这种瞬间的大电流如果全部从远处的电源汲取,会在供电线路的寄生电感上产生压降,导致IC供电引脚(VCC)的电压出现波动,进而可能影响自身或其他器件的稳定工作。

在靠近IC的VCC引脚处放置的电容C2,这时就扮演了“去耦”或“退耦”的角色。它如同一个微型本地储能池,在IC需要瞬时大电流时快速放电进行补充,在IC电流需求变小时吸收多余能量,从而将IC产生的电流波动限制在局部,阻止其回灌到主电源路径上,实现了IC与电源之间的“解耦”。这里的C2就是去耦电容。

为什么要用两个电容?

现在回到最初的问题:为什么常见的设计是并联一个0.1uF(100nF)和一个0.01uF(10nF)的电容?一个容值更大的电容不是滤波效果更好吗?

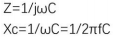

我们先看电容的阻抗公式:

从容抗(Xc)公式 Xc=1/ωC=1/2πfC 来看,确实,电容值C越大,对于相同频率f的信号,其容抗越小,即滤波(旁路)效果越好。那为什么还要多此一举加一个小电容呢?

关键在于电容并非理想器件。实际的贴片电容具有等效串联电感(ESL),其总阻抗会随频率变化。在低频段,它主要呈现容性;当频率达到其自谐振频率点时,阻抗最小;超过自谐振频率后,由于ESL起主导作用,阻抗反而会随频率升高而增加,呈现感性。

不同封装、不同容值的电容,其自谐振频率点不同。通常,容值越小的电容,其自谐振频率越高。将一个大电容(如0.1uF)和一个小电容(如0.01uF)并联使用,相当于拓宽了有效的低阻抗频率范围。大电容负责滤除较低频率的噪声,而小电容则利用其更高的自谐振频率,为高频噪声提供低阻抗通路。两者互补,能在更宽的频谱范围内提供有效的噪声抑制,这也是应对复杂电磁环境、提升系统EMC性能的一种实用设计。

希望这篇关于滤波电容的解析能对你有所帮助。更多关于计算机底层原理与硬件设计的内容,欢迎在云栈社区交流讨论。 |