文章目录

- 一、显示控制器的基本概念

- 二、VOP 简介

- 三、connector-mirror 技术

- 四、VOP-Split 技术

- 五、名词解释

一、显示控制器的基本概念

显示控制器,通常也称为 LCDC(LCD Controller),它的核心任务是将内存里的图像数据搬移到显示设备上。随着技术的迭代,它的功能也变得更加丰富,现在已经可以处理一些基础的图像操作,比如缩放、旋转以及多个图层的合成。

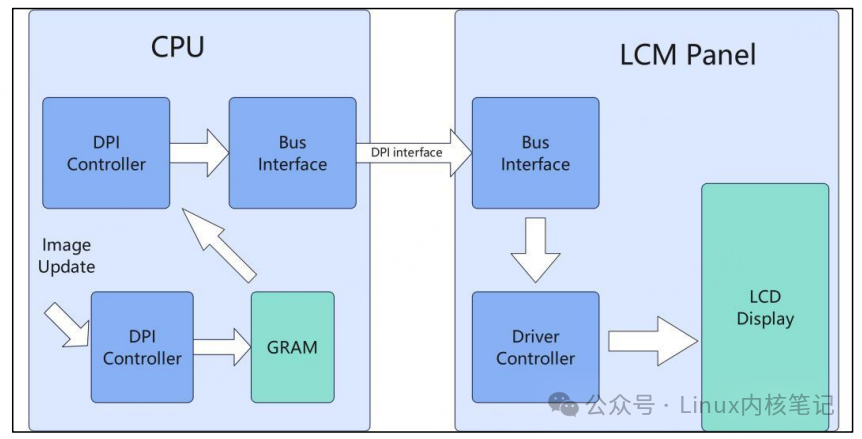

在处理器内部,显示控制器扮演的角色类似于电脑中的独立显卡。当一颗 SoC 集成了显示控制器,就意味着它内置了图形输出能力,可以直接驱动显示屏。像瑞芯微的 RK3399、RK3588 和 RK3568 这类高性能芯片,都内置了强大的显示控制器,无需额外硬件就能实现视频输出。其集成了显示控制器的处理器框架可以参考下图:

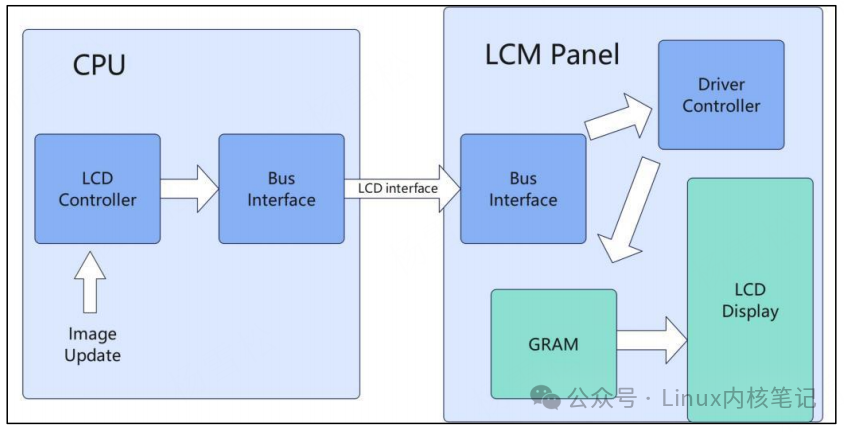

而在一些对功耗和成本更敏感的嵌入式场景,比如使用 STM32 这类微控制器时,芯片内部通常不集成显示控制器。这类处理器如果需要显示图像,就必须外接一个自带显存(GRAM)的显示模块来完成图形处理和最终显示。没有集成显示控制器的处理器架构可以参考下图:

这种没有集成显示控制器的架构有几个明显特点:

- 图形处理能力有限:需要依赖外置显示模块自带的处理资源。

- 功耗和成本较低:适合对能效和价格敏感的应用。

- 应用场景特定:多见于工业控制、传感器面板等基础显示需求的领域。

这两种架构的差异,本质上反映了处理器在不同性能定位和集成度上的取舍。高性能处理器通过集成显示控制器来获得强大的视频输出能力,而专用微控制器则采用更模块化的设计,在保证系统灵活性的同时满足特定需求。

二、VOP 简介

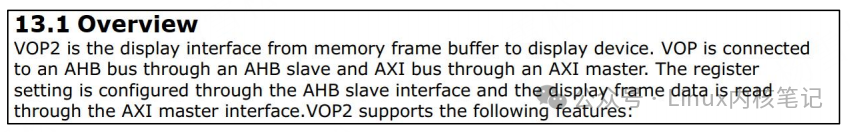

在瑞芯微(Rockchip)的 SoC 系列中,显示控制器有一个专门的名称:VOP(Video Output Processor)。我们以 RK3568 处理器为例,其技术参考手册(TRM)中对 VOP2 的描述如下:

手册里提到,VOP2 是连接内存帧缓冲区与显示设备的显示接口。它通过 AHB 从接口(AHB Slave)连接到 AHB 总线,用于配置寄存器;同时通过 AXI 主接口(AXI Master)连接到 AXI 总线,用于读取要显示的帧数据。

2.1、VOP1

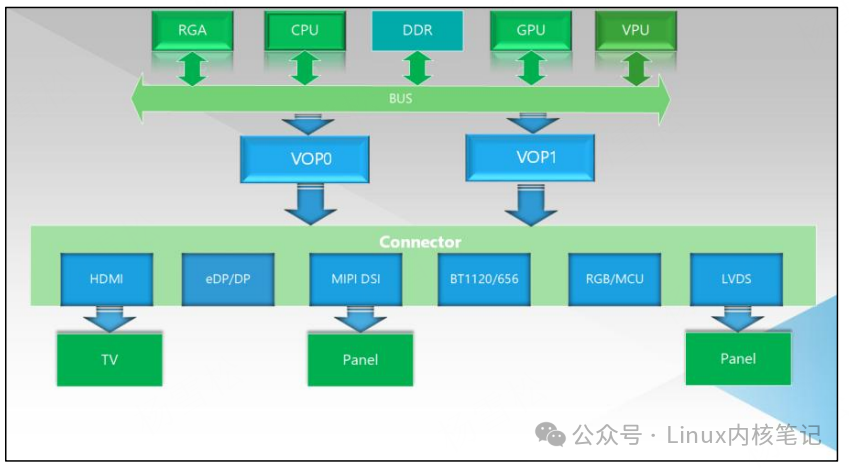

目前,瑞芯微的处理器中存在两种 VOP 架构:VOP1 和 VOP2。它们最主要的区别在于支持多屏显示的方式。

传统上,一个 VOP 在同一时间只能驱动一块屏幕。想要实现多屏显示,就需要在芯片里集成多个独立的 VOP 模块。VOP1 采用的就是这种传统方式,其架构功能示意如下:

例如 RK3399 处理器,它内置的显示控制器就是 VOP1 类型。在其 TRM 手册中关于 VOP 的描述明确指出了这一点:

可以看到,RK3399 芯片内部集成了两个 VOP 模块,分别叫 VOP_BIG 和 VOP_LIT。因此,RK3399 最多可以支持两块屏幕同时独立显示。

2.2、VOP2

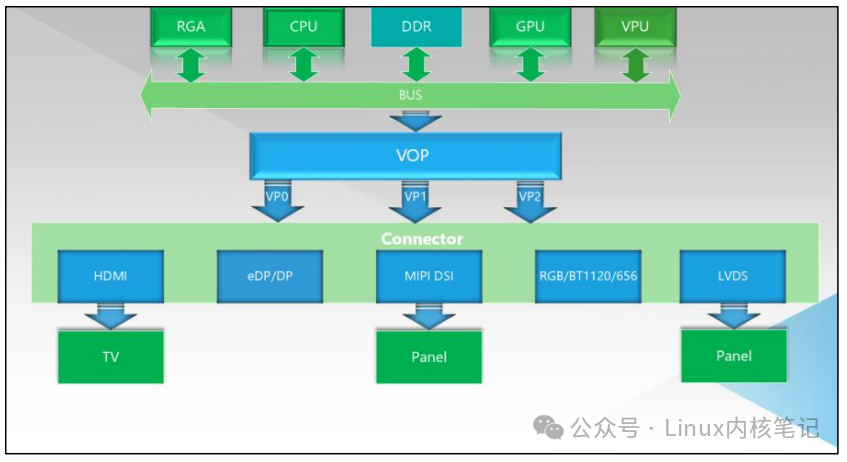

而 VOP2 架构则采用了不同的思路。在处理器内部通常只设计一个 VOP 模块,但在这个 VOP 的后端,集成了多个独立的 VP(Video Port) 输出接口。这些 VP 接口可以同时、独立地工作,从而实现多路显示输出。

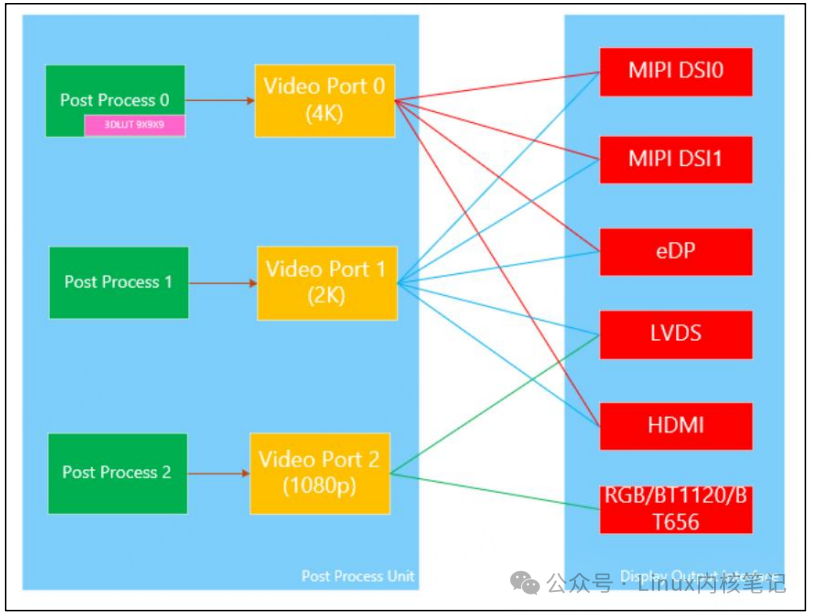

简单来说,VOP2 的显示能力取决于它有多少个 VP,有几个 VP 就能支持几路同时显示(可以是相同内容或不同内容)。VOP2 的架构功能示意如下:

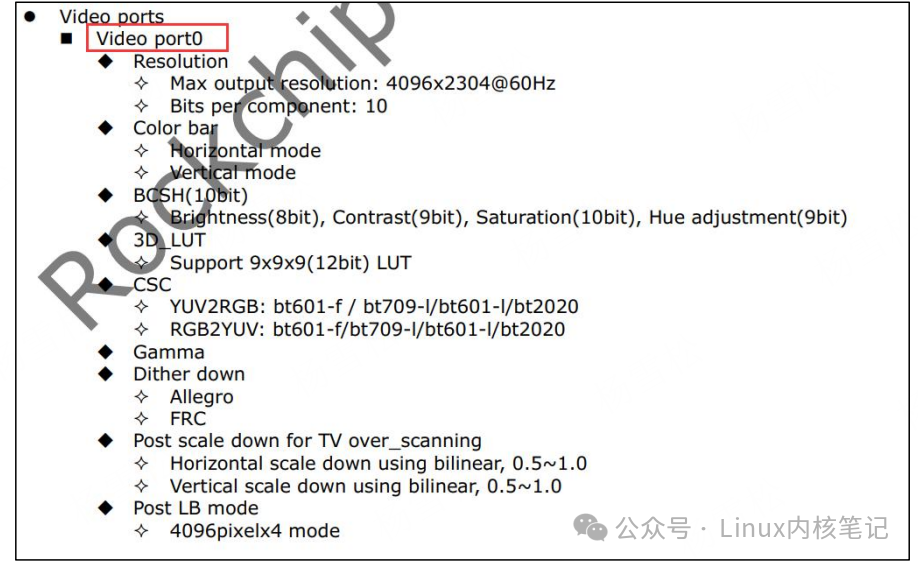

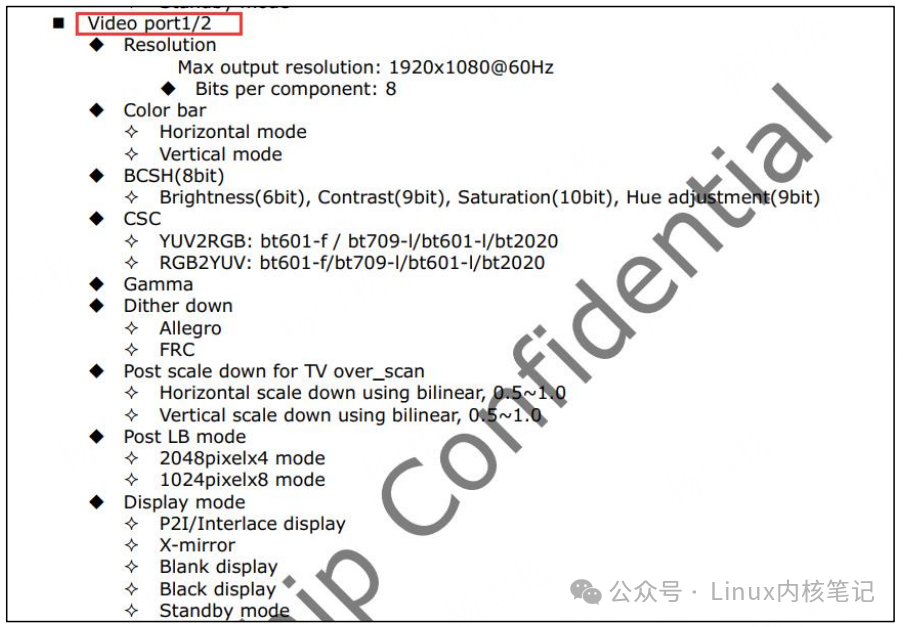

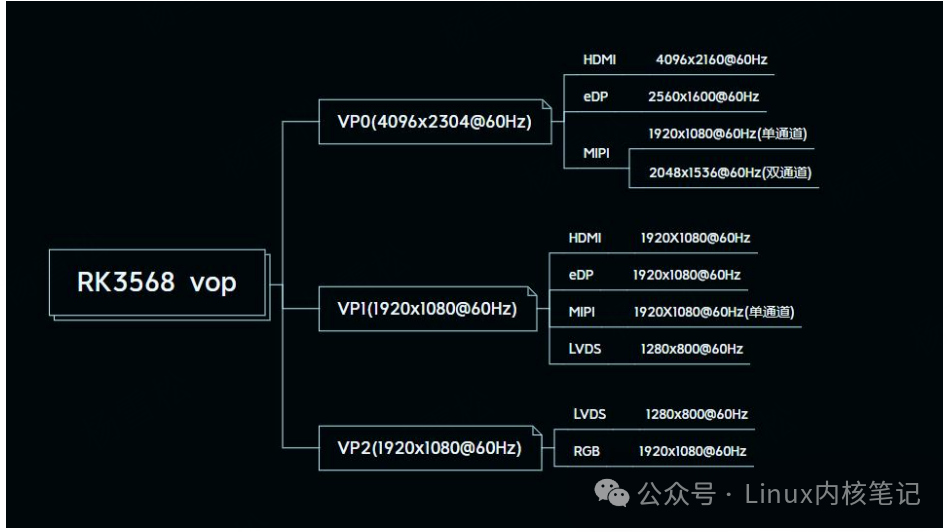

RK3568 处理器内置的显示控制器就是 VOP2 类型。查阅 RK3568 的 TRM 手册可以知道,它的 VOP2 拥有 3 路 VP(视频端口)。

所以对于 RK3568 而言,它最多支持 3 屏同显或异显。更灵活的是,RK3568 的每一路 VP 还可以支持不同类型的 LCD 屏幕接口,其连接关系如下图所示:

具体来说,RK3568 的 VP0 和 VP1 都支持连接到 MIPI0、MIPI1、eDP 以及 HDMI 接口,而 VP2 则支持连接到 LVDS 和 RGB接口。这种设计极大地增加了适配不同显示设备的灵活性。

需要注意的是,每一路 VP 在同一个时间点只能用于一种显示接口的输出。比如,如果 VP1 被配置为 LVDS 输出,那么它就不能同时用于 HDMI 输出。另外,不同 VP 接口所支持的最大分辨率也不尽相同。关于各 VP 接口支持的最大分辨率,可以参照下面这张总结图:

三、connector-mirror 技术

RK3568 芯片拥有三路独立的 VP,因此在基础配置下,它支持三路显示输出。但如果需要同时输出更多路画面,就可以借助 connector-mirror 技术进行扩展。

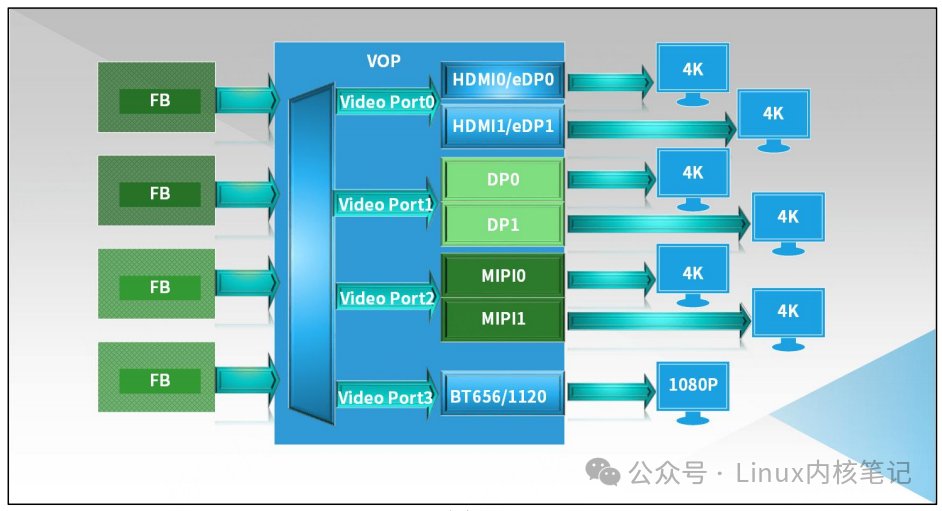

以 RK3588 为例,它在拥有四路 VOP(VP)的基础上,结合 connector-mirror 技术,可以实现同时输出七路显示信号的场景,其示意图如下:

上图展示了如何利用 connector-mirror 技术:将两路 HDMI/eDP 接口“镜像”连接到 VP0 上,将两路 DP 接口连接到 VP1 上,将两路 MIPI DSI 接口连接到 VP2 上,VP3 则通过 BT656/BT1120 输出。这样就实现了总计 7 路输出。

需要注意的是,这 7 路输出信号实际上是由 4 组独立的显示通路(即4个VP)产生的。在同一个 Video Port 上通过 mirror 连接的两个显示接口,它们输出的显示时序和内容是完全相同的,相当于“克隆”输出。

在这种模式下,每组显示通路(即每个VP)所能支持的最大分辨率,受限于该 VP 本身以及所连接显示接口的能力上限。此功能可以通过设备树源文件(DTS)进行配置,只需将两个显示接口节点挂载到同一个 Video Port 节点下即可。目前,该特性主要在瑞芯微的 NVR SDK 中获得支持,Android 系统暂不支持,因此这里不做更深入的代码级展开。

四、VOP-Split 技术

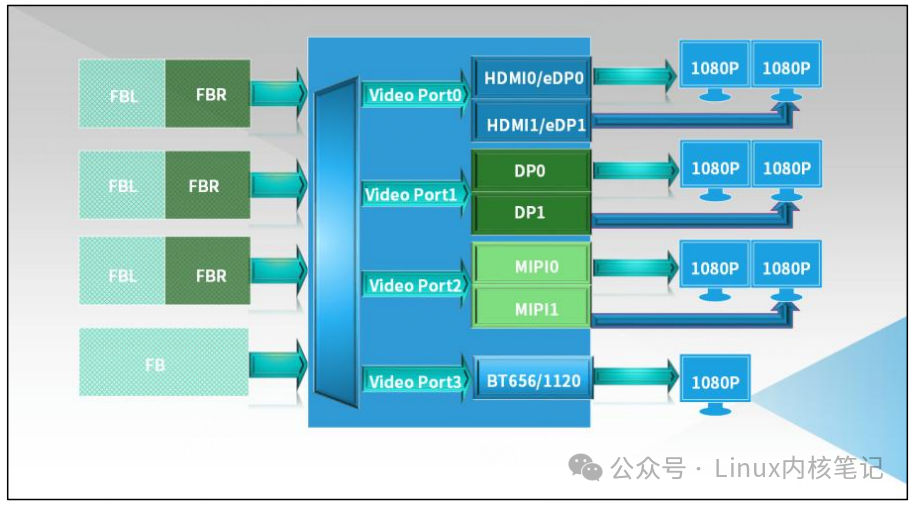

VOP-Split 功能是一种类似于 MIPI 双通道模式的技术。它能够将一路 Video Port 的输出,在水平方向上分割成左右两个部分,从而同时驱动两个显示接口。与 connector-mirror 不同,在 Split 模式下,两个接口的显示时序保持一致,但可以分别显示不同的内容(即左半部分和右半部分)。

需要注意的是,该功能目前仅支持基于 VOP2 架构的硬件平台。利用 VOP-Split 功能,可以实现更高效的显示扩展,其应用框图如下:

如图所示,当在 VP0 上启用 Split 模式后,VP0 的输出可以同时驱动两个显示接口(例如 HDMI0 和 HDMI1)。这两个接口显示的内容,是将 VP0 输出的完整画面在水平方向上平分的结果。例如,如果 VP0 输出分辨率是 3840x1080,那么每个显示接口将各得到 1920x1080 的画面。

在 Split 模式下,参与输出的两个显示接口必须保持完全相同的显示时序和帧率。目前,该功能仅在 RK3588 平台上得到支持。

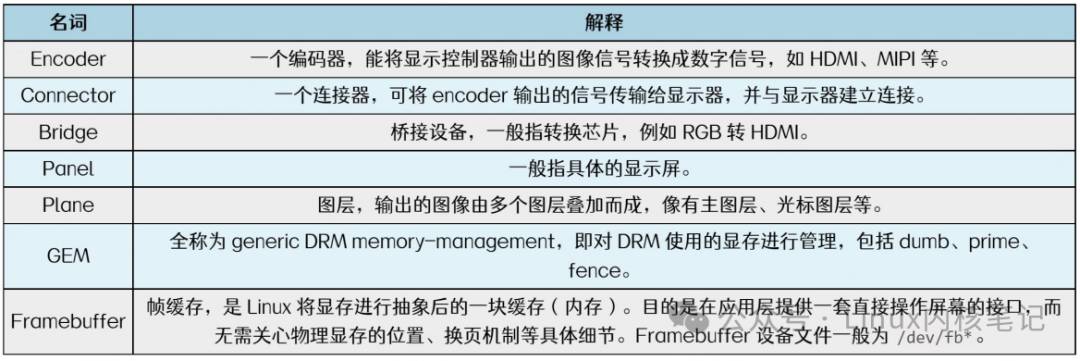

五、名词解释

在开发或阅读其他显示控制器相关资料时,你可能会遇到一些专业术语。下面这个表格整理了其中常见的几个,并给出了简要解释:

理解这些基本概念,有助于更深入地学习和调试 Linux 下的 DRM(Direct Rendering Manager)显示框架。希望这篇关于瑞芯微 VOP 显示控制器的解析,能帮助你在 LVDS 或其他显示接口的开发中理清思路。如果你想就此类嵌入式显示技术进行更多交流,欢迎在 云栈社区 分享你的经验或提出问题。