论文导读:借鉴机器学习算法让“硬件后门”无处遁形

随着硬件设计与制造供应链日益复杂,一个严重但隐蔽的问题是:所谓的硬件后门——即在芯片设计、编译、布局布线等环节被恶意植入的不良逻辑——有可能未经检测地潜入最终产品。传统的逻辑测试、验证等方法,在面对复杂系统与商业CPU时,经常力不从心。

为解决这一问题,研究团队将目光投向了XGBoost等机器学习方法。通过对RISC‑V软核在FPGA上的位流进行全面数据提取——不仅包括硬件性能计数,还包括综合、实现过程的数据,如使用的LUT数量、电路时序、设计时钟频率、功耗估计等——构建了一个用于HT检测与分类的数据驱动流程。

实验结果相当惊人:当ML模型同时使用综合/实现特征与性能特征时,无论是检测还是对HT类型分类,都达到了100%的准确率。更重要的是,他们通过特征重要性分析和降维可视化证明——真正区分是否含有后门的关键,在于综合/实现阶段的电路时序/结构信息,而仅靠运行时性能计数是远远不够的。

原文链接:https://www.scitepress.org/Link.aspx?doi=10.5220/0012324200003648

用Raspberry Pi Pico2与PIO实现12 MHz ROM仿真

对于复古电脑爱好者来说,原装EPROM芯片不仅日益稀缺,而且编程器也越来越难找。为了解决这个问题,开发者kyo-ta04提出了Pico2ROMEmu——一种基于Raspberry Pi Pico2的ROM仿真器。

这个仿真器的厉害之处在于速度:它在经典CPU上测试时,对Z80能稳定运行10 MHz,对MC68000则可达到12 MHz——性能足以驱动复古机器。

其关键技术是用Pico2的“可编程I/O”而不是其主CPU核心来处理时序、数据读写等低层I/O逻辑。这样既释放了主核资源,也让ROM仿真足够快速。

原文链接:https://hackaday.com/2025/12/06/emulate-roms-at-12mhz-with-pico2-pio/

Linux 6.19内核更新:ARM与RISC-V新SoC支持盘点

为了持续推动主线内核对更多平台的支持,Linux 6.19在SoC及平台兼容性上迎来了显著扩展。在目前的合并窗口期,多个分支为多款新兴与传统ARM与RISC-V硬件带来了主线支持。

SoC/硬件支持概览

- Tenstorrent Blackhole:首次被加入主线,是基于RISC-V、面向AI加速的PCIe卡。虽然目前只是基本启动与控制台支持,但这标志着主流Linux将更友好地支持高性能RISC-V加速硬件。

- 黑芝麻C1200:这是国内面向汽车/嵌入式应用的新SoC,对未来车载系统、智能设备开发极为关键。

- Anlogic dr1v90:这是以芯来单核RISC-V UX900为基础的FPGA平台/SoC,对于FPGA + RISC-V开发者来说意义重大。

- 瑞萨R-Car X5H:一款新的汽车级ARM SoC,内含16核Cortex-A720。

- TI AM62L:没有GPU的工业用SoC,这对功耗敏感、无图形界面的嵌入式系统非常实用。

- 高通骁龙430:较老的SoC也终于被主线接纳,对老设备重用有意义。

对开发者与生态的意义

- 生态扩展:Linux不再仅仅支持x86或少数ARM SoC,新一代RISC-V加速器、汽车SoC、工业SoC等纷纷入列。

- 开发门槛降低:过去这类新硬件往往需要厂商维护的内核补丁才能使用,现在纳入主线后,普通开发者用标准发行版就能跟进。

- 硬件选择多样化:无论关注低功耗工业设备、汽车电子还是AI加速卡,6.19的平台支持让“开箱即用”成为可能。

原文链接:https://www.phoronix.com/news/Linux-6.19-SoCs

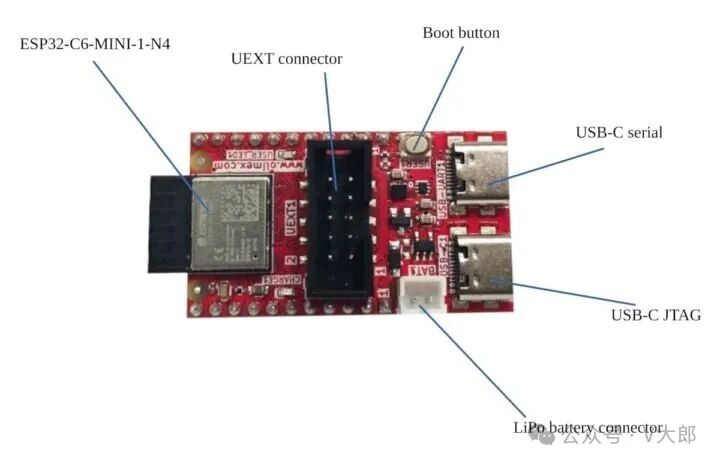

面向IoT的“全能小板”:ESP32-C6-DevKit-Lipo

用于智能设备和物联网项目的微控制器/无线模块层出不穷,但真正兼顾「无线连接能力 + 电池供电 + 扩展灵活性 + 面包板友好」的开发板仍不多。ESP32-C6-DevKit-Lipo的出现,为这一需求填补了空白。

资源配置合理:搭载单核32-bit RISC-V CPU、512 KB SRAM、4 MB SPI flash,完全足够运行常见IoT固件。

双USB-C接口:一个用作供电与串口/编程,另一个作为JTAG/调试接口。

开源硬件:KiCad原理图、PCB、Gerber等文件完全公开,便于用户二次开发或批量生产。

原文链接:https://www.cnx-software.com/2025/12/06/esp32-c6-devkit-lipo-small-open-source-hardware-esp32-c6-board-with-battery-support-uext-connector/

项目地址:https://github.com/OLIMEX/ESP32-C6-DevKit-Lipo/tree/main

国内上市公司面对RISC-V的资本动向

上海-禾赛科技:把RISC-V用在“安全级智能传感”中

- 推出Fermi C500——基于RISC-V架构的高性能激光雷达主控芯片。

- 搭配发布独家“光子隔离”物理级安全技术,并与升级的ATX-256线安全激光雷达一起亮相。

- 基于Fermi C500,禾赛从底层算力、接口、实时处理上获得完全自主权。

贵州-振华风光:扩展产品线,布局RISC-V MCU

- 正在研发RISC-V微控制器,同时推进射频/微波产品。

- 进一步进入商业航天、无人机等新兴应用市场。

- 这是典型的“替代ARM Cortex-M系列”的国产化路线,面向工控、航天、无人机等通用市场。

印度MosChip公司布局基于RISC-V的边缘AI SoC

MosChip与EMASS合作,支持后者开发的ECS‑DoT边缘AI SoC。MosChip负责其硅实现、物理设计、22 nm工艺流片、封装、测试及评估平台搭建等工作。

ECS-DoT是基于RISC-V架构、集成双神经网络加速器与4 MB片上内存的低功耗SoC,定位为“常开AI”,适配穿戴设备、无人机、IoT传感器等边缘应用。据报道,该设计目标是实现相比传统方案“高约93%性能、低约90%功耗”。

原文链接:https://www.bisinfotech.com/moschip-teams-with-emass-for-edge-ai-soc-development/