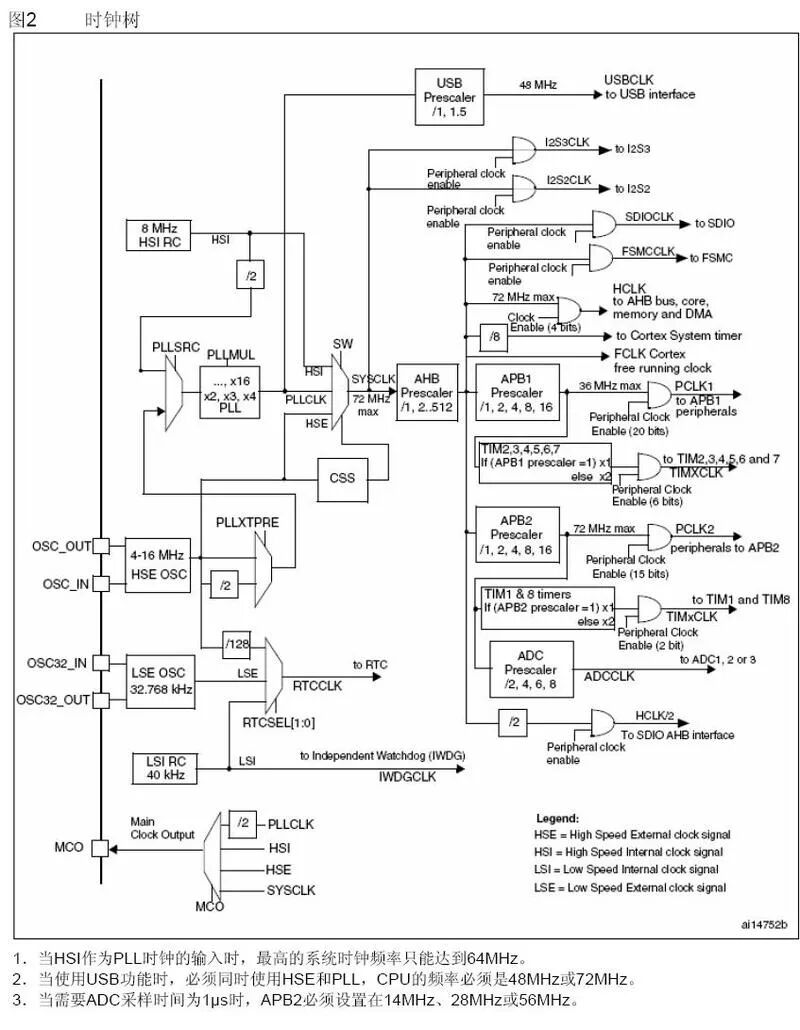

时钟信号就像是单片机的脉搏,深入了解STM32的时钟系统是进行底层开发与优化的基础。下图是STM32F1xx系列用户手册中经典的时钟系统结构图,清晰地展示了各个时钟源与分配路径。

在STM32F1xx中,主要有五个时钟源:

- HSI:高速内部时钟,采用RC振荡器,频率为8MHz。

- HSE:高速外部时钟,可连接石英/陶瓷谐振器或外部时钟源,频率范围为4MHz~16MHz。

- LSI:低速内部时钟,RC振荡器,频率为40kHz。

- LSE:低速外部时钟,通常连接频率为32.768kHz的石英晶振。

- PLL:锁相环倍频输出,其输出频率最大不得超过72MHz。

SYSCLK(系统时钟)

系统时钟SYSCLK的最大频率为72MHz,它是STM32内部绝大多数部件工作的核心时钟源。SYSCLK可以由PLL、HSI或者HSE提供,并通过AHB分频器进行分频,然后送给各个模块使用。你可以把它看作是整个芯片时钟网络的“总开关”。

HCLK(AHB总线时钟)

HCLK为高性能总线AHB提供时钟信号。它直接由系统时钟SYSCLK分频得到,在默认不分频的情况下,HCLK就等于SYSCLK。AHB总线连接了许多高速外设和存储器,因此HCLK就是这些外设和核心模块(如内存、DMA)的工作时钟。

FCLK(自由运行时钟)

FCLK是为CPU内核提供服务的自由运行时钟。我们常说的CPU主频是多少MHz,指的就是FCLK的频率,一个CPU时钟周期就是1/FCLK。这里的“自由”体现在它并不完全依赖于系统时钟HCLK;即使系统时钟暂停,FCLK也可能继续运行(例如在深度睡眠模式下)。

FCLK主要用于采样中断或为调试模块计时。当处理器进入休眠状态时,正是通过FCLK来捕捉中断信号和跟踪休眠事件的。在Cortex-M3内核中,FCLK与HCLK相互同步,以确保内核的指令执行延迟保持一致,这对于理解实时性至关重要,这也是计算机基础中处理器架构知识的体现。

PCLK(APB总线时钟)

PCLK为高性能外设总线APB提供时钟信号。APB总线分为APB1和APB2,分别连接不同的外设模块。PCLK1(给APB1)和PCLK2(给APB2)都由HCLK分频而来。值得注意的是,连接到APB总线上的某些定时器(如TIM2、TIM1等),在其对应的APB预分频器不为1时,其内部时钟TIMxCLK会是PCLK的2倍,这一点在配置定时器精度时需要特别注意。

核心关系与总结

简单梳理一下:SYSCLK是源头,经过分频产生HCLK(用于总线与外设);FCLK则相对独立地驱动CPU内核;而HCLK再次分频产生PCLK(用于更具体的外设总线)。理解这几者的关系,有助于你在配置功耗模式、精确控制外设时序以及进行操作系统级别的任务调度时做出正确决策。

虽然现在使用STM32CubeIDE等工具可以很方便地图形化配置时钟,但掌握其背后的原理,能让你在调试复杂问题或进行资源极限优化时更有底气。希望这篇解析能帮你厘清STM32时钟系统的关键概念。更多嵌入式开发深度讨论,欢迎在云栈社区交流分享。 |