在嵌入式开发领域,系统的实时性是一个核心考量指标。它衡量的是系统对外部事件做出响应的速度——从事件发生到系统开始处理,这个时间间隔越短,系统的实时性就越高。这种响应能力的基石,往往源自于微控制器(MCU)内核本身的中断机制。要评估一个内核的实时响应能力,一个关键的性能指标就是 中断延迟 。今天,我们就来深入探讨 ARM Cortex-M 系列内核的中断延迟概念,并介绍一种实用的测量方法。

什么是系统中断延迟?

中断延迟,严格定义为从中断请求(IRQ)信号有效开始,到处理器内核开始执行对应的中断服务程序(ISR)的第一条指令为止,所经历的时间。这段等待时间是无法完全消除的,因为当内核正在执行主程序线程的代码时,一个中断事件到来,处理器需要完成一系列“收尾”和“准备”工作:接收中断通知、保存当前线程的上下文(以便中断处理后能正确返回)、然后从中断向量表中定位并跳转到 ISR 的入口地址。

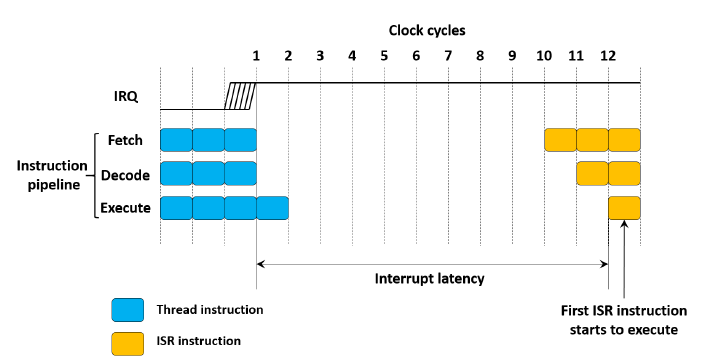

下图清晰地展示了这一过程。蓝色方块代表主线程指令在流水线中的执行,黄色方块代表 ISR 指令。箭头所指的范围,即从 IRQ 信号置起到第一个黄色 ISR 指令开始执行,这之间的时钟周期数就是中断延迟。

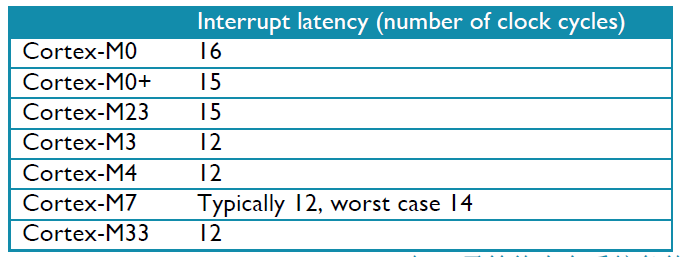

ARM Cortex-M 家族成员众多,从入门级的 M0/M0+ 到高性能的 M7/M55,它们的中断延迟因内核架构和流水线设计的不同而有所差异。下表列出了部分常见 Cortex-M 内核在理想条件(即代码运行在零等待存储器中,如同频的 SRAM)下的中断延迟周期数。

注意:

- 单位是内核时钟周期。

- 实际应用中,如果代码存放在有等待状态的 Flash 中(这在许多高频 MCU 中很常见),中断延迟会受到存储器访问速度的影响而增加。

如何测量系统中断延迟?

测量中断延迟的方法有很多,原则上任何能触发中断的外设模块都可以用于测试。对于 Cortex-M 内核而言,中断延迟主要取决于内核自身的响应流程,与具体是哪个外设触发的中断关系不大(可能只受该外设内部信号同步电路的一两个周期影响)。

其中,利用通用输入输出(GPIO)模块进行测量是最为直观和简单的方法。其基本思路如下:

- 准备两个 GPIO 引脚:一个配置为输入(

GPIO_IN),用于接收外部中断信号;另一个配置为推挽输出(GPIO_OUT),初始化为高电平。

- 开启

GPIO_IN 的边沿中断(例如下降沿)。

- 在

GPIO_IN 的中断服务函数中,快速地对 GPIO_OUT 引脚进行两次电平翻转。

- 使用示波器同时捕获

GPIO_IN 和 GPIO_OUT 的波形,通过测量两个信号边沿的时间差来计算中断延迟。

对应的伪代码示例如下:

uint32_t s_pin_low = 0x0;

uint32_t s_pin_high = 0x1;

void GPIO_IN_IRQHandler(void)

{

GPIO_OUT->DR = s_pin_low; // 第一次翻转:高变低

GPIO_OUT->DR = s_pin_high; // 第二次翻转:低变高

ClearInterruptFlag(GPIO_IN); // 清除中断标志

__DSB(); // 数据同步屏障,确保操作完成

}

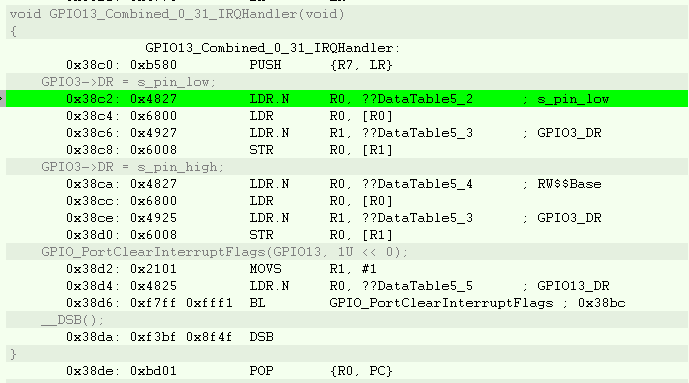

你可能会问,为什么要在 ISR 里翻转两次输出引脚?这并非多余操作。我们来看一下上述 C 代码在实际编译后(以 IAR 无优化为例)生成的汇编指令。可以看到,每一条简单的赋值语句 GPIO_OUT->DR = ... 实际上被编译成了多条 LDR(加载)和 STR(存储)指令。

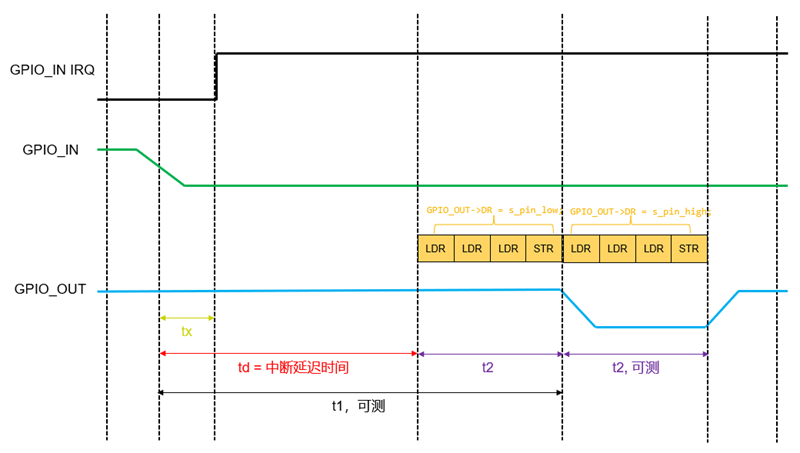

我们用来计时的 GPIO_OUT 的第一个下降沿,发生在 ISR 中执行完第一条翻转语句之后。而中断延迟的定义并不包含执行第一条 ISR 指令的时间。由于指令流水线、缓存等因素,从理论上去精确计算这几条指令的执行周期比较繁琐。更直接的方法是:在 ISR 中紧接着再执行一次翻转操作(拉高引脚),然后用示波器测量 GPIO_OUT 引脚低电平的持续时间 t2。这个 t2 就可以近似认为是执行那几条指令所花费的时间。

因此,最终的中断延迟时间 td 可以通过测量得到的两个时间值计算得出:td = t1 - t2。整个测量过程的时序关系如下图所示:

此外,图中还有一个 tx 时间段,它代表从 GPIO_IN 引脚的电平跳变到芯片内部 NVIC 模块真正识别并置起中断请求信号所需的时间。这部分时间是芯片 计算机系统 设计带来的信号同步延迟,本不属于处理器内核的中断延迟范畴,但在这种外部测量方法中无法将其分离,因此会被计入最终结果,可以将其视为一个微小的系统误差。

理解中断延迟的原理和测量方法,是进行 嵌入式系统 深度优化和实时性评估的基础。希望本文能为你剖析芯片的实时性能提供清晰的思路。你可以在 云栈社区 找到更多关于底层系统、内核机制以及性能调优的深度讨论与技术资源。 |