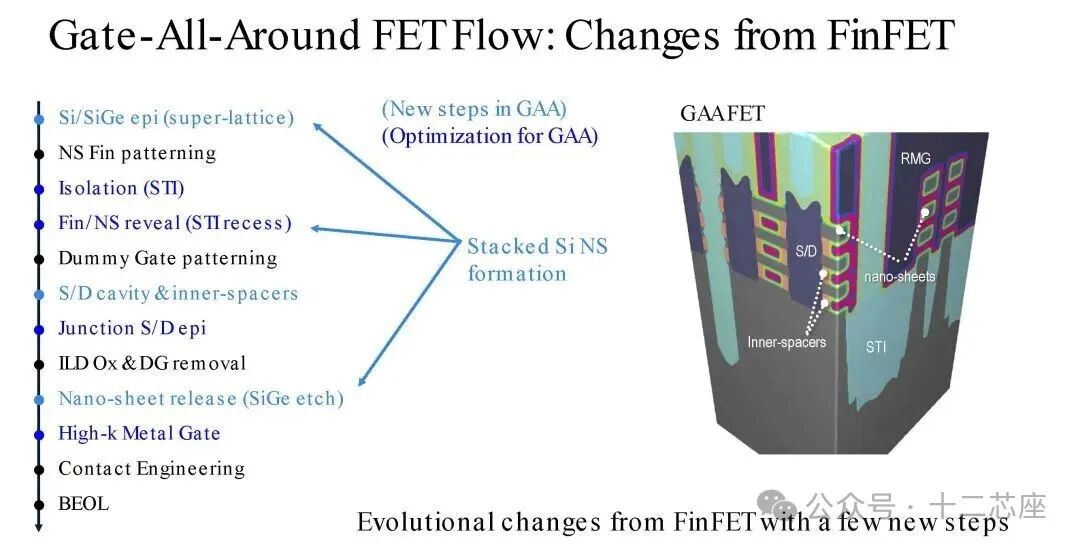

随着集成电路制程持续迈向3nm及以下节点,传统的FinFET(鳍式场效应晶体管)因其三面栅控能力的局限,已难以有效抑制日益严重的短沟道效应。为应对这一挑战,GAAFET(全环绕栅极晶体管)应运而生。它通过将栅极材料完全包裹在纳米片通道的四周,实现了近乎完美的电子控制能力。

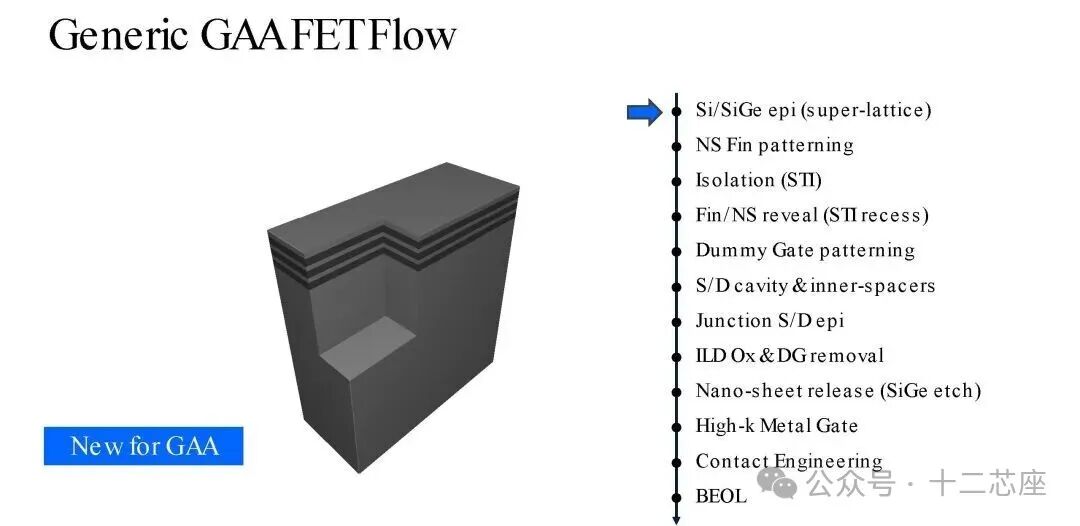

1. 超晶格外延生长

制造流程始于在硅衬底上交替生长硅(Si)和硅锗(SiGe)的多层外延结构,形成所谓的超晶格。

- 工艺细节:通常使用化学气相沉积技术来精确控制每一层的厚度。

- 核心逻辑:SiGe层在此处充当“牺牲层”,为后续步骤腾出空间;而Si层则是最终承载电子流动的通道。

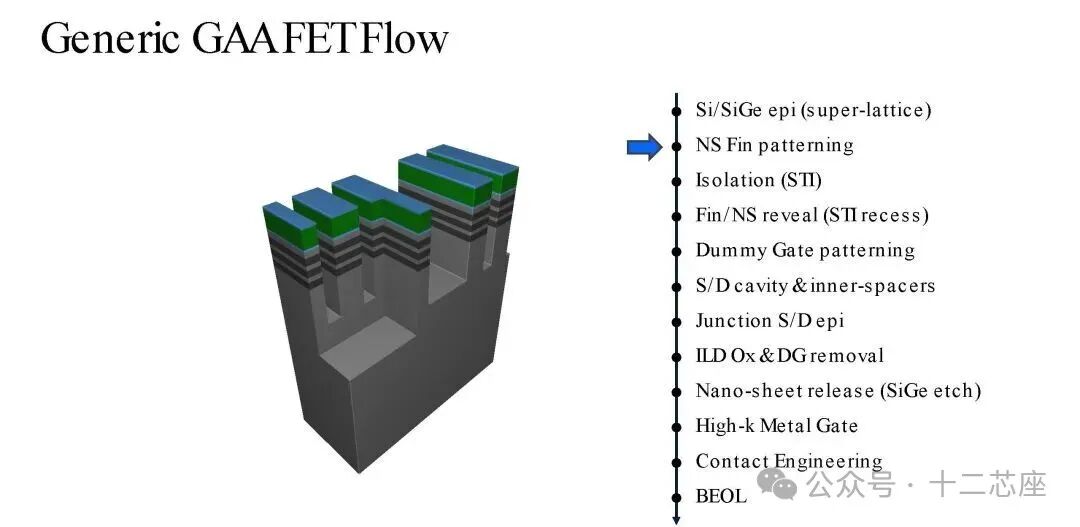

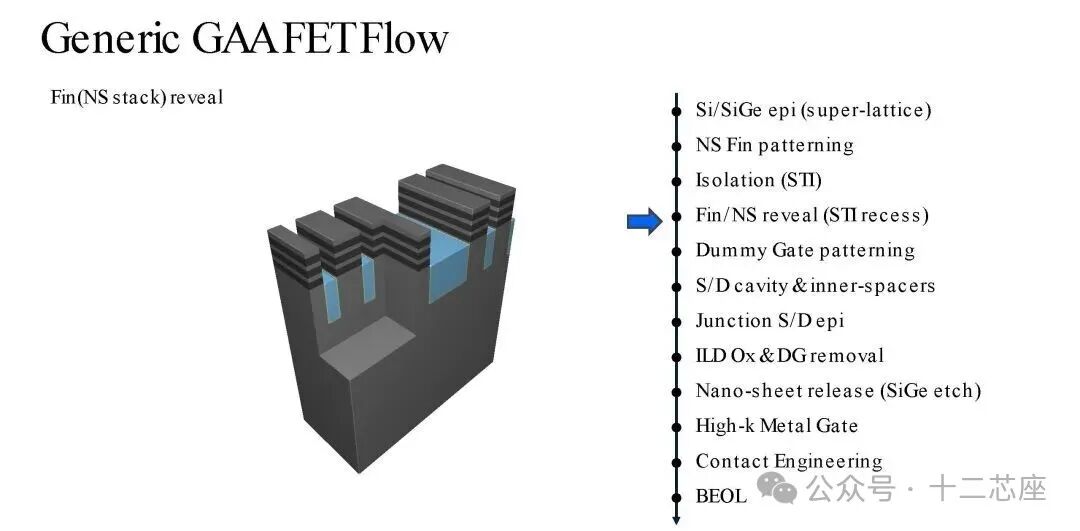

2. 纳米鳍图案化与浅沟槽隔离

此步骤与FinFET工艺有相似之处。通过光刻和干法刻蚀技术,将上一步形成的超晶格堆叠结构切割成垂直的条状“鳍”。

- 主要挑战:刻蚀过程必须保持极高的垂直度和各向异性,以确保多层Si/SiGe堆叠结构的侧壁光滑平整,这对后续的栅极包裹至关重要。

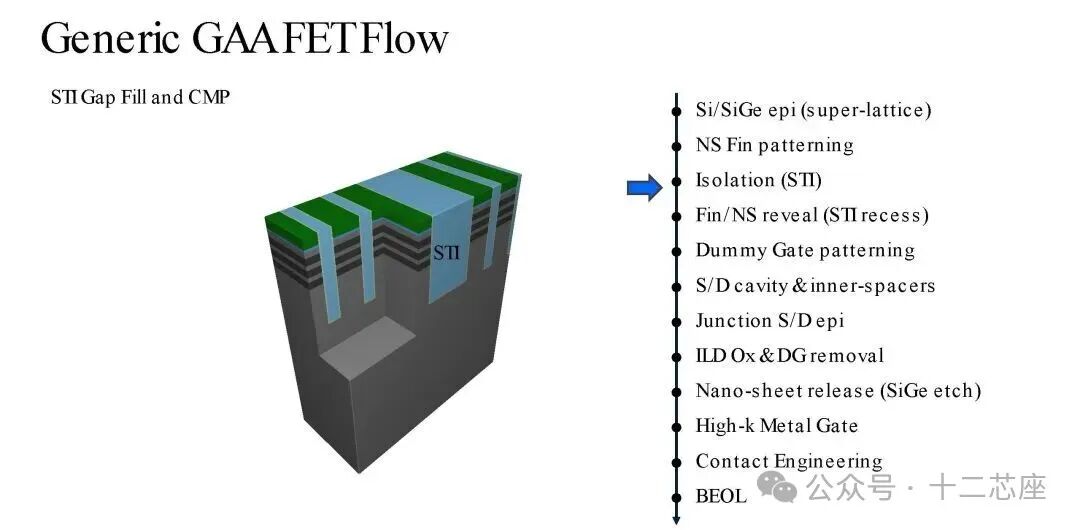

随后,进行浅沟槽隔离填充与化学机械抛光,将各个鳍结构电学隔离。

刻蚀掉部分填充材料,使纳米鳍堆叠结构显露出来。

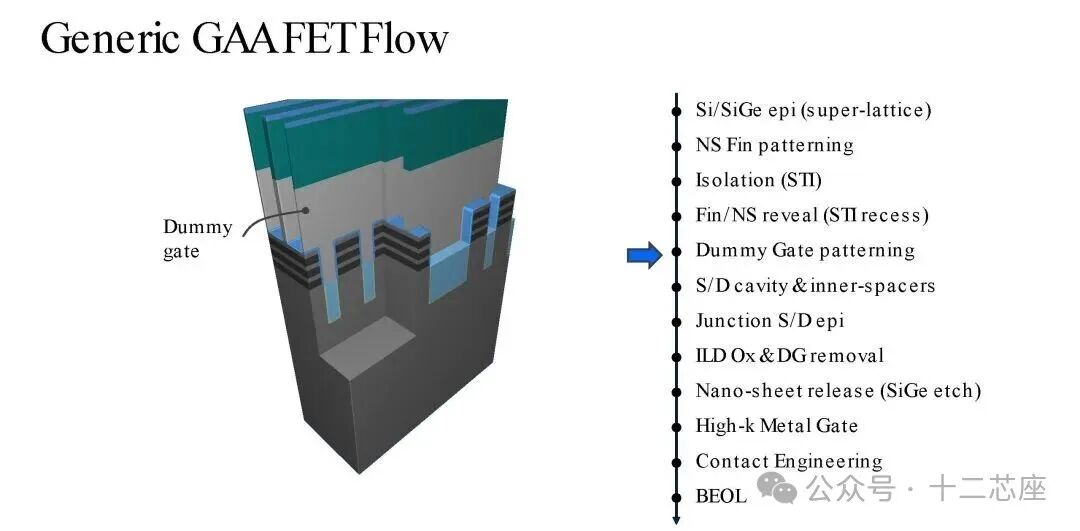

3. 虚拟栅极形成

在显露的鳍结构上,沉积并图案化形成虚拟栅极。这个栅极是临时性的,其作用是定义后续源漏区的位置,并在一系列复杂工艺中保护下方的沟道区域。

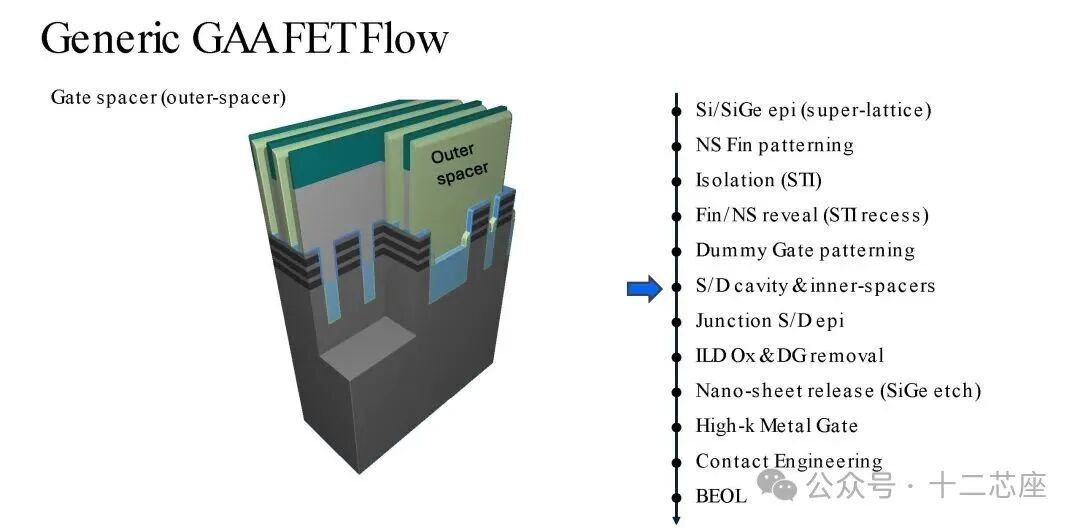

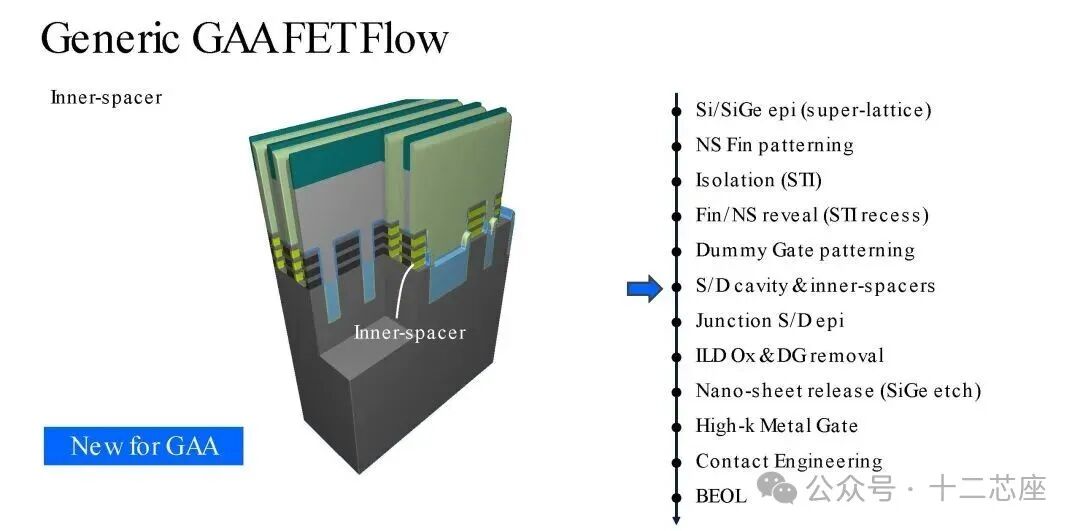

4. 内侧墙形成:GAA工艺的关键一步

这是GAA制造流程中区别于FinFET的最独特且关键的一步。在虚拟栅极两侧,需要侧向(各向同性)刻蚀掉一部分SiGe牺牲层,然后填充介电材料,从而形成内侧墙。

- 核心作用:内侧墙将后续形成的源极和漏极与最终的金属栅极物理隔离开。这一设计极大地降低了栅极-源极和栅极-漏极之间的寄生电容,对于提升晶体管开关速度、降低功耗至关重要。

- 技术难点:必须使用具有极高选择比的刻蚀工艺,确保只精确移除预定深度的SiGe层,而丝毫不会损伤相邻的Si沟道层。

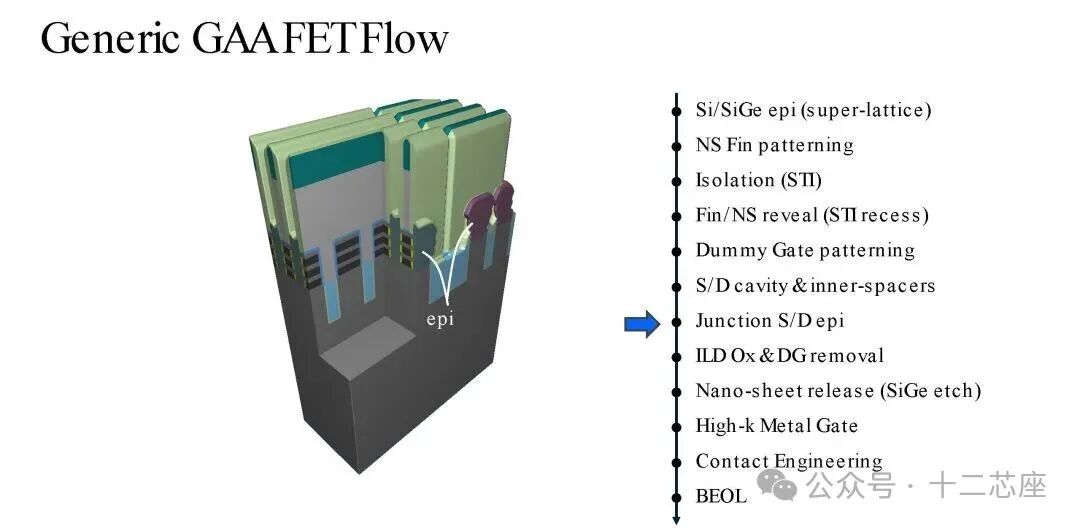

5. 源漏区外延生长

在虚拟栅极两侧的凹槽内,通过外延工艺选择性生长掺杂的硅(如SiP用于NMOS,SiGeB用于PMOS),形成晶体管的源极和漏极区域。

随后沉积层间介质并平坦化。

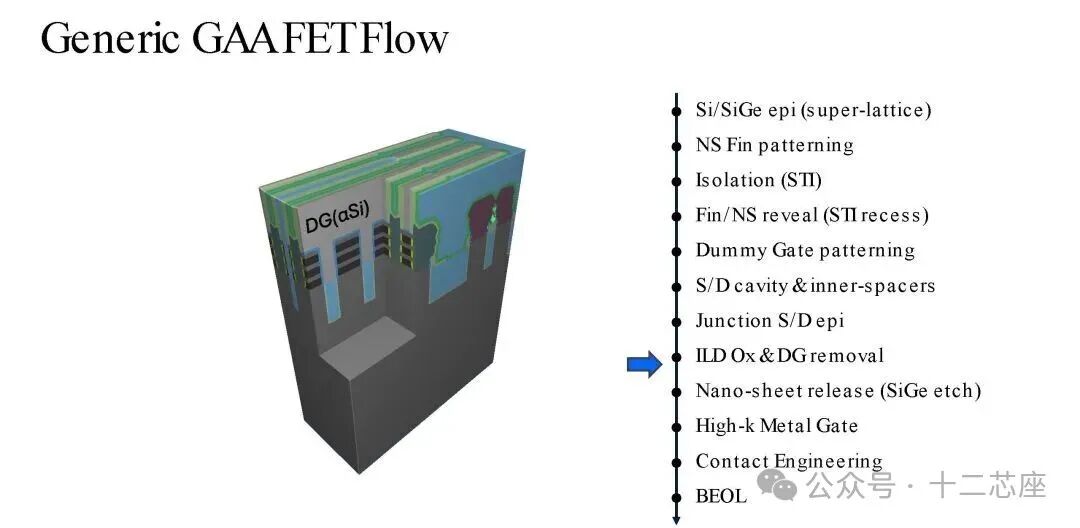

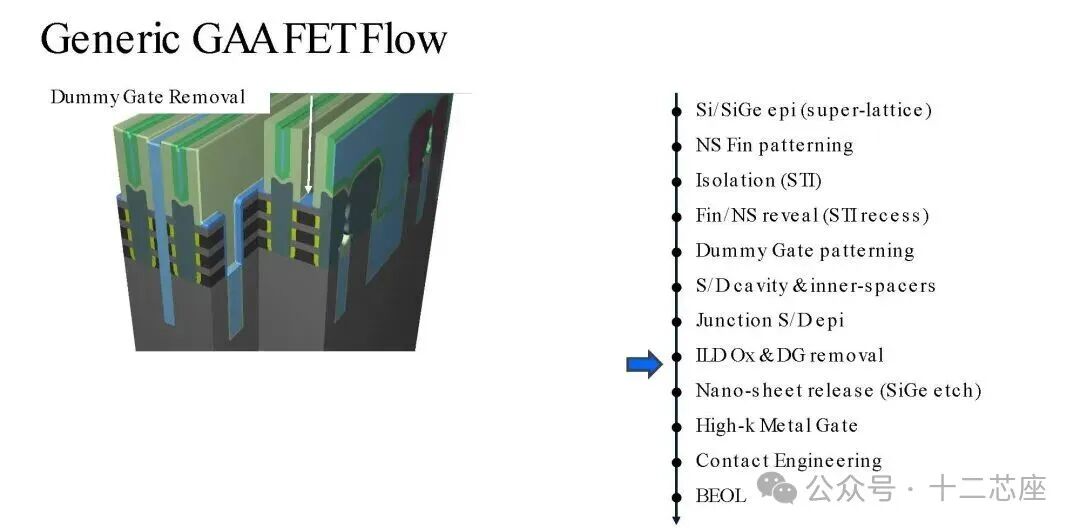

移除虚拟栅极是替换金属栅工艺的核心步骤之一。

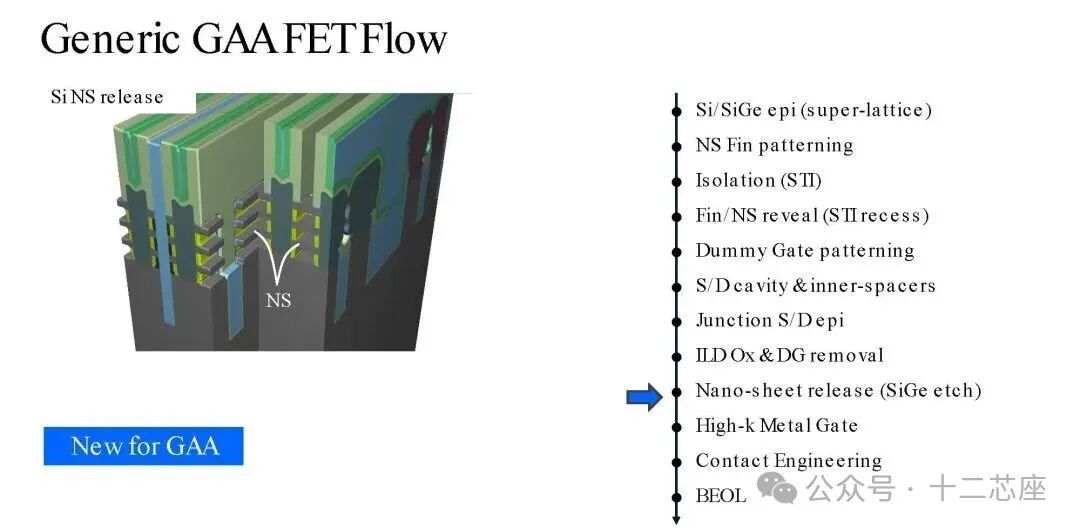

6. 纳米片沟道释放

在虚拟栅极被移除后,通过高选择比的湿法或干法刻蚀,将作为牺牲层的所有SiGe层彻底清除。这样一来,多层Si纳米片就如同“悬空的桥”一般,仅由其两端的源极和漏极支撑。

- 物理瓶颈:此时的Si纳米片极其纤细和脆弱,液体干燥过程中的表面张力或工艺应力都可能导致纳米片塌陷并相互粘连,这是制造中的重大挑战之一。

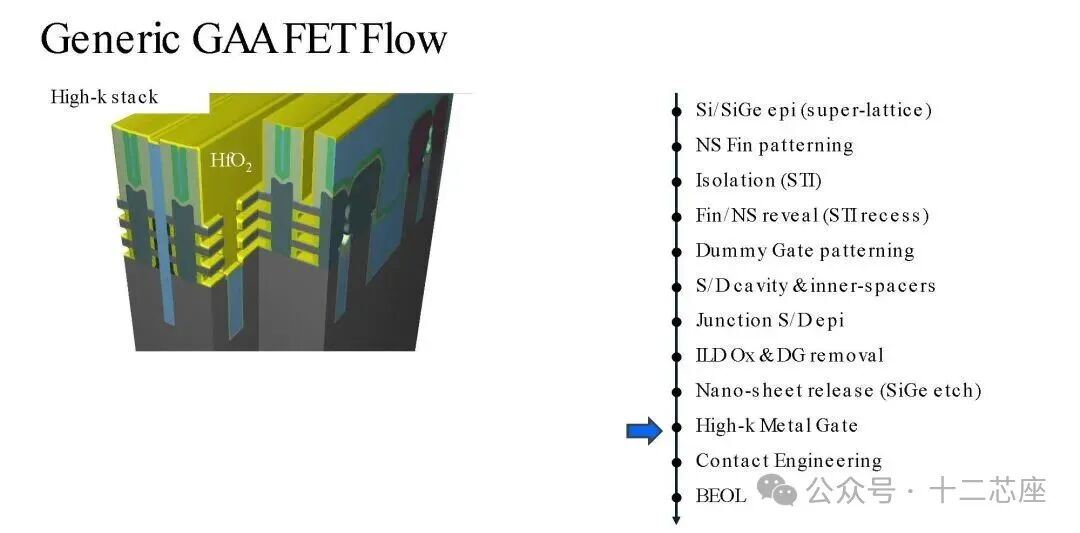

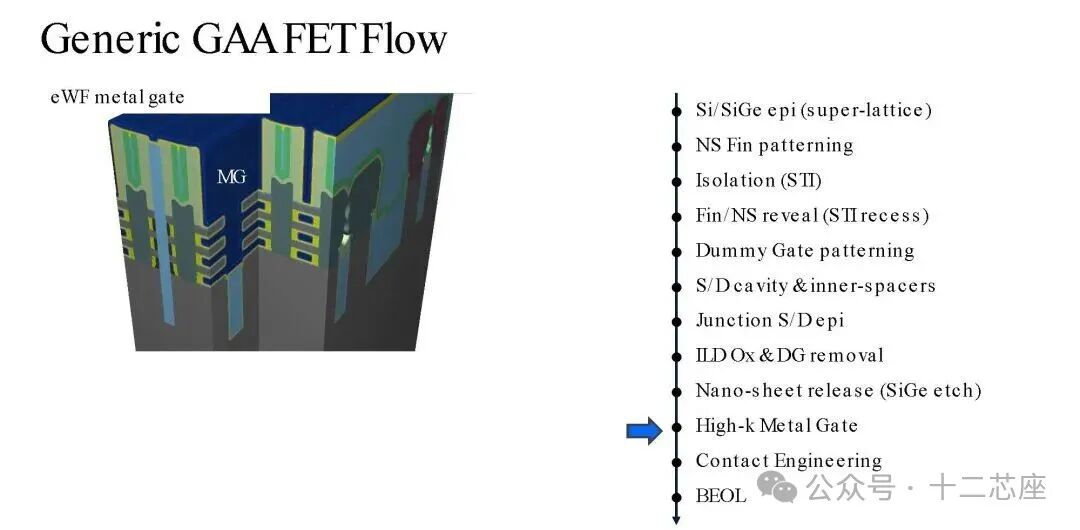

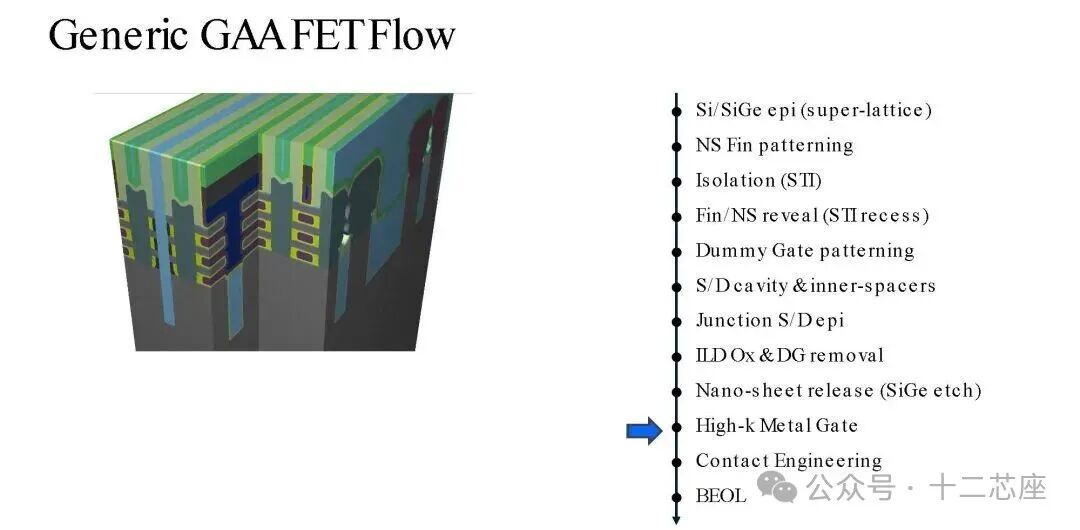

7. 高K金属栅极沉积

最后,也是实现“全环绕栅极”控制的关键一步:利用原子层沉积技术,将高K栅介质和金属栅极材料依次沉积到纳米片四周及片与片之间的极小缝隙中。

- 均匀性要求:ALD工艺必须保证在纳米片的顶面、底面和两个侧面都均匀成膜,实现真正的全环绕包裹,从而获得最强的栅控能力。

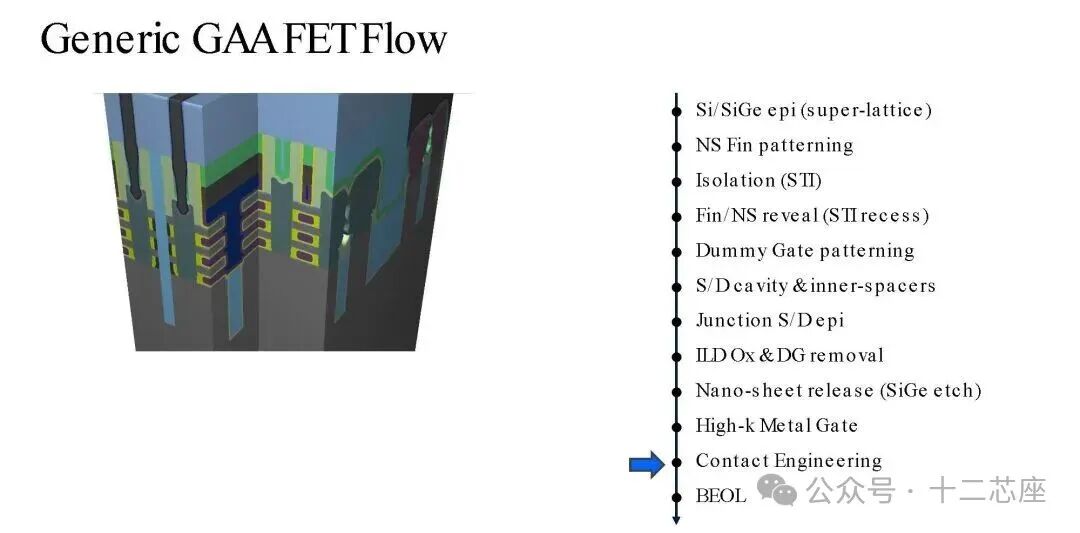

8. 接触工程与后端互连

完成栅极沉积后,进行接触孔刻蚀和金属填充,形成与源极、漏极和栅极的电学连接。随后进入标准的后端互连工艺,通过多层金属布线将数十亿个这样的晶体管连接成复杂的集成电路。

通过上述一系列高度精密的步骤,GAAFET成功地将晶体管沟道从FinFET的“竖鳍”转变为多层“纳米片”,并通过栅极的全面包裹,为先进制程芯片的性能和能效提升奠定了物理基础。对半导体制造工艺细节的深入探讨,欢迎在云栈社区继续交流。

参考来源:

- 2025 IEDM Short Course

- AMAT 技术资料

|