DRAM,全称为 Dynamic Random Access Memory,即动态随机存取存储器。它是我们电脑、手机等电子设备中至关重要的内存部件,负责为处理器(CPU)提供高速的数据读写空间。

那么,它为什么被称为“动态”的呢?这恰恰是DRAM最核心的特点。

DRAM的两大核心特点

1. 动态存储

DRAM需要不断地“刷新”才能保持数据。这源于其存储数据的基本原理:利用电容存储电荷。电容就像一个小型充电电池,当它充满电时,表示数据“1”;当它没电时,表示数据“0”。但电容存在漏电问题,电荷会随时间慢慢流失。为了防止数据丢失(比如“1”变成“0”),必须定期对电容进行“刷新”——即读出数据并重新写入,以补充电荷。

2. 随机存取

这与我们熟悉的硬盘(顺序存取)不同。DRAM允许CPU直接、快速地访问任意一个存储单元进行读写,而不必像磁带那样按顺序从头找到尾。这为实现高速数据交换提供了基础。

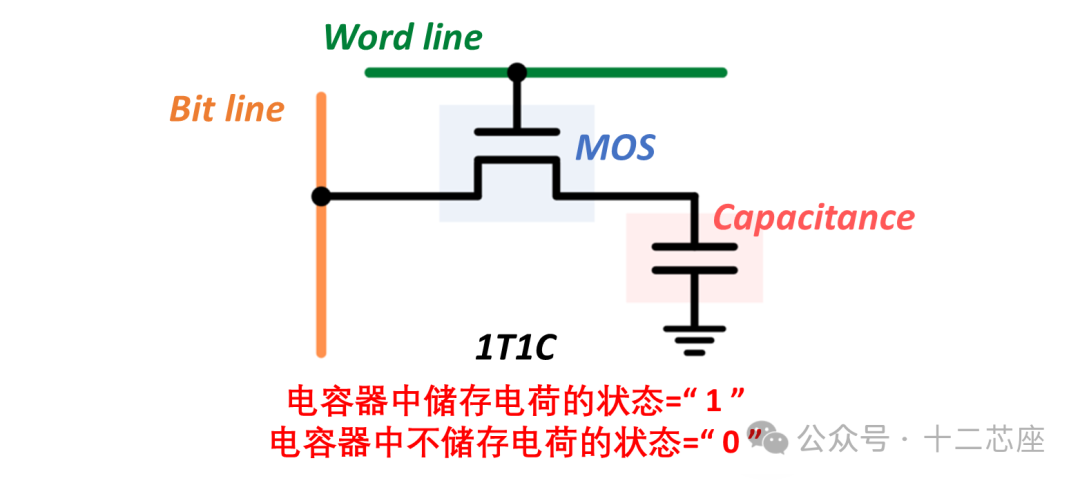

DRAM的基础结构:1T1C存储单元

DRAM存储数据的最小单元被称为“存储单元”,其经典结构是1T1C。

如上图所示,一个存储单元主要由一个晶体管(MOSFET)和一个电容(Capacitance)组成,这也是“1T1C”(一个晶体管,一个电容)名称的由来。

- 电容(Capacitor):存储数据的核心。充电状态代表“1”,放电状态代表“0”。

- 晶体管(Transistor):充当一个开关。当开关打开时,电容与外部电路(位线)连通,可以进行数据的读写;当开关关闭时,电容与外界隔离,保持其电荷状态。

这个简单的单元通过两条关键的线连接到控制电路:

- 字线(Word Line, WL):连接晶体管的栅极。它的作用是“寻址”。当字线被激活(施加高电压)时,这一整行上所有存储单元的晶体管开关都会打开,相当于选中了这一行。

- 位线(Bit Line, BL):连接晶体管的源极或漏极。它的作用是传输数据。当某一行被字线选中后,数据的具体读写操作就通过每一条位线来完成。

理解了这个基本结构,我们就可以深入其工作的三个核心环节:写入、读取和刷新。

DRAM的工作原理

在工作时,我们通常将字线或位线的高电平状态称为 High (H),低电平状态称为 Low (L)。

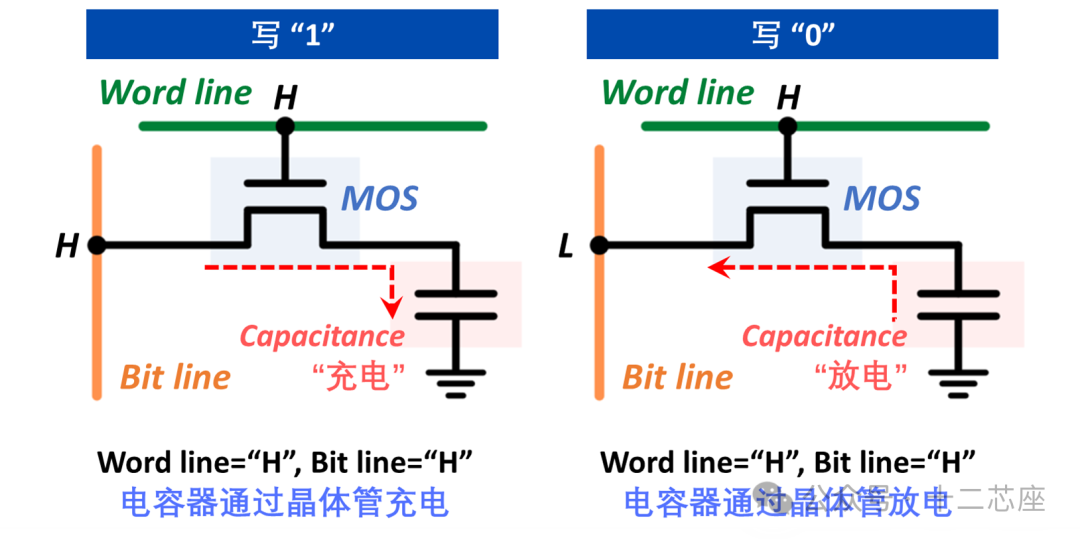

1. 写入操作

写入就是向电容中“灌入”或“抽走”电荷,从而设定其存储的是“1”还是“0”。

- 选中单元:首先,通过激活目标存储单元对应的字线(WL=H),打开该单元的晶体管开关。

- 施加电压:在对应的位线(BL)上施加目标电压。

- 若要写入 “1”,则置位线为高电压(BL=H)。此时,电流通过导通的晶体管流入电容,为其充电。

- 若要写入 “0”,则置位线为低电压(BL=L)。此时,电容中已有的电荷(如果有)会通过导通的晶体管流出,即放电。

- 完成写入:写入完成后,关闭字线(WL=L),晶体管断开,电容与位线隔离,数据就被保存在了电容的电荷状态中。

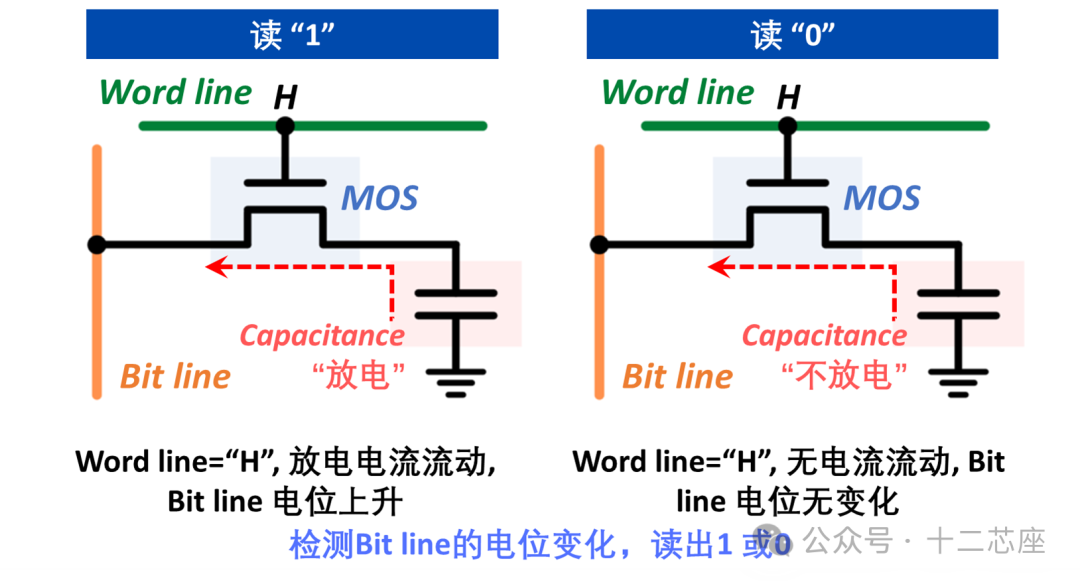

2. 读取操作

读取则是感知电容的电荷状态,并将其转换为外部电路可以识别的信号。关键在于,DRAM的读取是一种 “破坏性读出”。

- 选中单元并连通:同样,先激活字线(WL=H),打开晶体管开关,使电容与位线连通。

- 检测电荷变化:位线在读取前会被预充到一个特定的中间电压。

- 如果电容存储的是 “1”(充满电荷),那么当它与位线连通时,电容会向位线放电。由于电荷的流入,会导致位线的电压产生一个微小的上升。

- 如果电容存储的是 “0”(没有电荷),那么当它与位线连通时,电荷会从位线流向电容(或无明显流动),导致位线电压产生一个微小的下降或基本不变。

- 信号放大与判定:位线上这种极其微弱的电压变化会被一个非常灵敏的放大器(Sense Amplifier)检测并放大,最终被判定为逻辑“1”或“0”。

- 数据重写:由于读取过程改变了电容的电荷状态(放电了),所以在读取操作后,必须立即将刚刚读出的数据重新写回该存储单元,以恢复其原有的电荷量。这一步通常由电路自动完成。

3. 刷新操作

刷新操作的本质,其实就是一次完整的 “读取+重写” 过程。即使某个存储单元长时间没有被CPU访问,控制电路也会定期、逐行地对所有存储单元执行刷新,以补充电容漏电损失的电荷,确保数据不会丢失。这是DRAM“动态”特性的直接体现,也是其与不需要刷新的SRAM(静态内存)的主要区别之一。

总结来说,DRAM的工作原理围绕着小电容的电荷存储展开,通过精密的行列寻址、灵敏的电荷检测与放大电路,以及不可或缺的定期刷新机制,共同实现了高速、大容量的数据存储功能。理解了这些基础的计算机组成原理和电路原理,有助于我们更好地把握现代计算机内存系统的运行脉络。

如果想更系统地探索这类底层硬件知识,欢迎来云栈社区的计算机基础板块,与更多开发者交流讨论。

Reference:

- Semiconductor Devices Physics and Technology.

|