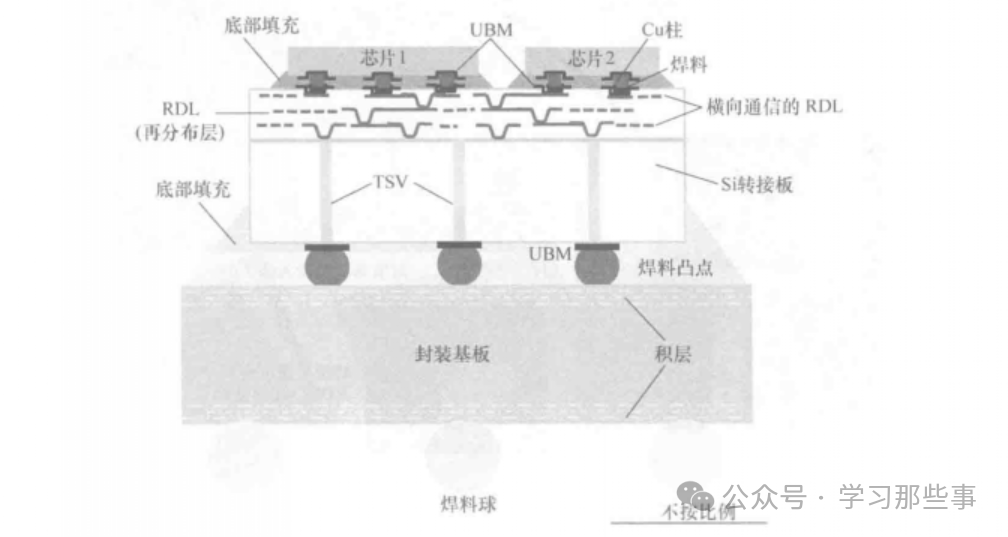

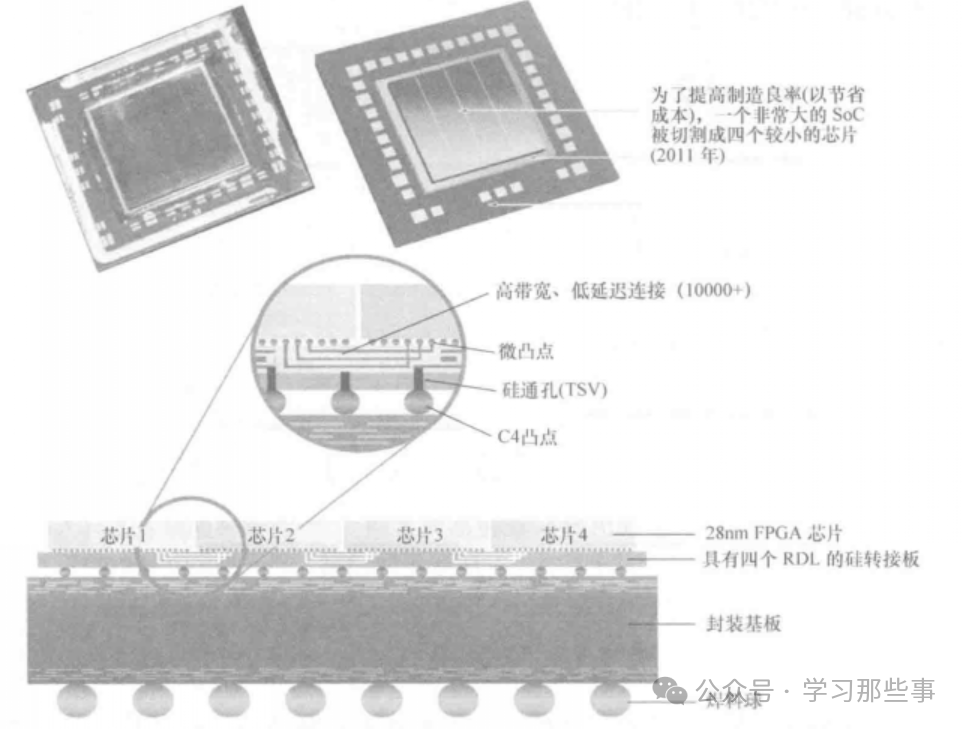

2.5D IC集成在实现宽I/O接口方面扮演着至关重要的角色。其核心架构包含两部分:一块采用了TSV(硅通孔)技术的无源硅片,以及一块或多块本身不含TSV的高性能、高密度IC芯片。这块无源硅片也常被称为无源转接板,它不仅为上层芯片提供物理支撑,其表面的RDL(再分布层)更是实现芯片间横向高速互连的关键。下图展示了这种集成方式的典型结构。

随着芯片集成度和引脚数量的爆炸式增长,同时芯片衬底的间距与尺寸却在不断微缩,传统的封装基板已经难以满足需求。引入中间基板(即无源转接板)成为解决这一瓶颈的有效方案。下面几张图展示了该技术在实际产品中的应用案例。

TSV/RDL无源转接板的实际应用

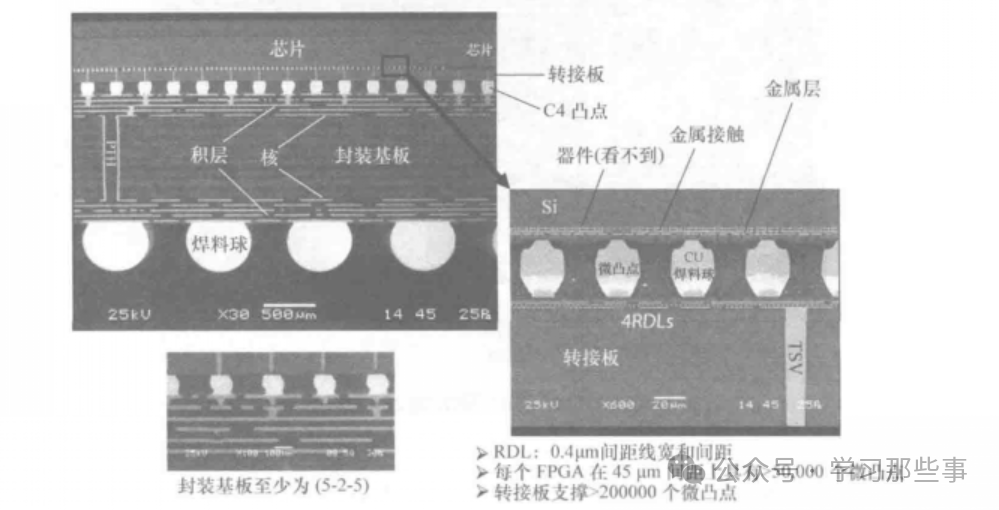

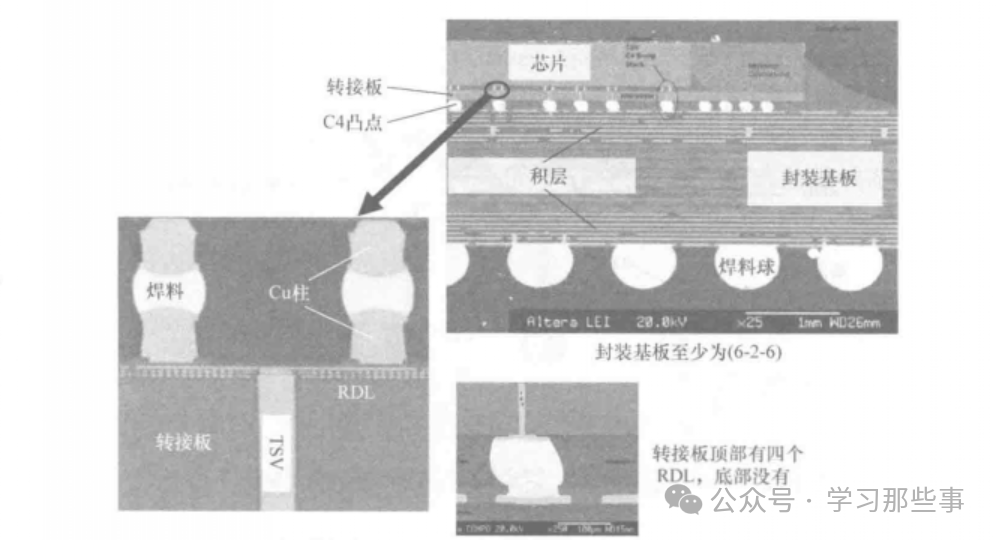

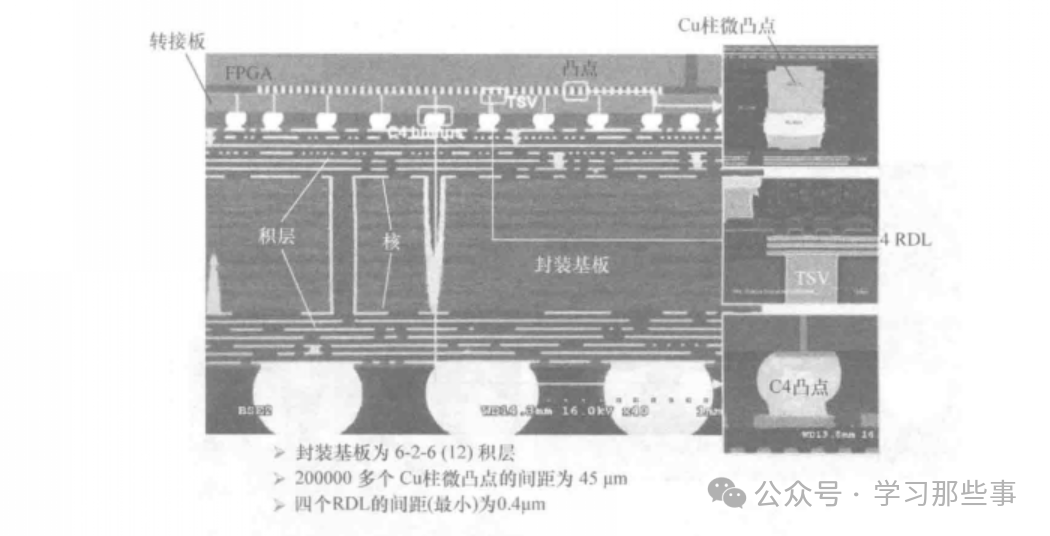

从上面的实际样品中可以清晰地看到,即便封装基板已经采用了多达12层的积层结构(6-2-6设计),仍然无法满足四颗28纳米工艺FPGA芯片的极致互连需求。因此,必须引入一块具备四个顶部RDL层(包含三个铜大马士革层和一个铝层)的TSV硅转接板。这块转接板上的TSV直径约为10微米,深度约为100微米。

为什么要如此大费周章?核心原因在于提升制造良率和控制成本。采用台积电28纳米工艺制造的大型SoC芯片,为了获得更好的良率,会被切割成四个较小的FPGA芯片。这四颗FPGA芯片之间高达一万多个的横向互连,主要就是依靠转接板上线宽和间距最小可达0.4微米的RDL来实现的。

RDL与钝化层的总厚度最小可控制在1微米左右。每颗FPGA芯片上集成了超过五万个带有焊料帽的铜柱微凸点,而整块转接板上的微凸点总数更是超过了二十万个,凸点间距为45微米。这些细节均可在上图中找到对应。由此可见,无源TSV/RDL转接板是应对极细间距、超高I/O数量、高性能和高密度半导体应用的理想选择。

转接板的制造

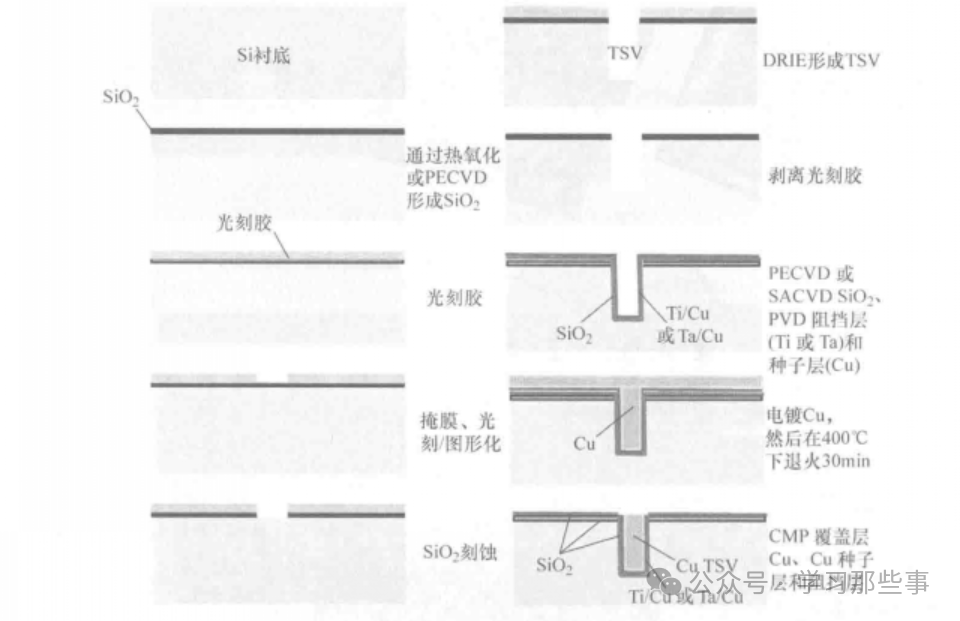

转接板的制造核心围绕两个关键工艺展开:TSV制造和RDL制造。下面我们来详细拆解这两个环节。

TSV的制造

TSV的典型制造流程如下图所示。工艺始于在硅衬底上通过热氧化或等离子体增强化学气相沉积(PECVD)形成SiN/SiO₂绝缘层。随后进行光刻胶涂覆和图形化,定义出TSV的位置。接着,采用Bosch工艺的深反应离子刻蚀(DRIE)技术在硅衬底上刻蚀出深宽比高达10.5的通孔。

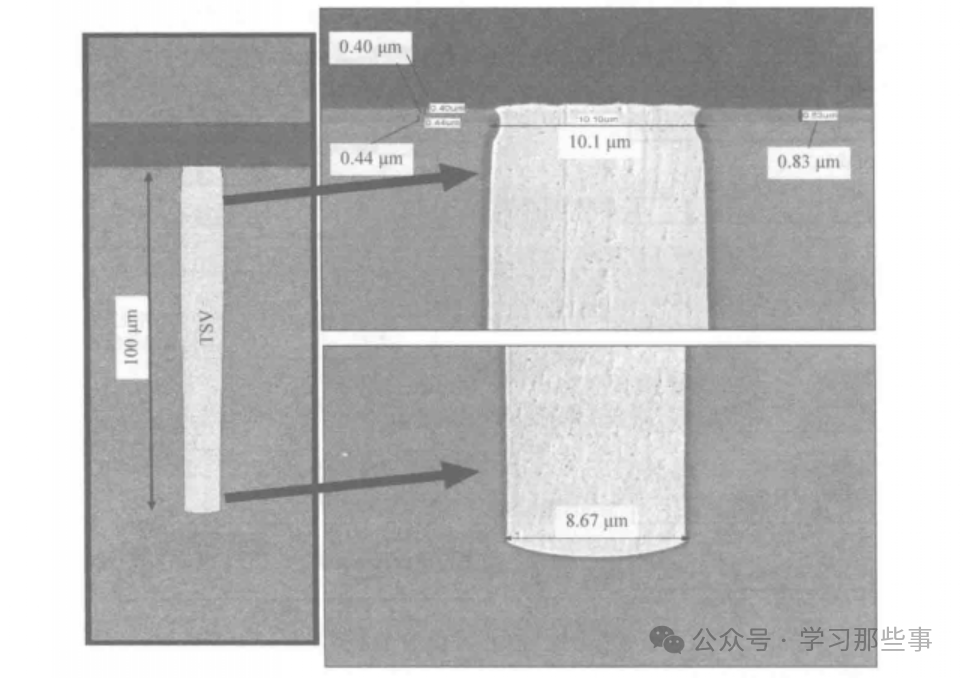

刻蚀完成后,通过亚大气化学气相沉积(SACVD)工艺在蚀刻出的孔洞内壁沉积SiO₂衬垫。然后依次沉积Ta阻挡层,并采用物理气相沉积(PVD)技术形成铜种子层,最后通过电镀工艺填充铜。最终形成的盲孔TSV,其顶部开口直径约10微米,深度约105微米,深宽比保持在10.5。由于孔洞深宽比大,电镀时需要采用自下而上的填充机制,以确保孔内无缝隙且表面铜层厚度均匀。

上图是TSV横截面的扫描电子显微镜(SEM)图像,可以观察到TSV底部直径略有收窄,这是刻蚀工艺中的常见现象。表面的场区铜层厚度被控制在5微米以内。电镀完成后,需要在400℃环境下进行30分钟的退火处理。最后,通过化学机械抛光(CMP)工艺去除表面多余的铜层,完成TSV的制造。

RDL的制造

目前,RDL的制造主要有两种成熟的技术路线。

第一种方法是采用聚合物作为钝化介质层。常用的聚合物材料包括聚酰亚胺(PI)、苯并环丁烯(BCB)、聚苯并双恶唑(PBO)等,金属导线层则通过电镀铜工艺形成。这种方法被许多外包半导体组装和测试(OSAT)厂商广泛采用,因为它无需昂贵的半导体前道设备,适用于晶圆级芯片尺寸封装(WLCSP)、扇出型封装等场景。

第二种方法是铜大马士革工艺,它由传统的半导体后道互连工艺演变而来,专门用于制造铜金属的RDL。上文图3至图5中展示的RDL结构正是采用此法制造。总体而言,铜大马士革工艺能够实现更薄的介质层和铜导线,获得更精细的线宽与间距,以及更高的集成精度。关于这两种工艺更详细的步骤和对比,我们将在后续的文章中深入探讨。

对半导体封装技术和先进集成工艺感兴趣的开发者,可以持续关注相关讨论。希望这篇关于2.5D集成与宽I/O接口的解析,能帮助你理解现代高性能芯片背后的架构奥秘。欢迎在云栈社区分享你的见解或提出更多技术问题。 |