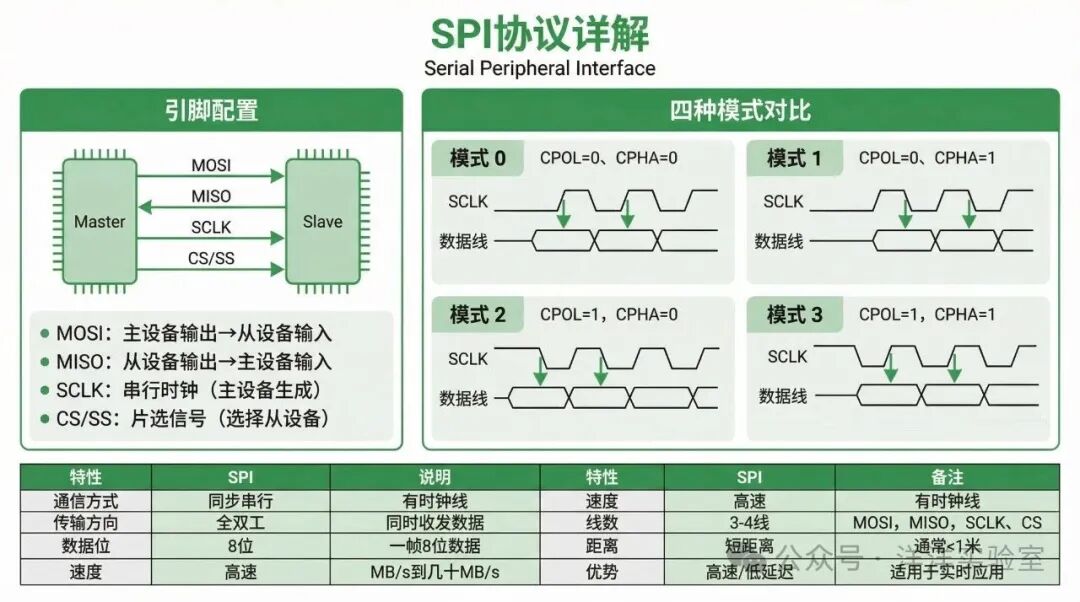

SPI(Serial Peripheral Interface,串行外设接口)是一种同步、串行、全双工的通信方式。得益于其高速、协议简单的特点,它被广泛应用于存储芯片(如FLASH、SD卡)、显示模块(如LCD、OLED)等设备与主控芯片之间的数据交换。

SPI通信区分主机(Master)和从机(Slave),产生并输出时钟信号的一方为主机。标准的SPI通信需要4根信号线:

- SCLK:串行时钟,由主机产生。

- MOSI:主设备输出、从设备输入。

- MISO:主设备输入、从设备输出。

- CS/SS:从设备选择(Slave Select)信号,也称为片选(Chip Select)信号。

通信过程由主机发起。从机需要检测CS/SS信号,仅当该信号有效(通常为低电平)时,才会响应通信。同时,通信双方必须约定并遵守相同的时钟极性(Clock Polarity,CPOL)和时钟相位(Clock Phase,CPHA)特性:

- CPOL:时钟极性,决定了总线空闲时SCLK的电平状态(0=低电平,1=高电平)。

- CPHA:时钟相位,决定了数据在时钟的哪个边沿被采样(0=第一个边沿,1=第二个边沿)。

CPOL与CPHA的不同组合,构成了SPI的四种工作模式。其中,Mode 0和Mode 3在实际应用中最为常见。

深刻理解时序是掌握任何通信协议的关键。对于开发者而言,配置正确的SPI模式是确保设备间正常通信的第一步。

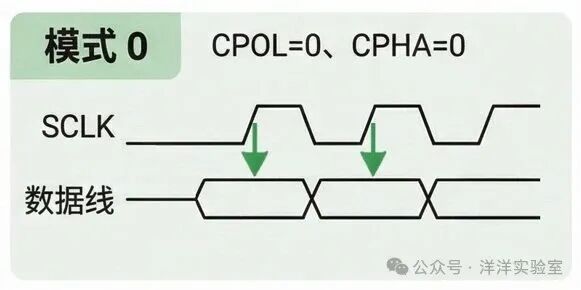

SPI 模式0详解

在模式0下,总线空闲时SCLK保持低电平(CPOL=0),数据在SCLK的第一个边沿(即上升沿)被采样(CPHA=0)。这意味着数据在时钟的上升沿时刻必须保持稳定。

SPI 模式1详解

模式1与模式0的时钟空闲状态相同(CPOL=0),但数据采样点不同。在模式1中,数据在SCLK的第二个边沿(即下降沿)被采样(CPHA=1)。

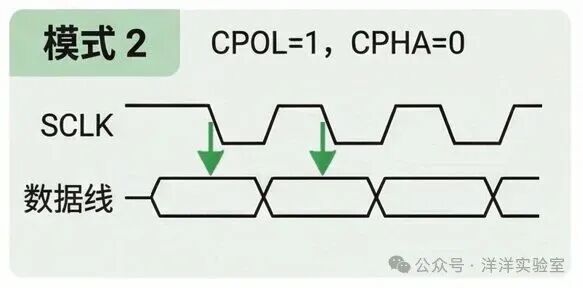

SPI 模式2详解

在模式2下,总线空闲时SCLK为高电平(CPOL=1)。数据在SCLK的第一个边沿(此时为下降沿)被采样(CPHA=0)。

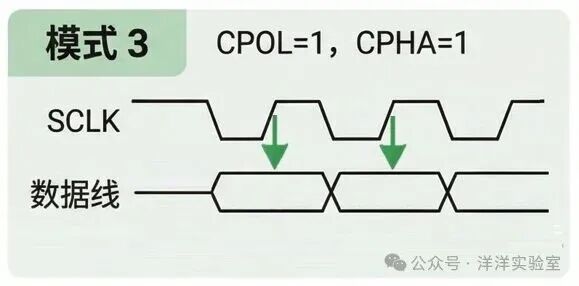

SPI 模式3详解

模式3的时钟空闲状态与模式2相同(CPOL=1),但数据采样点移到了第二个边沿(此时为上升沿,CPHA=1)。这种模式与模式0在数据采样边沿上是一致的(都是上升沿采样),但时钟空闲状态相反。

SPI通信特性小结

- 传输单位:SPI以字节为单位进行传输,通常采用高位在前(MSB First)的格式。

- 流式传输:进行多字节传输时,字节之间通常无需插入等待周期,可以实现连续的数据流传输。

- 会话控制:通信的开始和结束由片选信号(CS/SS)的拉低和拉高来控制。

尽管硬件上SPI接口比UART、I²C需要更多的引脚,但它提供了一种更为高效的全双工通信方式,在要求高速数据传输的嵌入式场景(如读写Flash存储器)中具有不可替代的优势。如果你想深入探讨更多底层通信原理或嵌入式开发技术,欢迎在云栈社区交流分享。 |