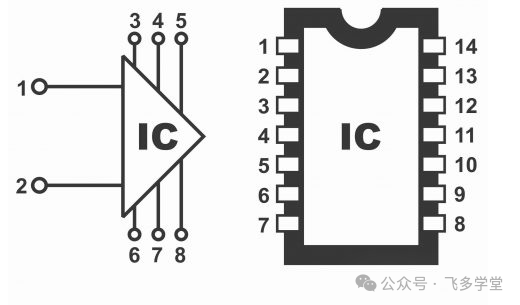

在绘制电子电路的原理图时,如何表示一个集成电路(IC)的符号?这看似基础,却直接影响着设计的效率与可靠性。通常,IC的电路符号有两种主流分类,它们各有侧重,适应不同的设计场景:

- 引脚真实位置视图 (Pin-accurate View):也叫物理视图或引脚排布视图。

- 功能分组视图 (Functional-grouped View):也叫逻辑视图。

🟦 引脚真实位置视图 (Pin-accurate View)

核心特点

- 严格遵循物理引脚顺序:符号中引脚的排列顺序与芯片数据手册(Datasheet)以及实际封装的引脚编号完全一致,通常按照逆时针或顺时针规则排列。

- 为PCB布局而生:最直接方便在绘制PCB时进行对照检查。

- 适合简单器件:常用于运算放大器、逻辑门、LDO、MOSFET等引脚数较少的元件。

优点分析

- 连接最可靠:严格按照物理引脚绘制,原理图连线时最不容易接错引脚。

- 对照直观:在进入PCB布局阶段,工程师对照Datasheet检查连线、进行内存管理和信号走线时,这种视图提供了最直观的参考。

- 小器件清晰:对于像LM358、74HC14这类引脚定义简单、功能单一的芯片,使用此视图能让原理图简洁明了。

缺点与局限

- 大芯片的灾难:当面对引脚众多的MCU、FPGA或复杂电源管理芯片(PMIC)时,所有引脚机械地排列在符号四周,会使原理图符号变得庞大且杂乱无章。

- 破坏系统性:功能上紧密相关的引脚(例如同一组GPIO或通信接口)被物理位置打散,严重妨碍阅读者对电路系统结构的理解。

- 可读性差:原理图的核心目标之一是清晰传达设计意图,而这种视图在复杂场景下恰恰损害了可读性。

🟩 功能分组视图 (Functional-grouped View)

核心特点

- 按逻辑重新组织:完全打破物理引脚的排列顺序,按照电气功能和信号类型将引脚重新分组、归类排列。

- 例如:电源组(VDD、GND)、模拟输入组(ADC)、数字IO组(GPIO)、通信接口组(I²C、SPI、UART)、控制与反馈组(EN、FB、COMP)等。

- 与封装解耦:符号中的引脚位置不再反映其在芯片封装上的实际物理位置。

优点分析

- 可读性极佳:这是它最大的优势。原理图一眼望去就能看清芯片的功能模块划分,系统架构清晰可见,极大地提升了设计文档的可维护性。

- 为复杂IC量身定制:特别适合MCU、PMIC、模拟前端(AFE)、FPGA等具有多功能模块的芯片。

- 便于绘制框图:这种分组方式与系统框图(Block Diagram)的思维方式一脉相承,方便绘制具有模块化风格的原理图,是理解复杂系统计算机基础逻辑的有力工具。

缺点与注意事项

- 不能直接用于PCB对照:这是最主要的代价。在布局PCB时,无法直接从原理图符号看出物理引脚号,必须依赖电气规则检查(ERC)、设计规则检查(DRC)或人工仔细核对封装引脚映射表。

- 初学者易混淆:新手可能会误以为符号中的引脚位置就是实际的焊接位置,导致PCB设计错误。

- 依赖工具与规范:需要严谨的库管理和设计流程来确保原理图符号与PCB封装之间映射的绝对正确。

📘 两种视图对比速查表

| 对比项目 |

引脚真实位置视图 |

功能分组视图 |

| 引脚顺序 |

与物理封装完全一致 |

与物理封装无关,按逻辑排列 |

| 原理图可读性 |

对大芯片较差 |

对大芯片极佳 |

| 适用器件类型 |

小器件、功能单一器件 |

MCU、PMIC、AFE、FPGA等复杂IC |

| PCB布局对照 |

非常方便,可直接参考 |

需要额外检查引脚号映射 |

| 利于系统理解 |

较差 |

非常清晰 |

| 典型应用场景 |

运放、逻辑门、MOSFET |

STM32、TPS系列电源芯片、各类AFE芯片 |

🧠 工程师实战经验总结

如何选择?资深工程师通常遵循以下“潜规则”:

小器件 → 首选引脚真实视图

- 运算放大器 / 比较器

- MOSFET / 晶体管

- 小型LDO / 稳压器

- 基础逻辑门电路(与门、或门等)

这些器件引脚少,功能单纯,使用物理视图既准确又不会牺牲可读性。

大型复杂IC → 必选功能分组视图

- 微控制器 (MCU):如STM32、AT32、CH32系列。

- 电源管理IC (PMIC):如TPS5430、MPM系列等多路输出芯片。

- 模拟前端 (AFE):如INA226电流传感器、ADS1115模数转换器。

- 现场可编程门阵列 (FPGA)

- 多功能电源芯片

对这些芯片而言,可读性和系统化设计远比对单个引脚的物理感知更重要。

混合模式:专业团队的常用做法

最高效且可靠的做法往往是两者的结合:

- 符号采用功能分组:在原理图层面获得最佳的清晰度和模块化。

- 标注真实引脚号:在符号的每个引脚旁,明确标注其对应的物理引脚编号(Pin Number)。

- 严格管理封装库:在PCB封装库中,确保原理图符号的引脚编号(Pin Number)与封装的焊盘编号(Pad Number)准确无误地映射。

这种“形神分离”的方法,兼顾了原理图设计的逻辑性与PCB实现的准确性,是许多顶尖半导体公司(如TI、ADI、NXP)内部推崇的最佳实践。掌握这两种视图的运用,是每位硬件工程师提升设计效率和作品质量的基础,相关的深入讨论和技术资源,也可以在云栈社区这样的专业开发者平台上找到更多同行交流。 |