关于Buck和Boost转换器的文章我已经写过不少,但专门探讨PCB布局设计的却不多。这篇就来深入聊聊这个话题。

大多数DCDC芯片的数据手册都会提供PCB布局设计指南,有些还会附上布局示意图,这些建议通常是大同小异的。

以Buck电路为例,随便列举几个常见的设计要点:

- 输入电容和二极管应与IC放在同一层,并尽可能靠近IC放置。

- 电感应靠近芯片的SW引脚,输出电容则应靠近电感。

- 反馈回路应远离电感、SW引脚和二极管等噪声源。

那么,你知道这些设计要点背后的原理是什么吗?

在实际设计中,我们常会遇到具体芯片的引脚排布并不理想的情况,此时可能无法同时满足所有要求,该怎么办?哪些是必须优先保证的,哪些可以适当妥协?

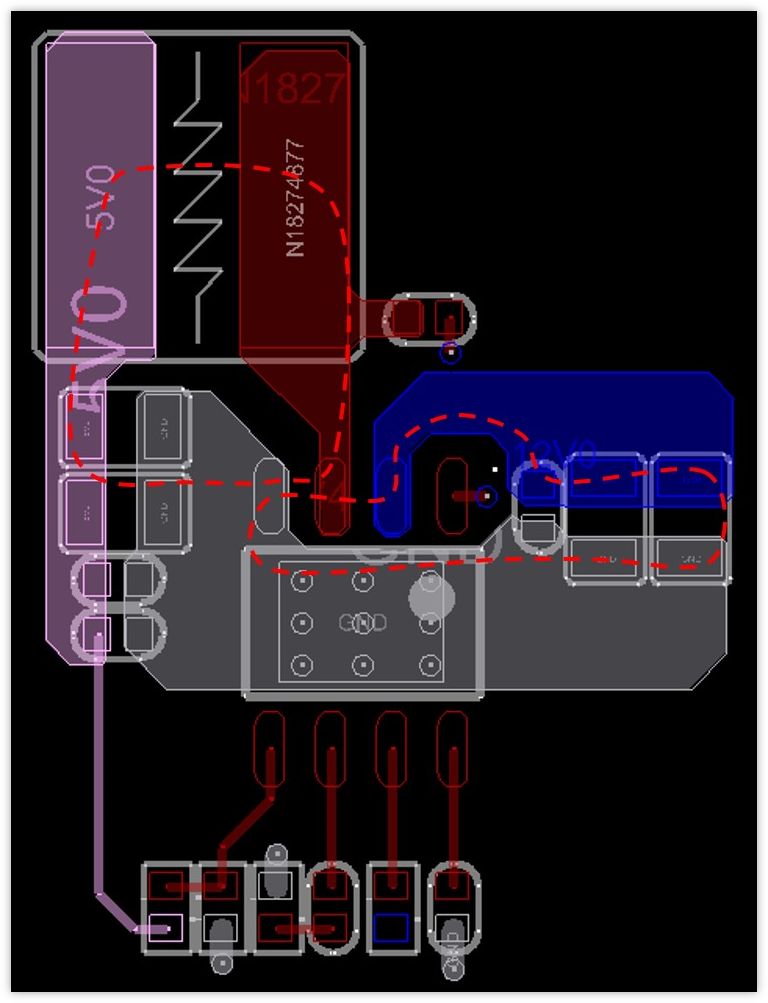

一个引脚分布不佳的Buck电路实例

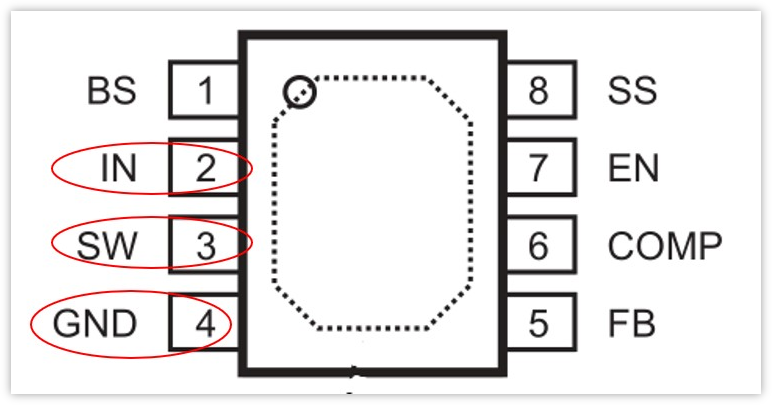

例如下面这个Buck芯片,它的引脚分布就很不友好。

SW引脚位于IN和GND引脚之间。如果严格按照“输入电容靠近IN和GND”的原则放置输入滤波电容,那么SW引脚的走线就会被阻挡。而电感也需要靠近芯片放置,这就产生了矛盾。

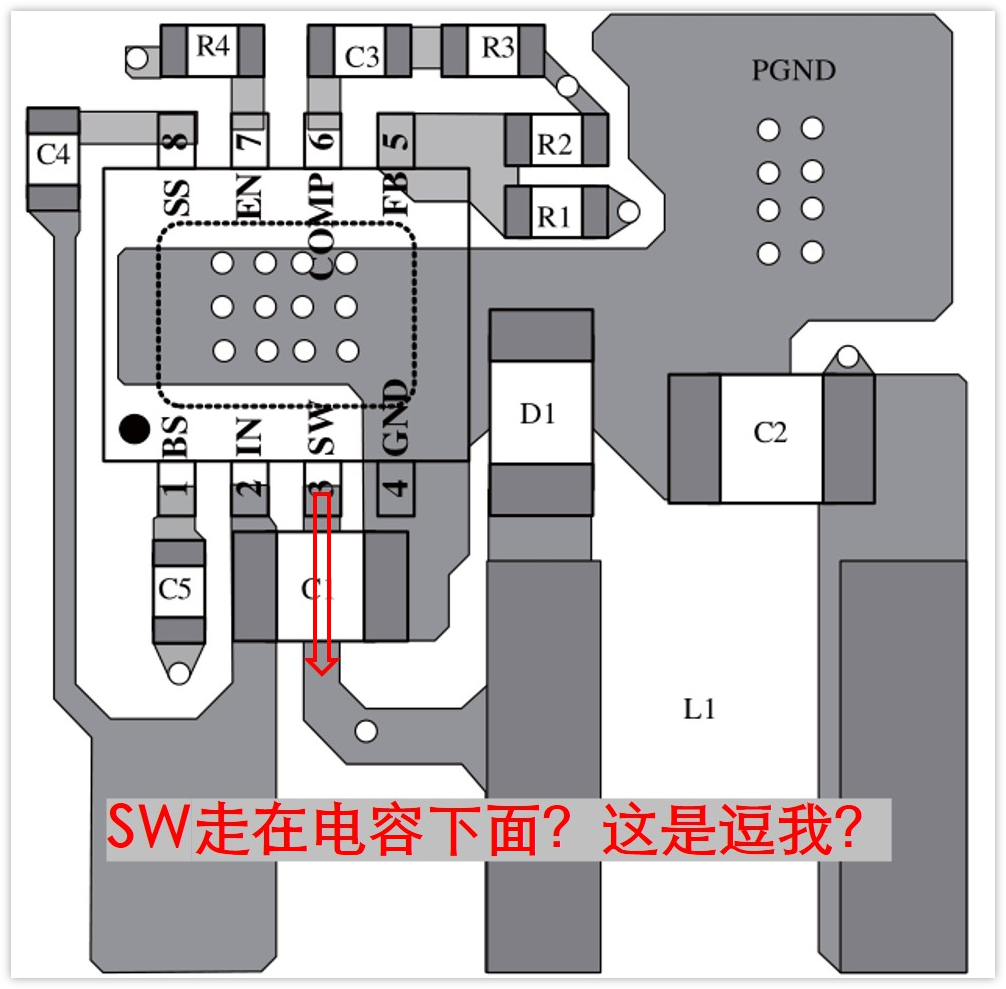

我们来看看该芯片手册推荐的Layout方案。

手册推荐的布局确实做到了“就近放置”,但它的方法竟然是让SW信号线从输入滤波电容底下穿过,这在实际工程中通常难以实现!

我们不能完全照搬手册的这种推荐方式,但现实是,采用类似引脚分布的芯片非常多。那么,我们的Layout究竟该如何布局布线呢?

先不急着回答这个问题,我想跟大家分享一个最根本的布局设计心法:

DCDC布局的终极奥义——心中有“环”。

心中有“环”

这里的 “环”,特指有大电流流过的闭合回路。只要我们能有效控制这些回路的面积和路径,Layout就成功了一大半。

下面我们来剖析其原因。

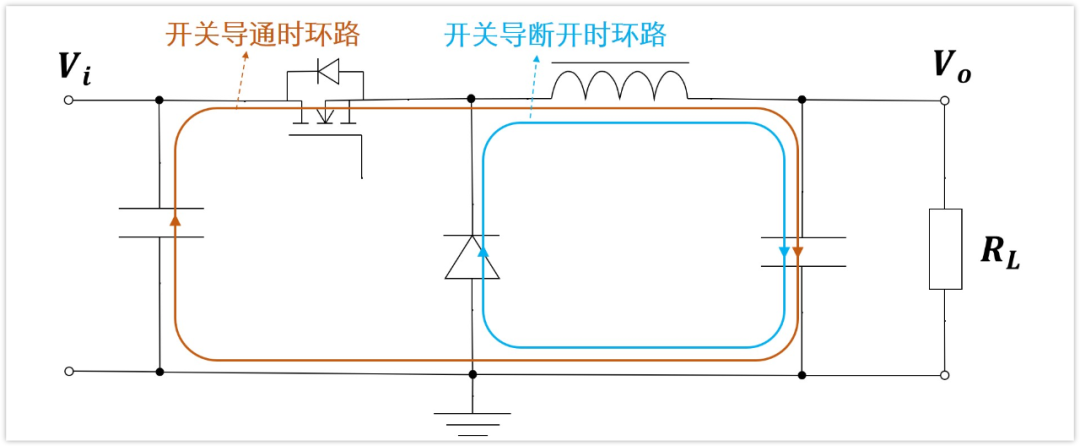

以Buck电路为例,其工作存在两种状态:上管导通和下管(或续流二极管)导通,因此对应着两个主要的电流环路。

搞清楚这两个环路有什么用呢?

核心目标是要让这两个环路的面积尽可能小。因为每一个电流环路都可以等效为一个环形天线,会产生电磁辐射,引发EMI问题,并可能干扰板上其他电路。辐射强度与环路面积成正比。

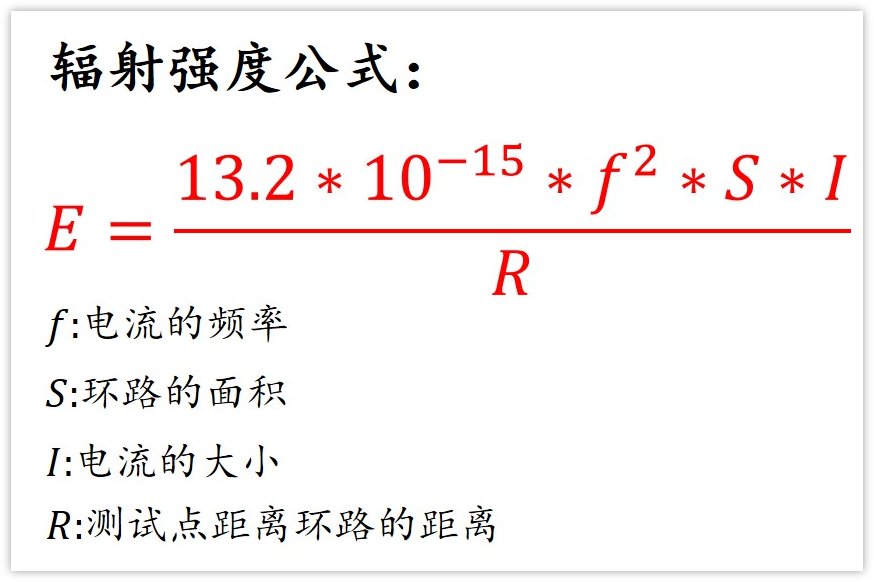

电流环路产生的高频磁场在传播一段距离后会转换为电磁场,其辐射场强近似为:

从公式可以看出,辐射强度与环路面积(S)、电流频率的平方(f²)以及电流大小(I)均成正比。

那么,是不是只要把这两个环路的面积做到最小就可以了呢?

理论上是的,但仅仅理解到这一步还不够深入,无法突出设计重点。

从拓扑图可见,Buck的两个大环路有重叠部分,其中一个包含另一个,导致大环路中各节点的电流并不一致,因此直接套用上述公式计算整个大环路的辐射并不方便。

我们需要变通一下。电磁辐射产生的根本原因,是变化的电流产生了变化的磁场。环路所围面积内的磁通量随电流动态变化,变化的磁场产生电场,进而形成电磁波传播出去。

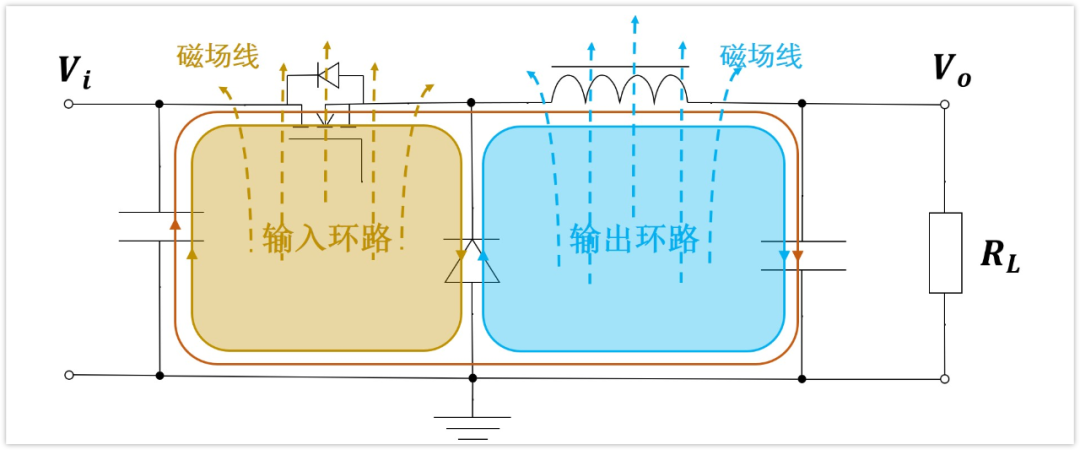

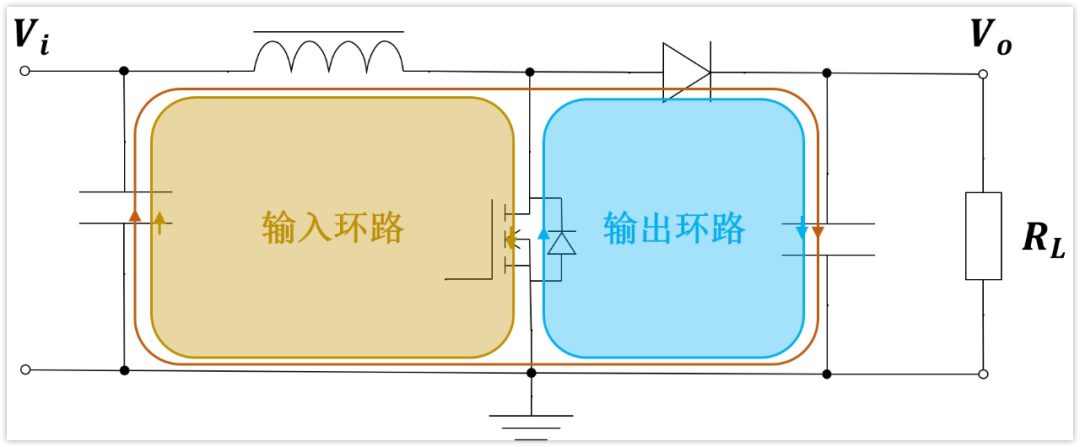

我们可以将那个复杂的大电流环路拆解为两个部分来分析,如下图所示:

整个大环路可以看作是 “输入环路” 和 “输出环路” 的叠加。

这可能需要一点理解:输入环路并非一个物理上独立存在的电流回路,它是两个实际电流环路的“差模”成分。这只是一种等效分析方法,目的是为了评估整个大回路中磁通量的变化情况。等效后,我们可以分别考察输入环路和输出环路的磁通变化。

- 输入环路的等效电流就是输入电容Cin的电流。

- 输出环路的等效电流就是电感的电流。

我们只关注其中的交流分量,直流分量频率为0,不会产生辐射。

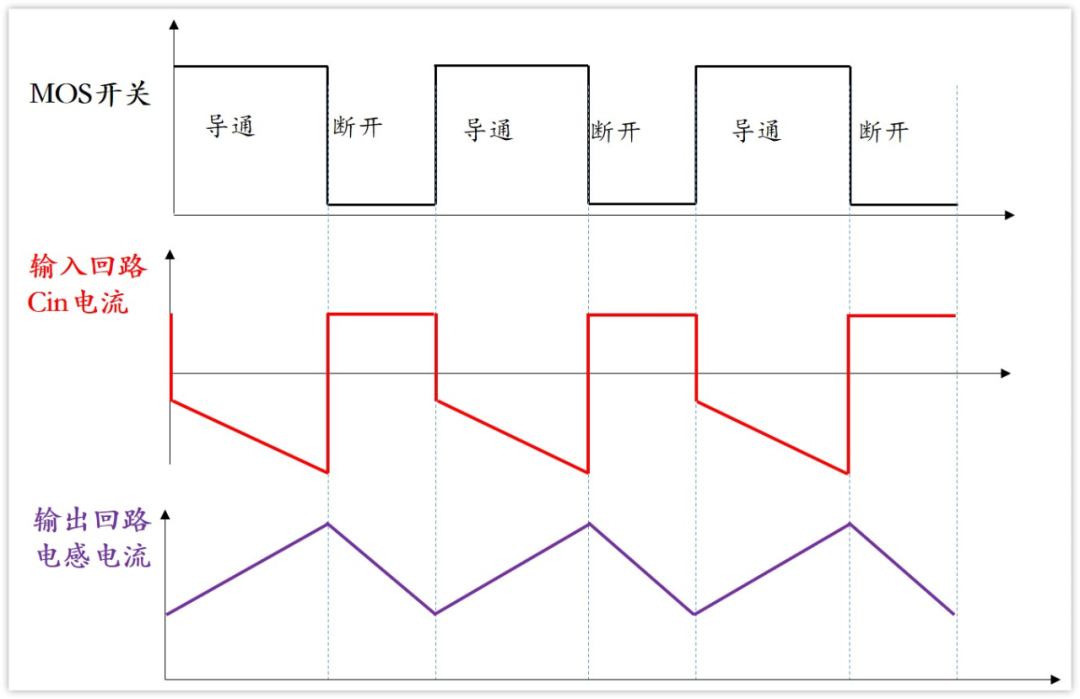

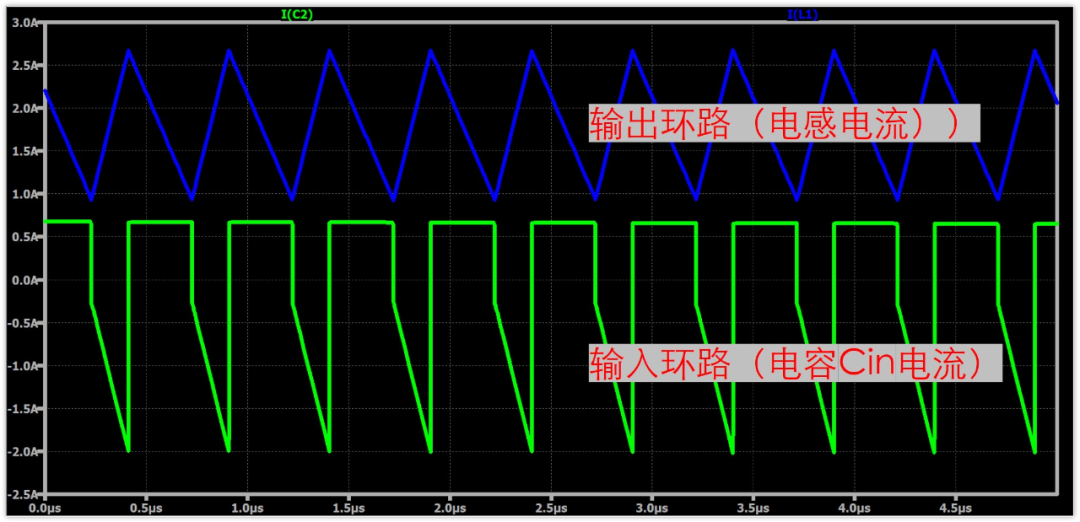

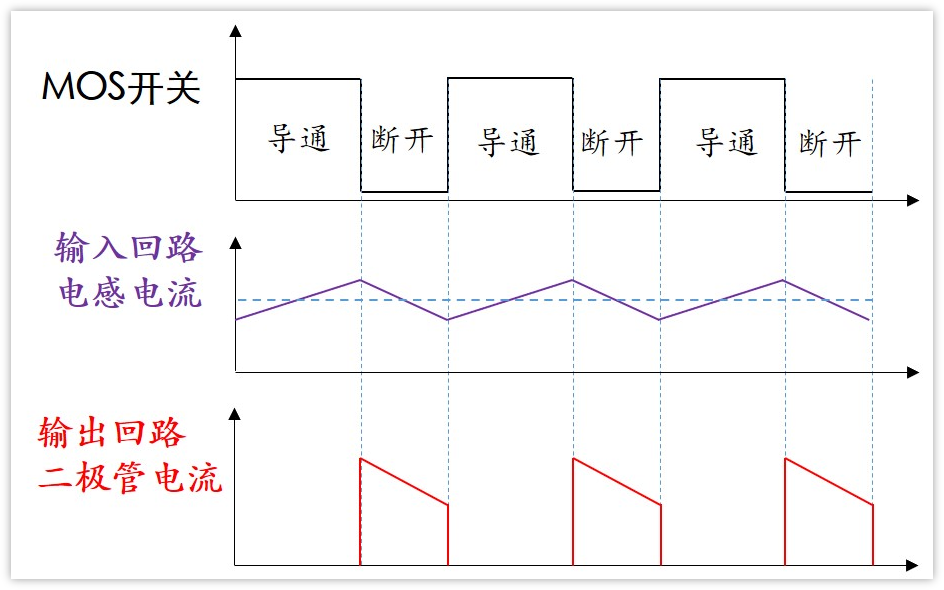

在之前的《手撕Buck!Buck公式推导过程》文章中已经分析过,输入环路电流(Cin电流)和输出环路电流(电感电流)的波形分别如下:

可以明显看到,在开关切换的瞬间,输入环路电流会发生突变,即存在很高的di/dt。这意味着输入环路的磁通量变化率极大,包含了丰富的高次谐波。

根据前面的辐射公式,辐射强度与频率成正比,因此这些高次谐波更容易被辐射出去。

相比之下,输出环路电流是连续的三角波,没有突变,其高次谐波的能量要小得多。

信号强度对比

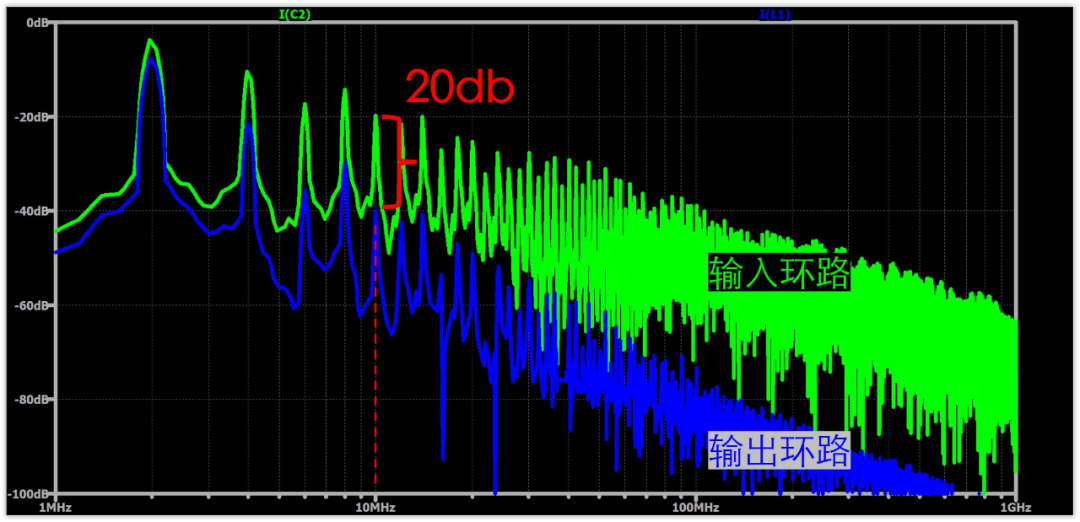

这里可能有人会质疑:三角波经过傅里叶变换后的频谱理论也是无限的,同样包含高频分量,为什么辐射就小呢?

确实如此。但三角波的高频分量幅度衰减很快,频率越高,其幅度越低,意味着高频分量的能量很微弱,因此产生的辐射也较弱。

关于这一点,我们可以通过仿真,观察电流的傅里叶变换(FFT) 频谱来验证。

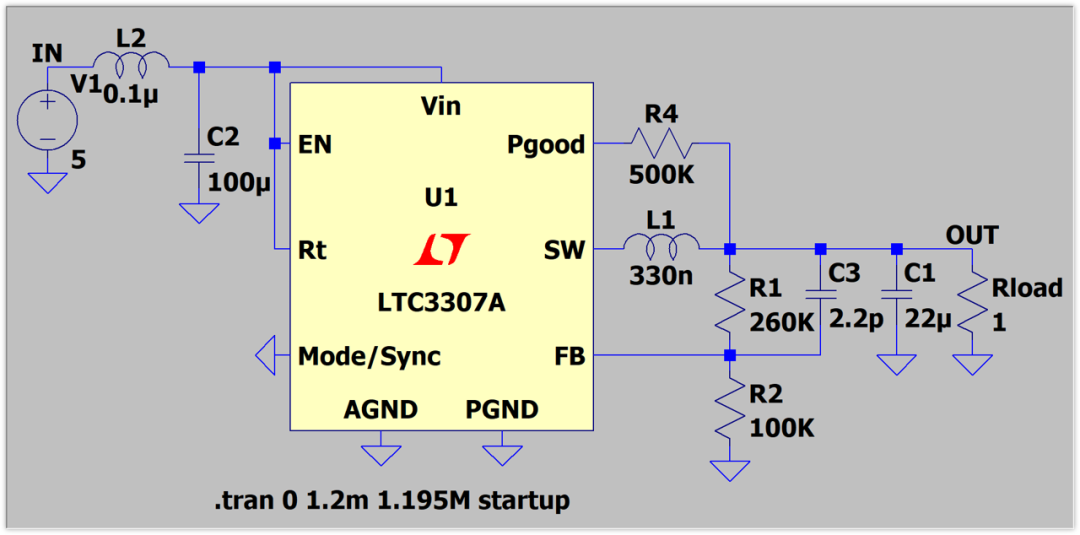

使用LTspice软件进行仿真,一个5V转1.8V的Buck电路图如下:

输入环路电流(输入电容电流)和输出环路电流(电感电流)的波形如下:

获得波形后,我们查看其FFT频谱:

可以看出,基频就是Buck芯片LTC3307A的开关频率2MHz。在2MHz处,两者的强度相差不大,仅2-3个dB。但在10MHz时,强度差已经达到20dB,且频率越高,差距越大。

这说明,输入环路的高频谐波能量远大于输出环路。有经验的工程师会知道,导致EMI测试超标的多半是高频段。因此,由输入环路引发EMI问题的概率要高得多。

我花了这么多篇幅分析,核心就是为了强调一个结论:

Buck电路的输入环路至关重要,必须将其环路面积做到最小。

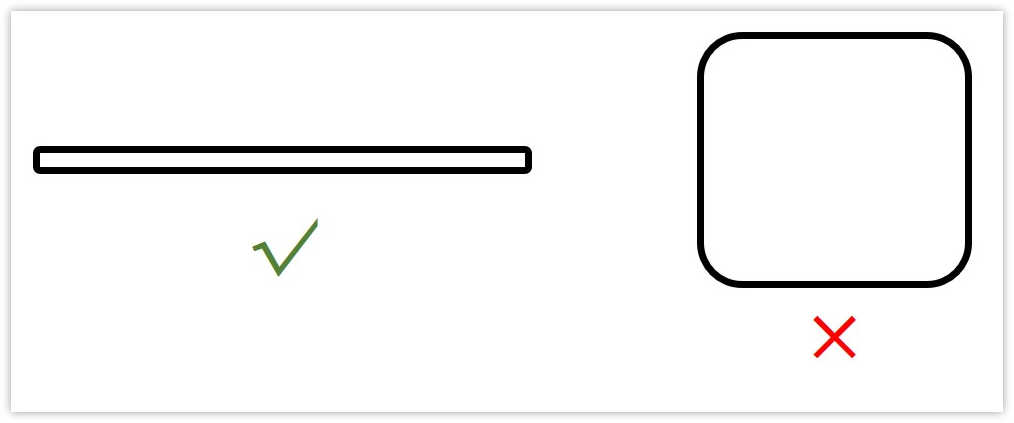

另一点需要注意的是,我们要最小化的是环路面积,而不仅仅是走线长度。 两者有所区别,有时走线短并不代表环路面积小。我们的终极目标是减小环路所包围的面积。

在布局走线时,应尽量将环路走成扁平的形状。

回到开头的DCDC芯片布局难题

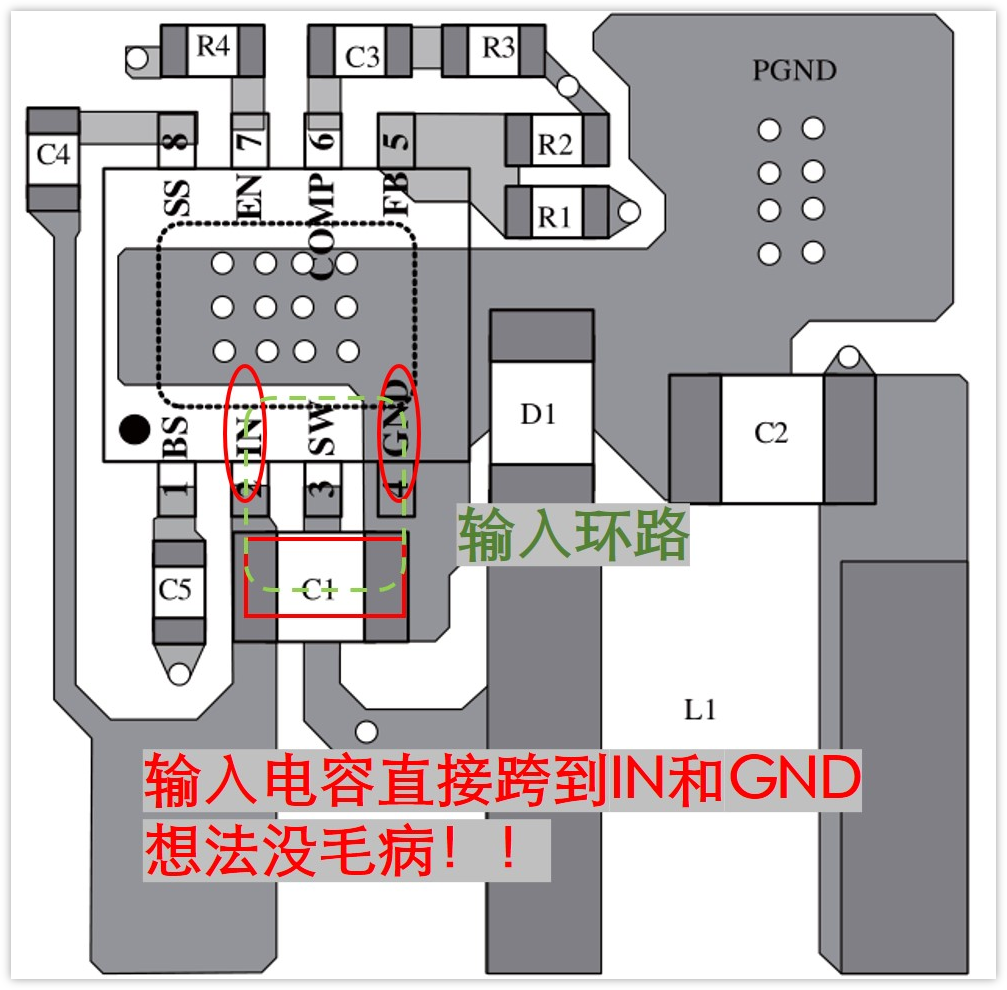

现在回到文章开头那个引脚分布不佳的Buck芯片。它的输入环路指的是什么呢?

显然,该芯片的开关管集成在内部,因此输入环路就是由芯片的IN引脚、GND引脚以及输入滤波电容构成的环路。除了芯片本身,这个环路中唯一的器件就是输入滤波电容。

所以,最理想的布局就是直接将输入滤波电容跨接在芯片的IN脚和GND脚之间。从这一点看,芯片手册的推荐布局思路是符合的,只不过它为了实现这一点,让SW信号线从电容下方穿过,这在实际中很难操作。

这颗DCDC芯片的推荐布局确实保证了输入环路最小化,但将SW走在电容下面的做法通常不现实,因为电容下方很难布置足够宽的铜皮来承载开关电流。

那该怎么办呢?

或许有人会想到将输入滤波电容放置在PCB背面,在Vin和GND管脚的正下方打孔连接,这样看起来环路面积也较小。

我的看法是:如果有其他更好的布局方式,应尽量避免这样做。

因为过孔会引入寄生电感,增加环路的总体电感量,可能引发LC谐振。直观表现就是在SW节点产生很高的振铃电压。高振铃意味着环路中谐振频率的信号分量非常强。

也就是说,虽然环路面积小了(天线效应减弱),但信号强度增大了,最终的辐射效果未必会变好。

关于振铃,以前专门写过《BUCK的振铃实验与分析》,可以参考。

一个实际教训

多年前,我曾遇到一个案例:将电源芯片的输入滤波电容放在背面并通过过孔连接,结果导致整板噪声很大。而将滤波电容手动用导线跨接到芯片的Vin和GND引脚上后,问题立即消失。

当时很不解,觉得过孔数量不少,电容也在底部就近放置,怎么还会有问题?几个过孔的威力这么大吗?

后来专门改版解决,将输入滤波电容与芯片放在同一层,并在表层直接连接,问题便迎刃而解。

综上所述,Buck电路布局的重中之重是输入滤波电容的布局布线,这是第一优先考虑项。

如果是异步Buck电路,还会有一个外置的续流二极管,它也是输入环路的一部分。其布局的重要性与输入滤波电容同级,需要靠近芯片的SW引脚放置。具体如何摆放,核心准则依然是如何使整个输入环路的面积最小。

输出环路的重要性

前面花了大量篇幅强调输入环路,那输出环路就不重要了吗?

当然不是。 从前面的FFT频谱也能看出,输出环路同样包含高频分量,因此输出环路也应尽可能小。只是在输入与输出环路布局发生冲突时,应优先保证输入环路。

我的布局方案

总而言之,如果让我来对文章开头提到的那个Buck芯片进行布局,我会这样处理:

Boost电路的情况分析

以上讨论的是Buck电路,那么Boost电路的情况又如何呢?

对Boost电路而言,最重要的也是输入回路吗?需要优先考虑输入滤波电容吗?

答案是否定的。

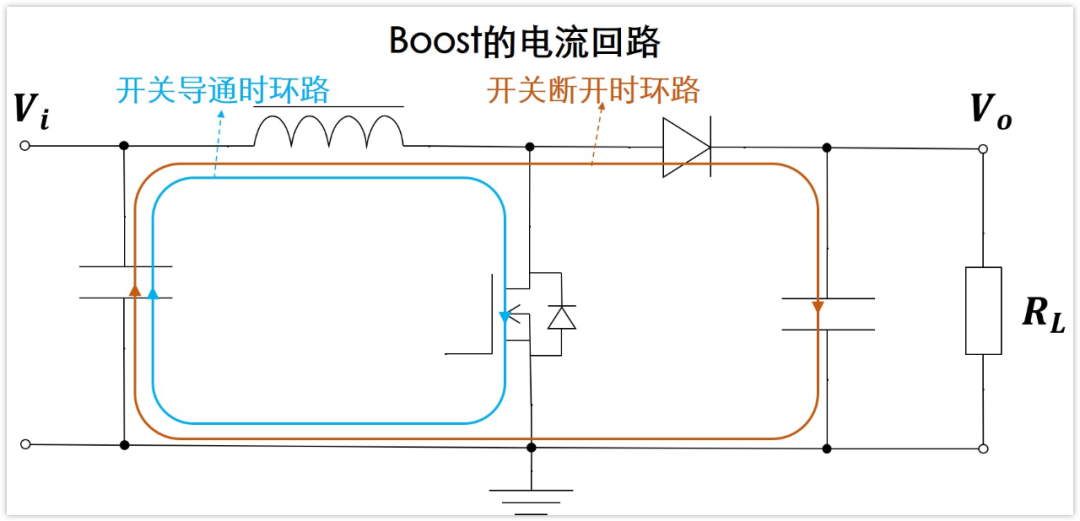

Boost电路也有两个工作环路,如下图所示:

与Buck类似,我们也可以将其分解为输入环路和输出环路。可以看到,输出环路是两个实际环路的“差模”成分。

与Buck不同之处在于:Boost的电感位于输入环路,其电流是连续的三角波;而输出环路的电流就是续流二极管的电流,是存在突变的。

在之前的《手撕Boost!Boost公式推导及实验验证》文章中已经分析了这两个电流,波形如下:

也就是说,对于Boost电路,最关键的是输出回路(其电流有突变),其地位类似于Buck电路中的输入回路。我们需要优先保障Boost输出环路的面积最小化。

其他布局注意事项

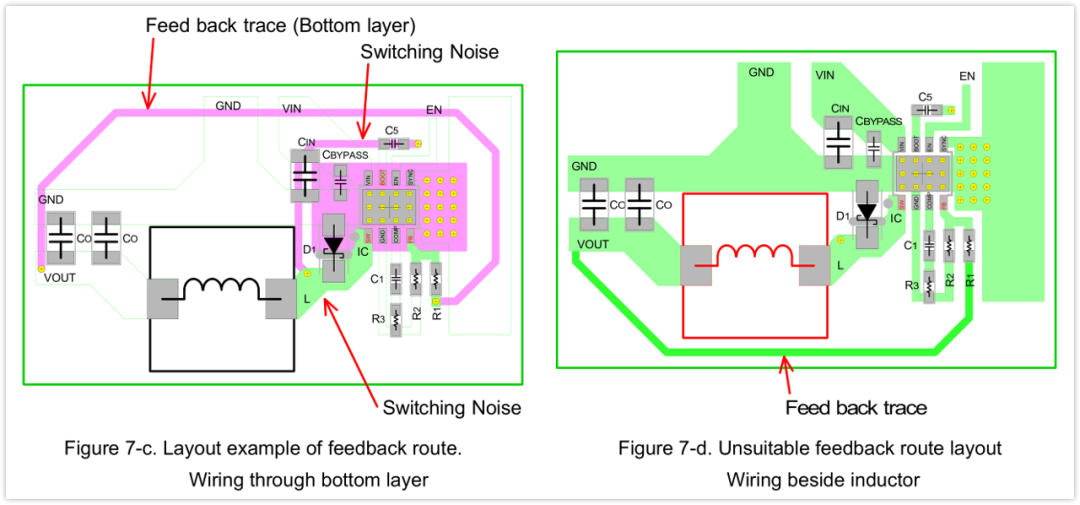

除了处理大的功率电流环路,对于FB(反馈)、补偿电路等小信号走线,需要尽量远离上述大电流环路和电感等噪声源。

例如下图中,左侧的布局就优于右侧:

另外需注意,在规划大电流回路时,必须将GND地路径作为环路的一部分来考虑,避免用走线分割了大电流的回流地路径。

所以,有时你会看到底层的FB走线并不是最短的直线,而是有意绕开了一些区域。

总结

总的来说,进行DCDC的PCB布局时,我们必须做到心中有“电流环”。

在画板时,要在心里模拟:开关断开时,电流怎么流;开关导通时,电流又怎么流。然后找出电流存在突变的那一个环路,它就是布局中需要优先处理的重中之重。

这个原则不仅适用于DCDC,对于其他类型的电源电路或大功率电路设计同样适用。

理解了“环路最小化”这一核心原则,很多电路的布局甚至无需细看芯片手册中冗长的注意事项,因为手册所述无非是这一原则的具体实施方法。

从源头(环路面积)上杜绝EMI问题的产生,远比后期出现问题再尝试各种补救措施要有效得多。

掌握硬件设计的底层原理,能让我们在复杂的工程挑战面前更加从容。如果你对这类深入的硬件知识解析感兴趣,欢迎在云栈社区与更多开发者交流探讨。

最后,文中所涉及的《硬件十万个为什么(无源器件篇)》一书,系统性地解答了电阻、电容、电感等无源器件的原理与选用规范,是硬件工程师夯实基础的优秀读物。