上期我们探讨了BUCK电路开关振铃的LC阻尼振荡本质,文章偏重理论。那么,同步BUCK电路的开关尖峰振荡到底是如何产生的呢?

要把这个问题彻底搞清楚并不容易,因此本文会涉及大量的仿真实验与分析,内容比较详实。

本文的核心是分析以下两个关键问题:

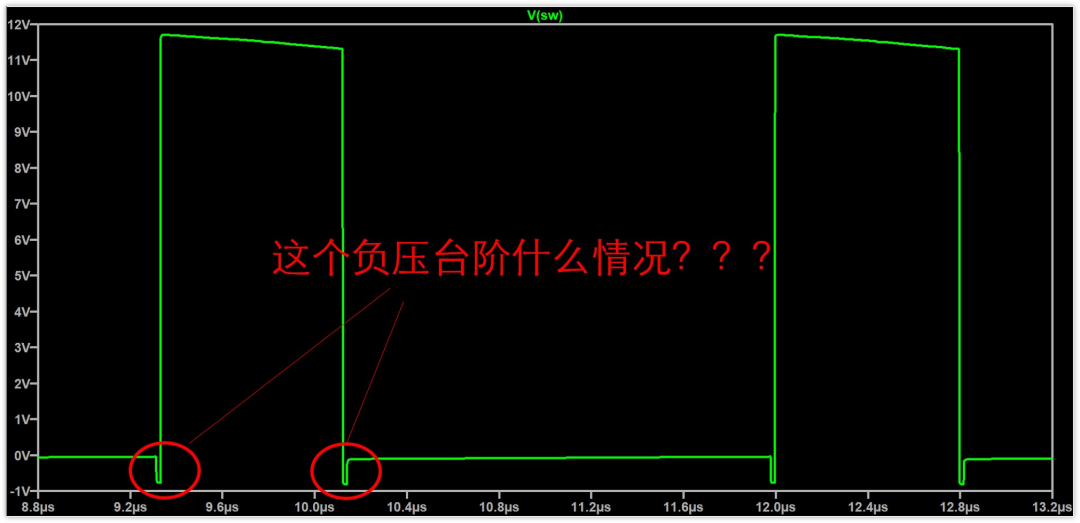

1、什么是死区时间?开关波形底部那个小台阶是怎么回事?

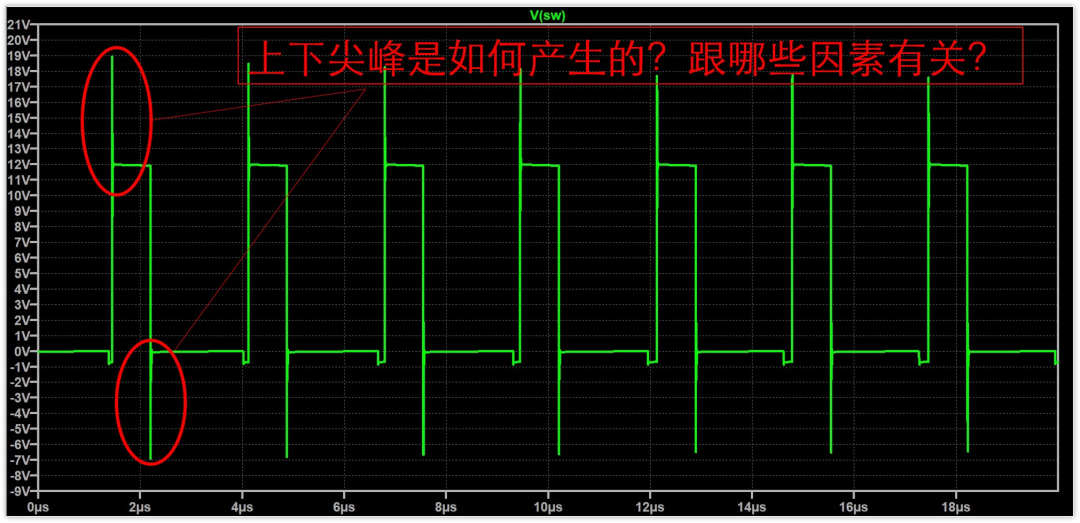

2、开关波形上的上下尖峰振荡是如何产生的?与哪些因素有关?

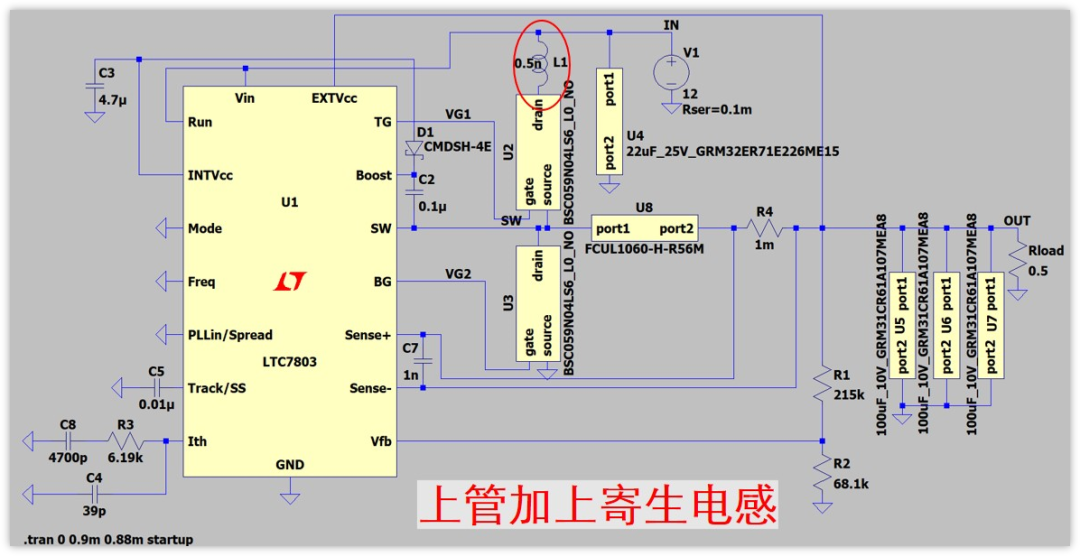

理想的BUCK电路SW波形

我们由浅入深,先来看看没有尖峰电压的“理想”开关波形是什么样的。

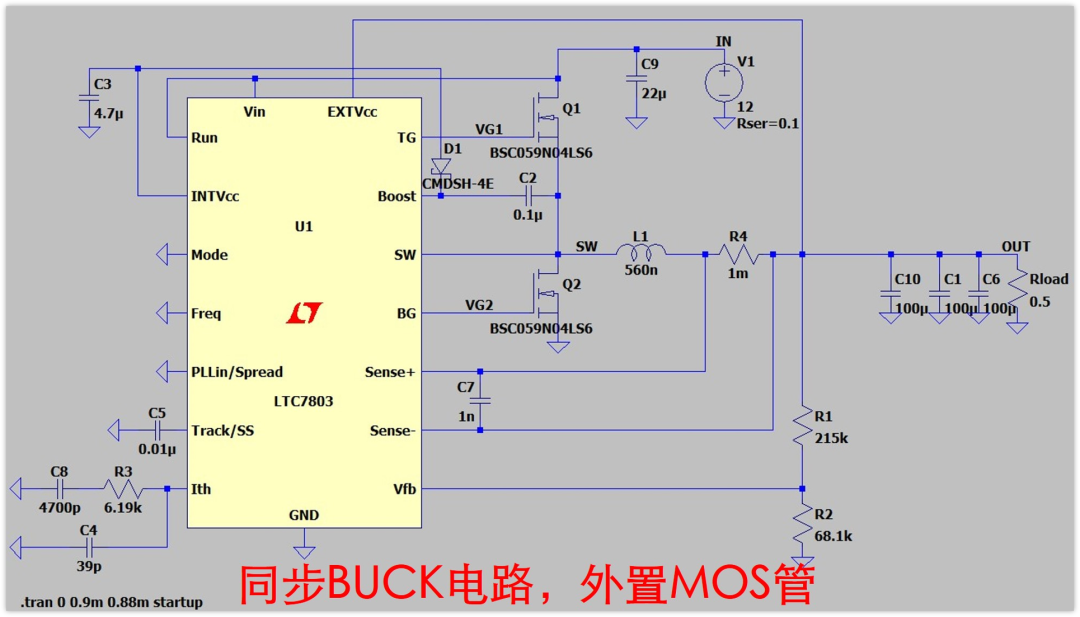

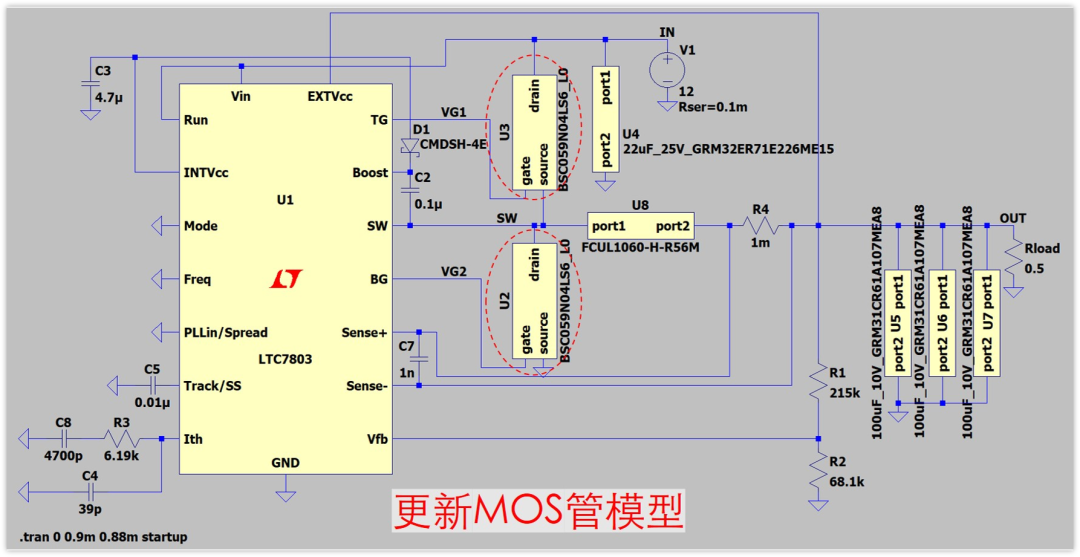

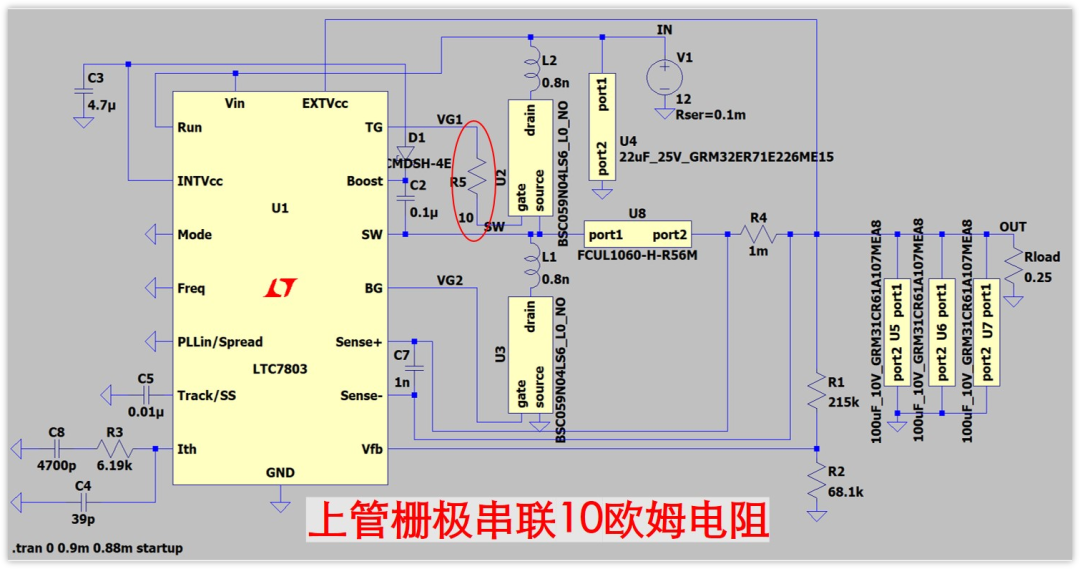

为了更好地观察BUCK电路各节点的电压电流情况,我选择了一款外置MOS管的电源芯片 LTC7803 进行仿真。

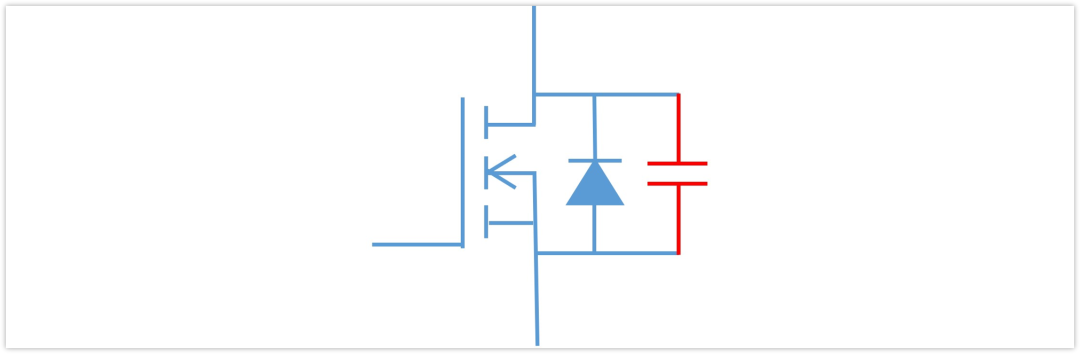

使用 LTspice 搭建的电路图如下,这是一个典型的同步BUCK拓扑,没有使用外部分立二极管。

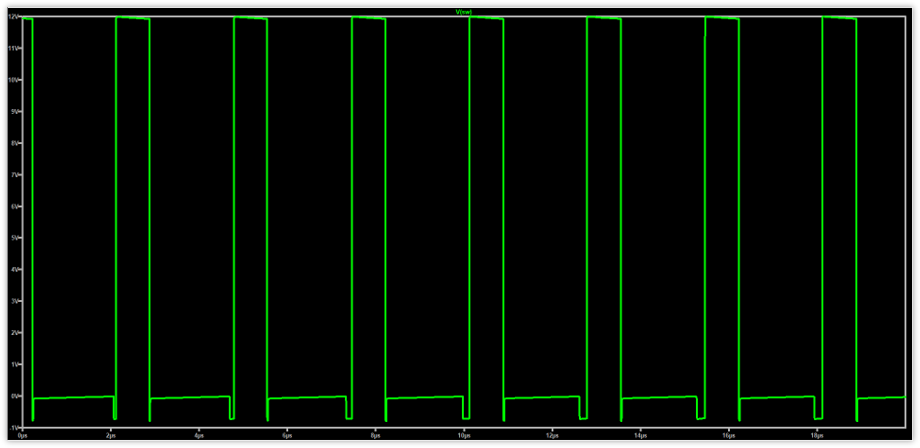

电路参数:输入12V,输出3.3V,负载0.5Ω,BUCK工作在连续模式。我们直接观察电感前端的SW节点波形:

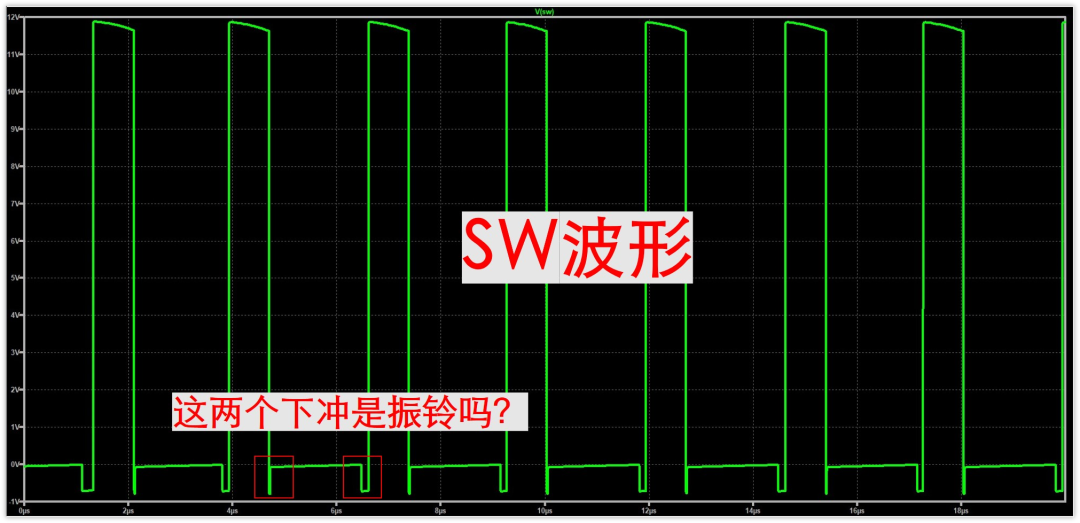

这个波形看起来非常“干净”,没有向上的振铃尖峰。唯一的美中不足是波形底部有一个约0.7V的下冲。

这个下冲是怎么回事?是向下的振铃吗?

仔细观察,这个下冲幅度固定,且没有振荡,因此猜测它可能是二极管的导通压降。为了验证,我们同时观察上下管(MOS管)的栅源电压Vgs以及电感电流。

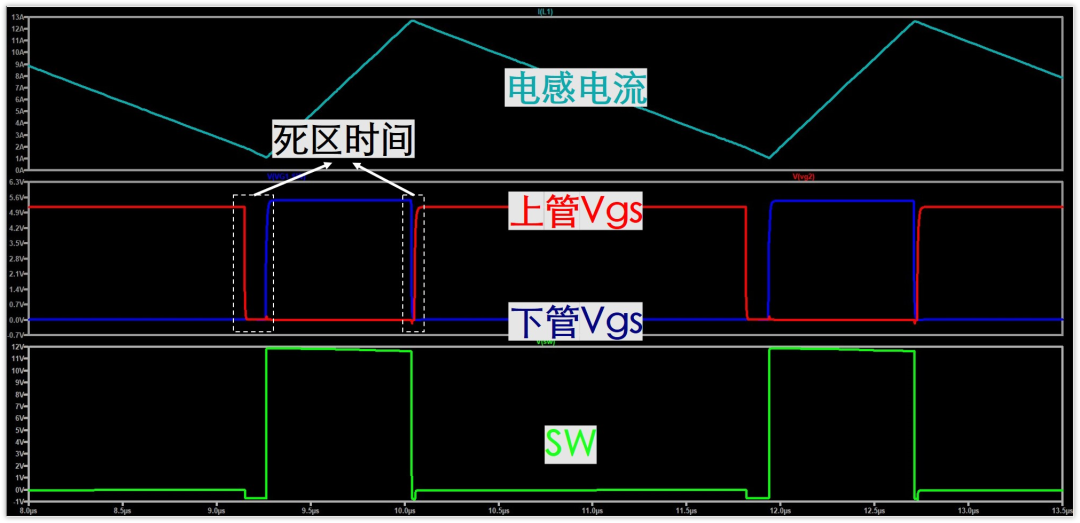

从上图可以清晰看到:

- 电感电流始终为正(大于0),方向流向负载,最小值约2A。

- 上下两个NMOS管的Vgs信号存在同时为低电平的时段,即两个管子都关闭,这段时间就是死区时间。

为什么需要死区时间?

在理想化分析BUCK拓扑时,我们通常认为上下管交替导通。但实际上,MOS管在开关切换过程中存在中间态(半导通状态),此时导通电阻很大。如果上下管同步切换,极有可能出现两者都处于半导通状态,导致续流路径阻抗过高,电感电流无法续流。

更严重的是,如果切换稍微不同步,可能导致上下管同时完全导通,造成输入电源到地的直通短路,这是灾难性的。

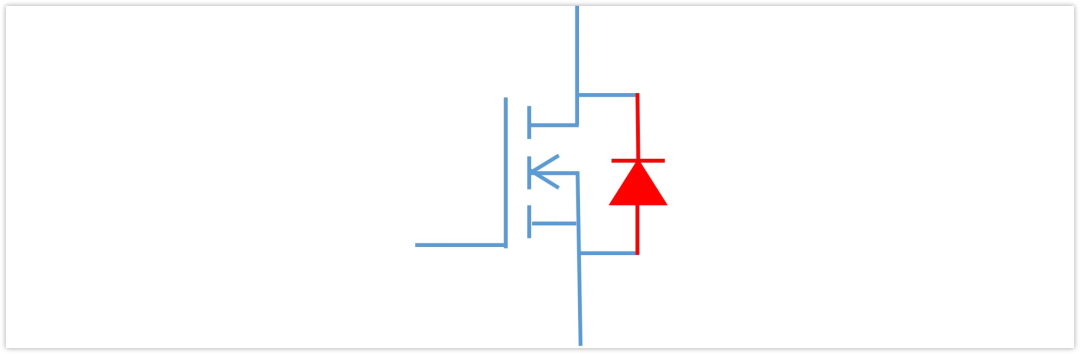

因此,最保险的做法是将驱动信号错开,设置一段两个管子都关闭的“死区时间”,彻底避免直通风险。那么,死区期间电感电流如何续流呢?答案是利用MOS管内部集成的体二极管。

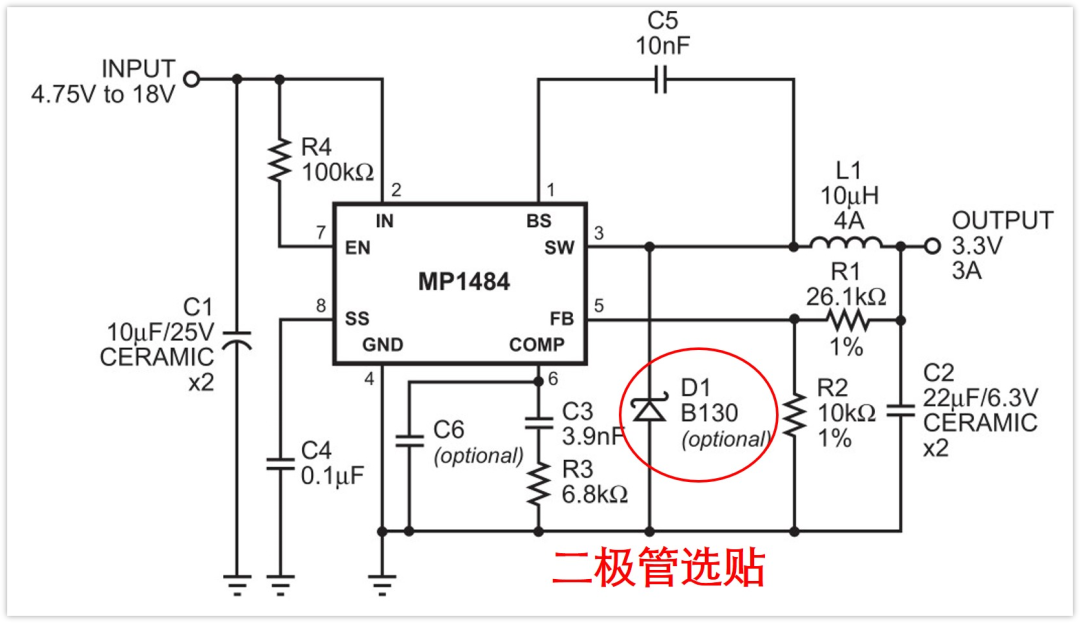

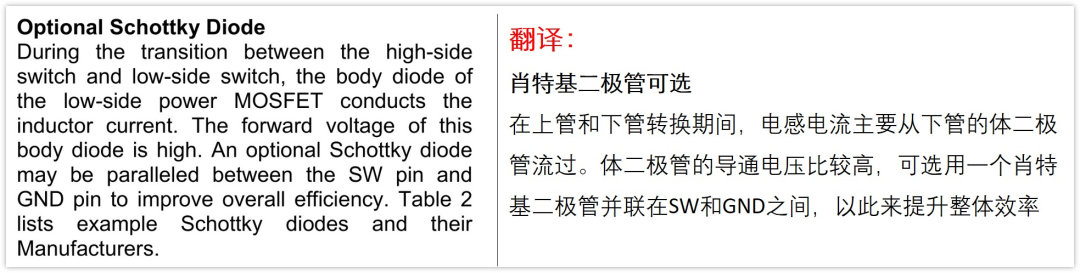

这引出了一个常见设计:有些同步BUCK芯片的推荐电路中,会有一个“可选(选贴)”的肖特基二极管。例如MP1484的D1。

这个可选二极管有什么用?

芯片手册里写得很清楚(见下图翻译):在死区时间,电感电流流经下管体二极管。体二极管(硅材质)导通压降较高,并联一个导通压降更低的肖特基二极管可以提升整体转换效率。当然,由于死区时间占空比极小,效率提升非常有限。

那么,实际电路在开关切换时也会有这个0.7V的“下冲”吗?

我用手头的MP1484板卡进行了实测,波形如下:

奇怪的是,实测波形只在下降沿出现了一个0.7V的下冲台阶,而上升沿底部却没有。难道上升沿没有死区时间?

我猜测这可能与负载电流较小、上升沿死区时间极短,以及MOS管DS极间寄生电容有关。在切换前,下管导通,寄生电容电压为0。死区时间开始时,体二极管并非立即导通,需要先将寄生电容放电至约-0.7V。如果死区时间太短或电感电流很小,电容放电不足以使电压降到体二极管开启门限,死区特征就不明显。

为了验证,我增大了负载电流,迫使寄生电容无法提供足够的续流。再次测试,波形如下:

此时,上升沿也出现了一个向下的“冒尖”,持续时间极短(约13ns),而下陷沿的下冲时间约100ns。这说明MP1484的两个死区时间并不对称,分别为13ns和100ns。

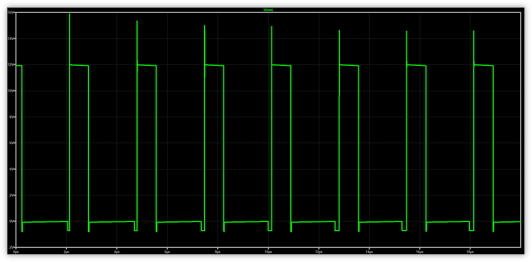

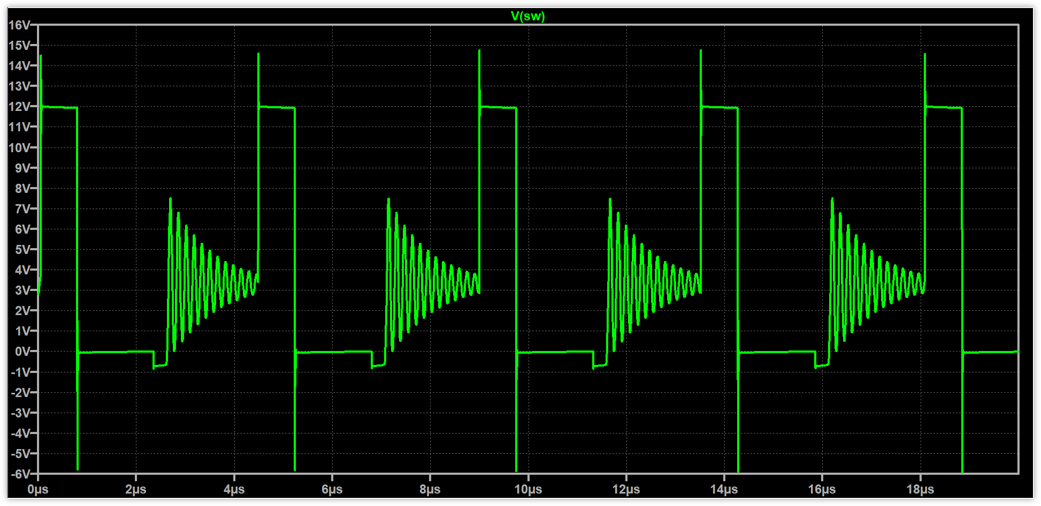

至此,我们弄清了死区时间导致的负压台阶。但前面的仿真波形完全没有尖峰,而实测波形有。这个关键的振荡尖峰是如何产生的?它的大小又受哪些因素影响?

下面进入正题。需要说明,我实测的尖峰较小是因为PCB布局已做优化。如果布局不当,尖峰可能非常显著,如下图这种高频振荡。

尖峰过高会带来严重的EMI问题,并可能危及开关管安全。要抑制尖峰,必须首先理解其产生机理。

BUCK电路SW尖峰的产生机理

第一个问题:为什么之前的仿真没有出现尖峰?是器件模型不够精确吗?

仿真用到了芯片、MOS管、电感和电容模型。我们需要逐一排查。

更新功率电感模型

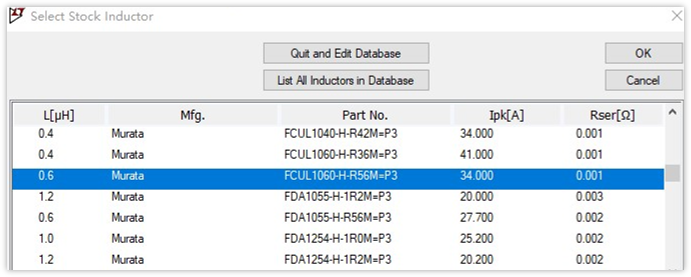

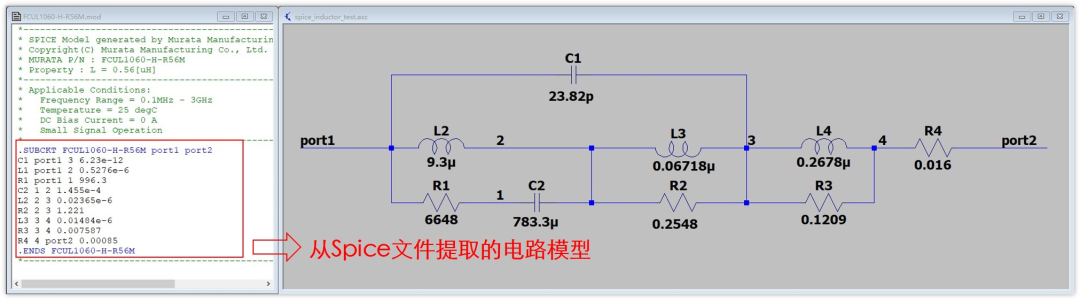

最初使用的功率电感 FCUL1060-H-R56M 是LTspice库中的简化模型,仅包含串联电阻Rser,缺乏寄生电容参数。

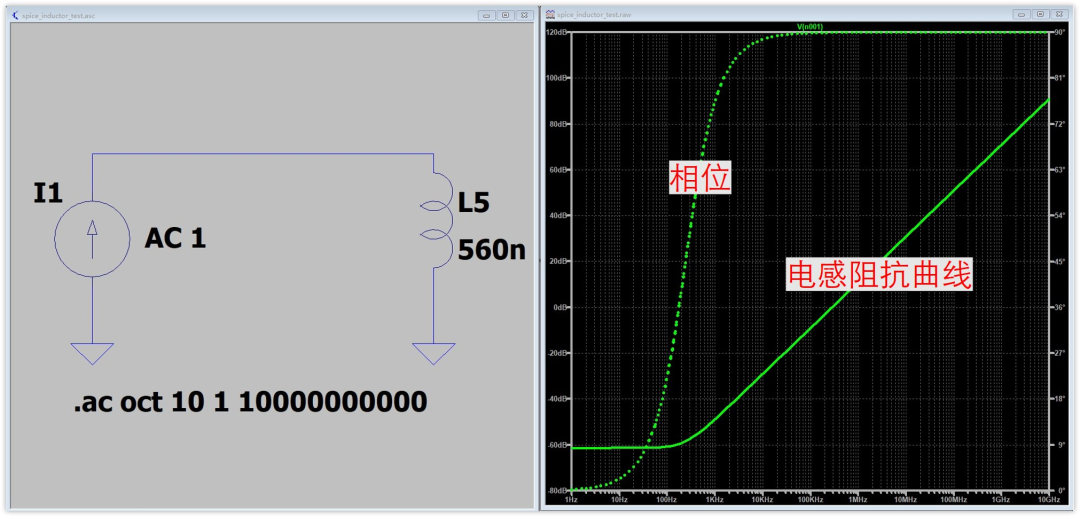

我怀疑其准确性。单独测试该模型的阻抗频率特性:使用1A交流电流源进行AC扫描,测量电感两端电压(阻抗等于电压值)。结果如下:

结果显然有问题:阻抗随频率单调上升,连基本的自谐振点都看不到,模型过于理想。

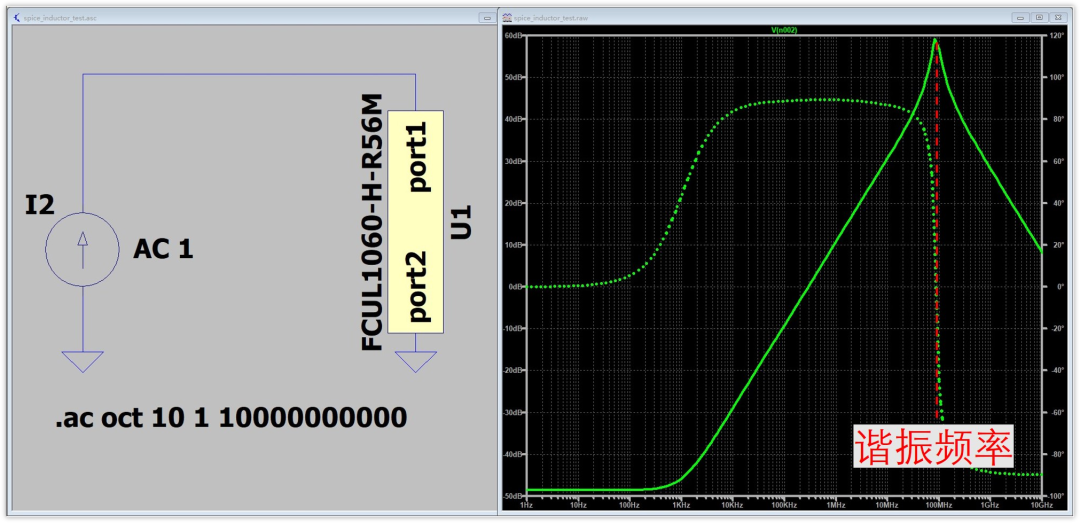

于是,我从村田官网下载了该电感精确的Spice模型文件。在LTspice中导入后,重新测试其阻抗曲线:

此时,阻抗曲线出现了正常的谐振峰,自谐振频率约在100MHz,这个模型准确得多。

Spice文件本质是描述元件等效电路的网表,根据其内容可以绘制出该电感的等效模型,如下图所示。其复杂度远高于我们常用的“电感串联电阻并联电容”的简单模型。

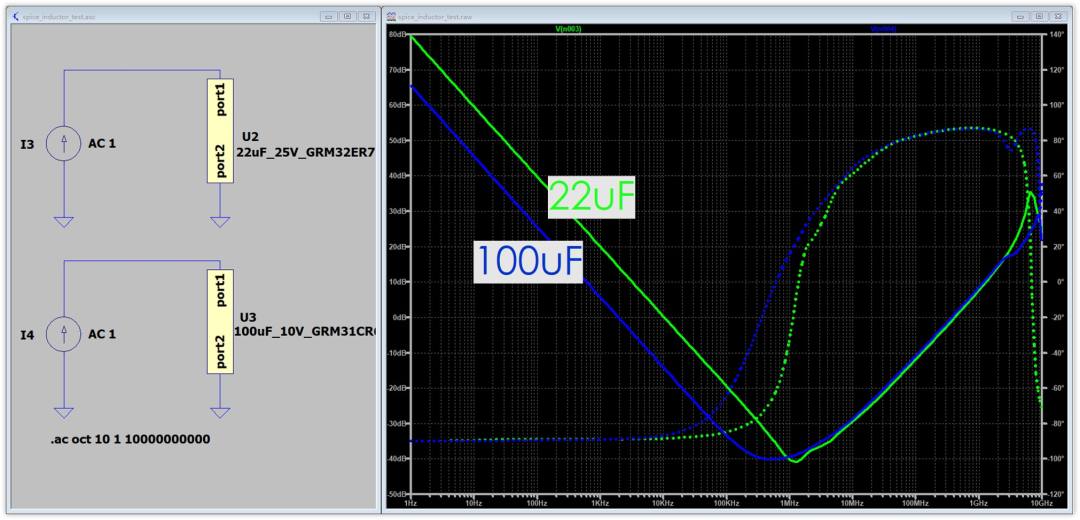

更新电容模型

采用同样方法,为电路中的22uF和100uF滤波电容也替换为官网下载的精确Spice模型。测试其阻抗曲线如下:

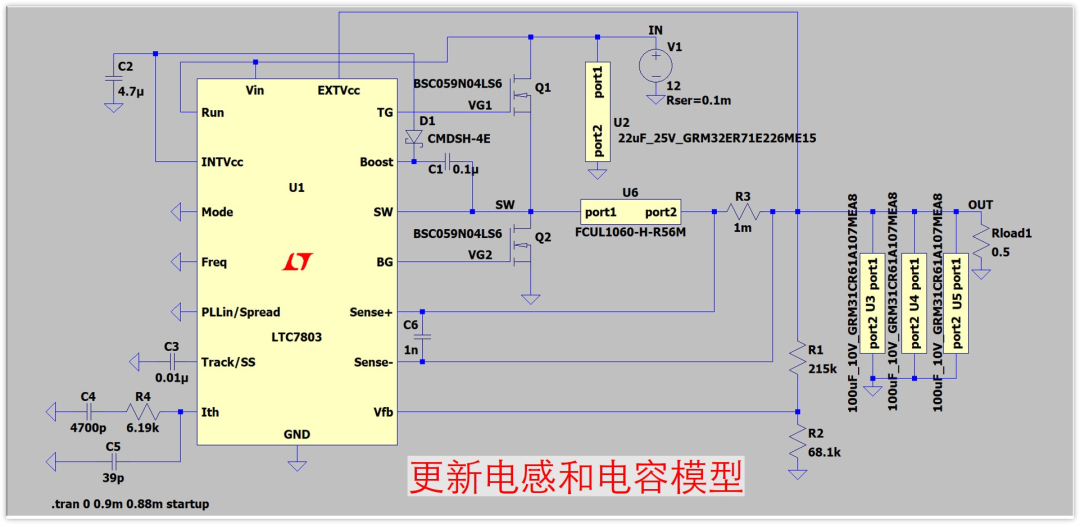

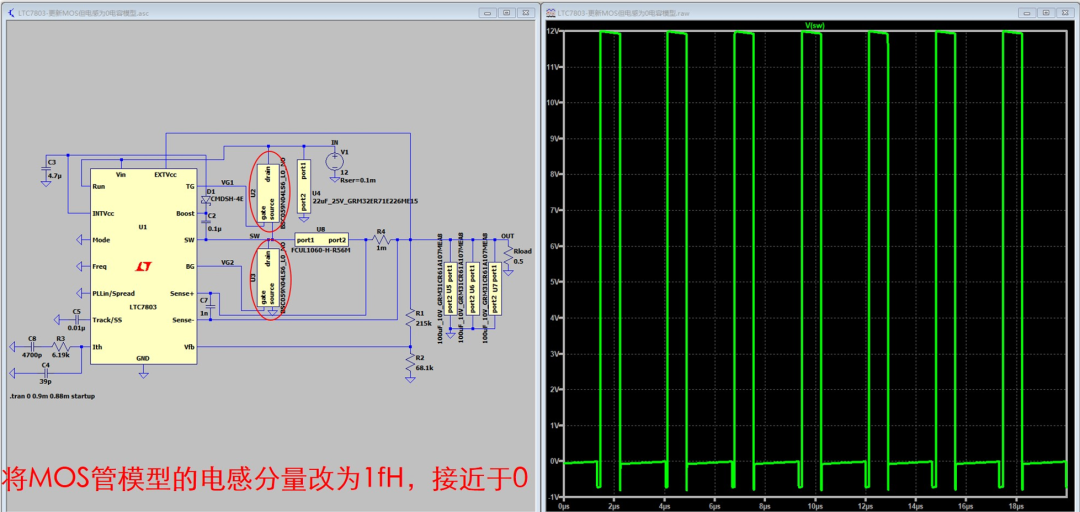

仿真验证

将更新后的电感、电容模型代入原电路。

再次仿真SW波形:

结果:与更新前相比,波形几乎没有变化,仍然没有尖峰。 问题看来不在无源器件上。LTC7803是驱动芯片,主要影响开关速度。那么,剩下的唯一变量就是MOS管模型了。

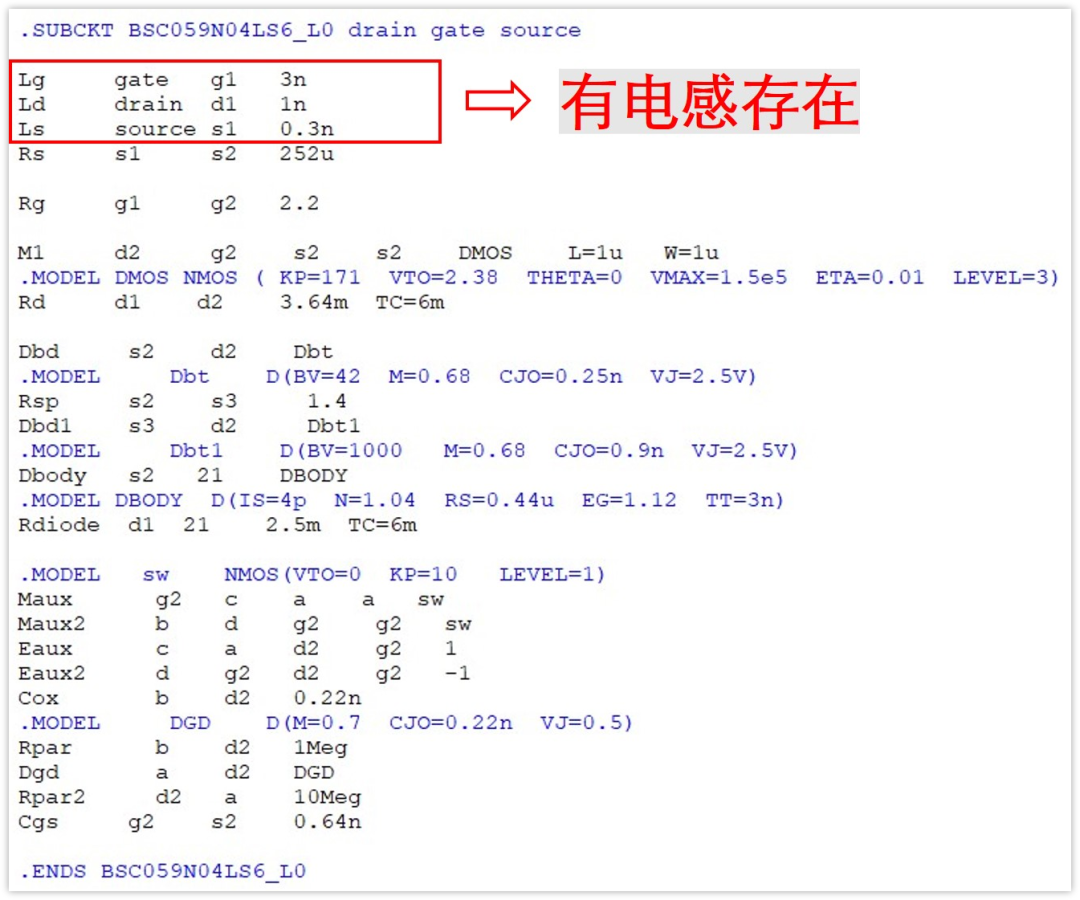

更新MOS管模型

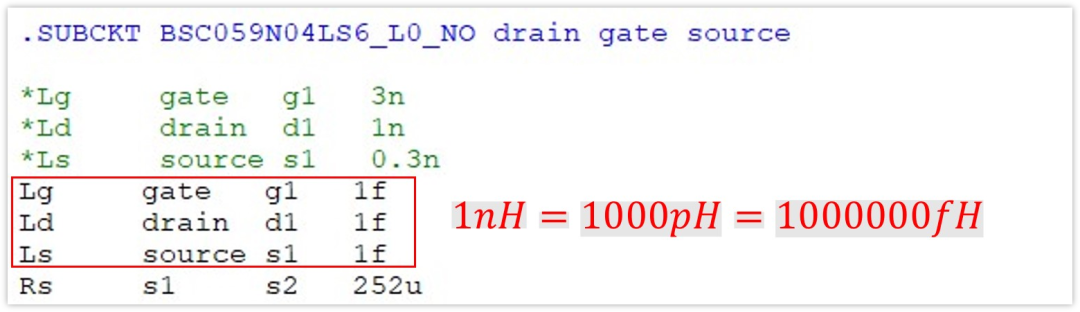

LTspice自带的MOS管模型很可能也是简化版。我从英飞凌官网下载了所用MOS管 BSC059N04LS6 的完整Spice模型,构建新模型并替换到电路中。

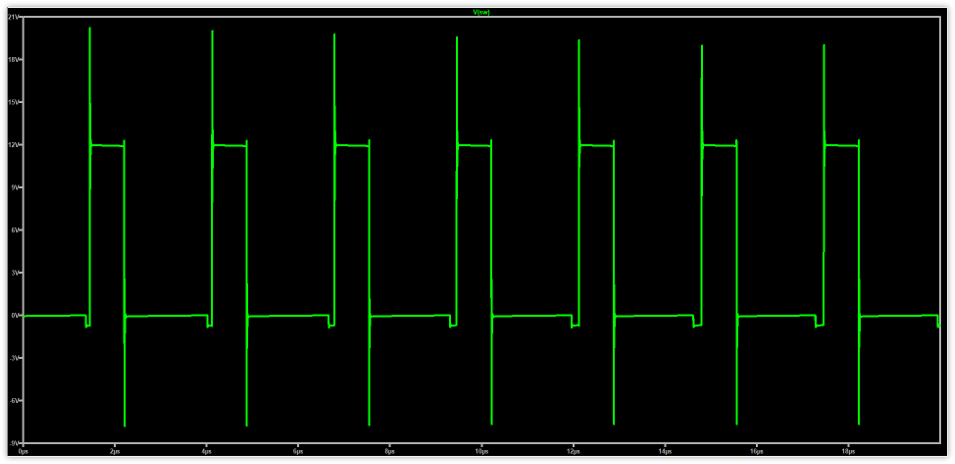

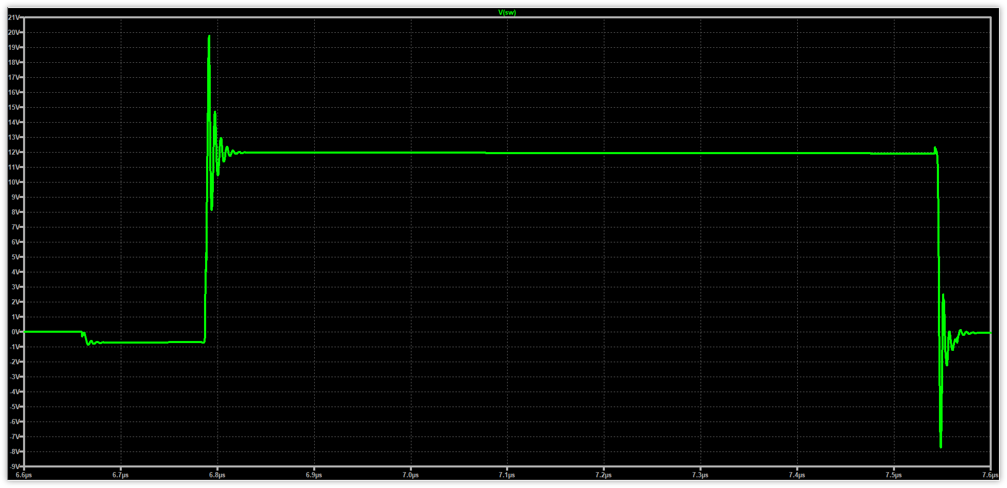

仿真SW波形:

久违的振荡尖峰终于出现了! 上下尖峰幅度均约8V。

关键发现:官网提供的MOS管模型有何不同?

查看其Spice文件,发现了三个关键参数:Lg, Ld, Ls。这三个参数代表了在MOS管的栅极(G)、漏极(D)、源极(S)引脚上串联的寄生电感。

我猜测,正是这三个寄生电感的引入,导致了振荡尖峰的产生。 因为振荡的本质是LC阻尼,MOS管模型本身已包含结电容,但电感通常是缺失的。

为了验证,我将模型中的Lg, Ld, Ls三个参数改为极小值1fH(1e-15 H,近乎为零)。

用这个“零电感”的新模型替换到电路中再次仿真。

结果:SW尖峰完全消失! 这确凿地证明了MOS管引脚上的寄生电感是产生开关尖峰的必要条件。

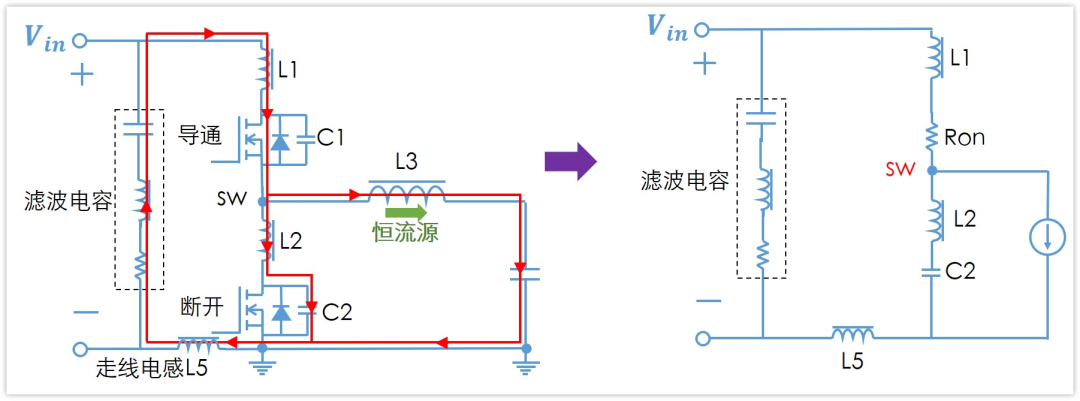

从电路拓扑分析尖峰产生过程

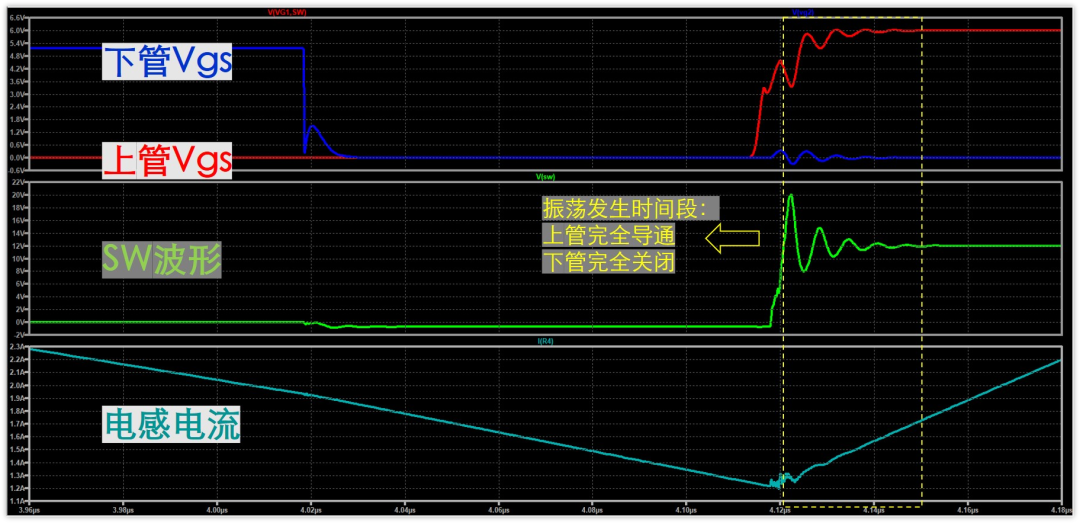

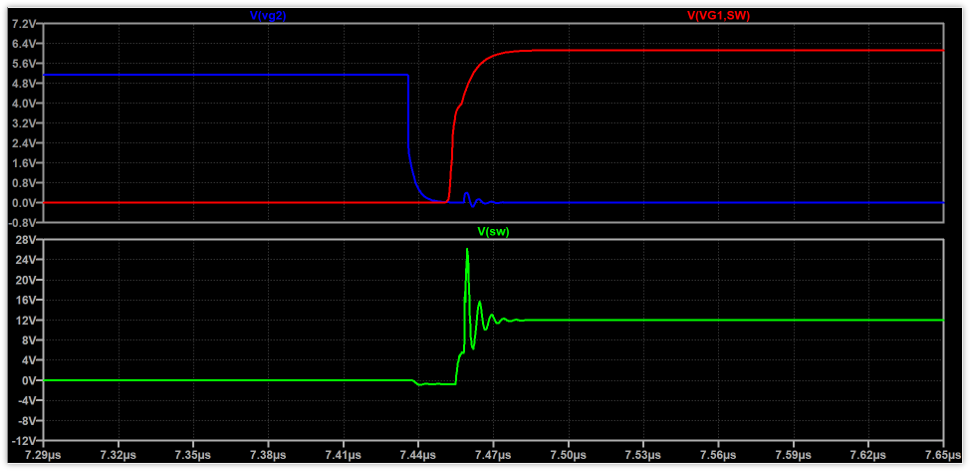

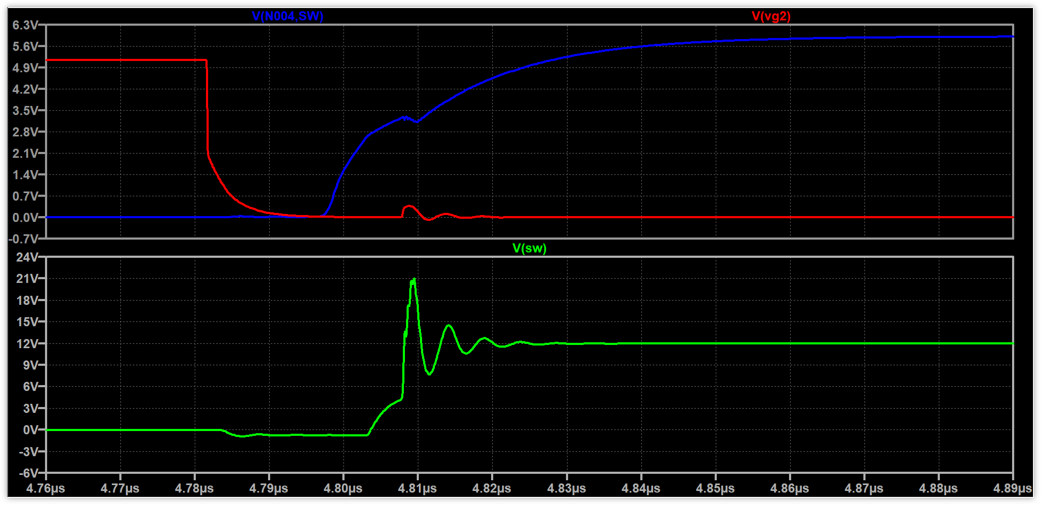

我们以上尖峰(上升沿振荡) 为例,结合波形分析其物理过程。

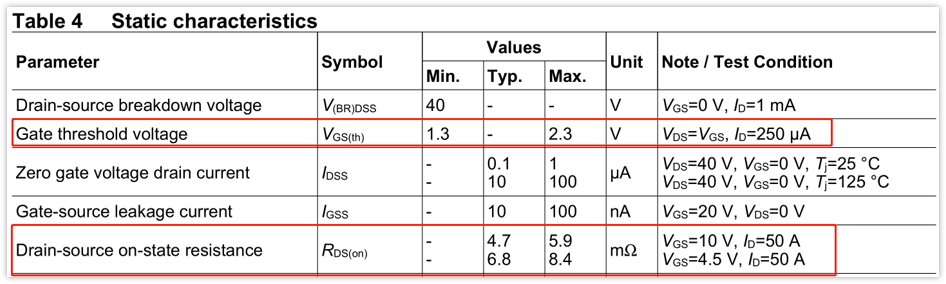

观察关键点:在上尖峰振荡期间,上管Vgs > 3.5V(已完全导通),下管Vgs = 0V(已完全关闭)。查看芯片手册,该MOS管的开启阈值电压Vgs(th)最大为2.3V,印证了此时上管处于深度导通状态。

上管完全导通意味着什么? 此时其导通电阻Rds(on)仅几毫欧,其自身的输出电容Coss相当于被短路。如果没有串联电感,SW点将通过一个小电阻直接连到输入电源Vin,电压不可能剧烈振荡并超过Vin。

因此,必须有寄生电感L的存在。 当开关瞬间电流变化率(di/dt)极大时,会在电感上感应出高压(V = L * di/dt),从而产生尖峰。

具体过程定性分析:

在上管导通前,电感电流通过下管的体二极管续流,下管漏源电压为0。

上管导通瞬间,电路可简化为下图所示的等效结构。由于我们分析的是纳秒级的极短时间,功率电感可被视为一个恒流源(因其自谐振频率约100MHz,对更高频的振荡呈高阻抗)。

简化后,振荡回路主要由上管寄生电感L1、下管输出电容C2、以及回路中的寄生电阻构成。过程简述如下:

- 上管导通,SW点电压从0V开始上升。电源通过L1同时为电感恒流源续流和对C2充电。因此,流经L1的电流

IL1 = I_L + I_C2。

- 当SW电压达到Vin时,若停止上升,则C2充电电流

I_C2 = 0,要求 IL1 = I_L。但此刻 IL1 > I_L,矛盾。

- 因此SW电压会继续上升(超过Vin),导致L1两端电压反向,

IL1开始减小。

- 当

IL1 减小到等于 I_L 时,I_C2 = 0,C2停止充电,SW电压达到峰值。

- 随后,因SW电压 > Vin,

IL1 继续减小,为了维持 I_L 恒定,C2必须放电(I_C2 为负)。SW电压开始下降。

- SW电压下降至Vin后继续降低,L1两端电压再次反向,

IL1 开始增大。如此往复,形成衰减振荡。

整个过程就是典型的LCR二阶电路阻尼振荡。一个更简化的振荡回路模型如下:

结论:

- 上管到输入电容的环路寄生电感L1 是决定上尖峰幅度的核心因素。尖峰电压基本等于该电感两端的感应电压。

- 负载电流越大,电感L1中初始存储的能量(

1/2 * L * I^2)越大,参与振荡的能量也越多,尖峰幅值越高。

- 开关速度越快,电流变化率di/dt越大,L1上的感应电压瞬时值越高,尖峰也越高。

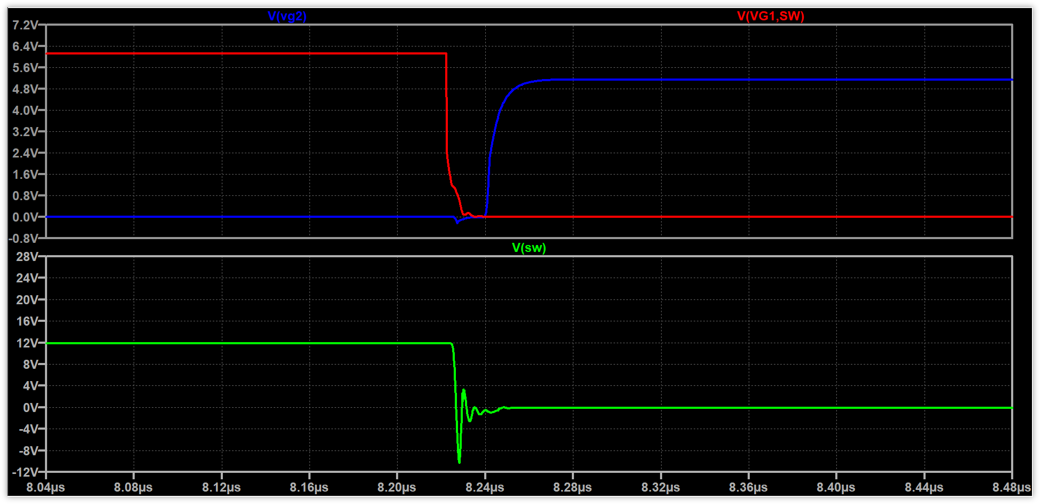

下尖峰的产生机理类似,发生在下管导通、上管关闭的时段,由下管环路寄生电感与上管输出电容等构成振荡回路。

通过仿真实验量化各因素的影响

既然知道寄生电感是关键,我们可以通过控制变量法,直观地看它如何影响尖峰。

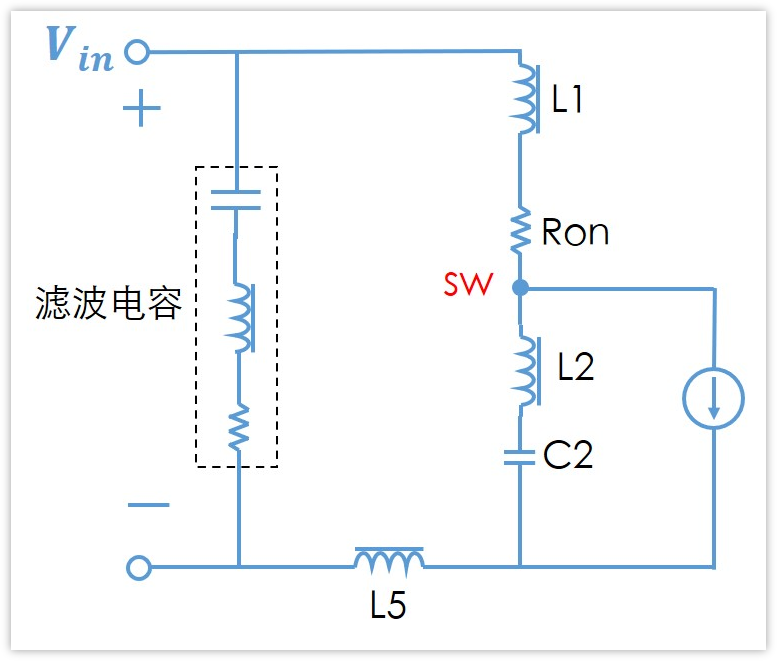

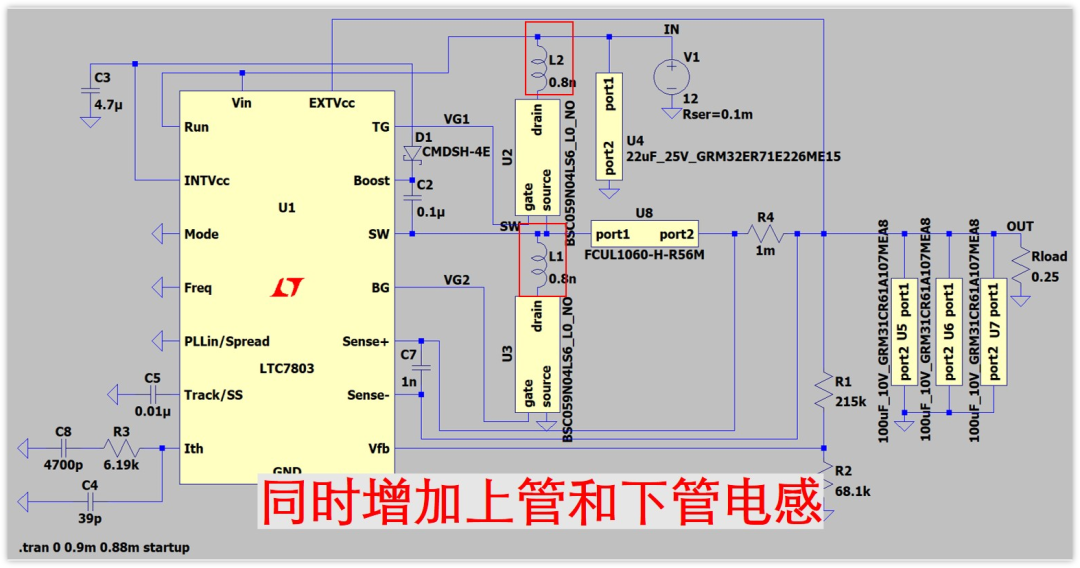

我们使用已将Lg, Ld, Ls设为1fH的“无电感”MOS管模型,然后在电路板上手动添加串联电感来模拟寄生电感。

实验1:仅上管串联0.5nH电感

- 电路:上管D极串联0.5nH,下管无外加电感。

- 负载:0.5Ω (电流约6.6A)。

- 结果:出现约4V的上尖峰,无下尖峰(底部负压仅为死区体二极管压降)。

说明:上、下尖峰主要由各自回路的寄生电感决定。

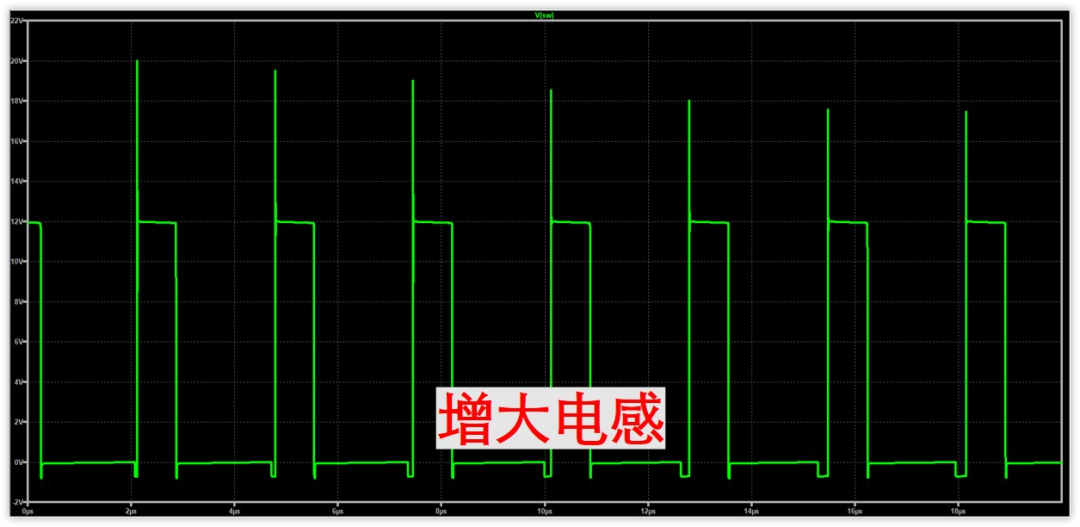

实验2:增大上管串联电感至0.8nH

- 其他条件不变。

- 结果:上尖峰增大至约8V。

说明:寄生电感越大,尖峰幅值越大。

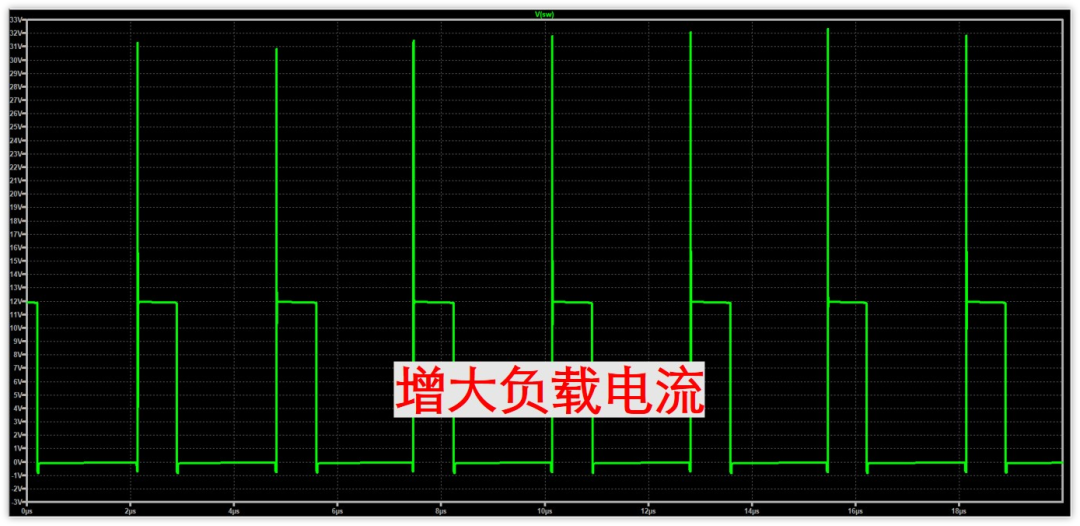

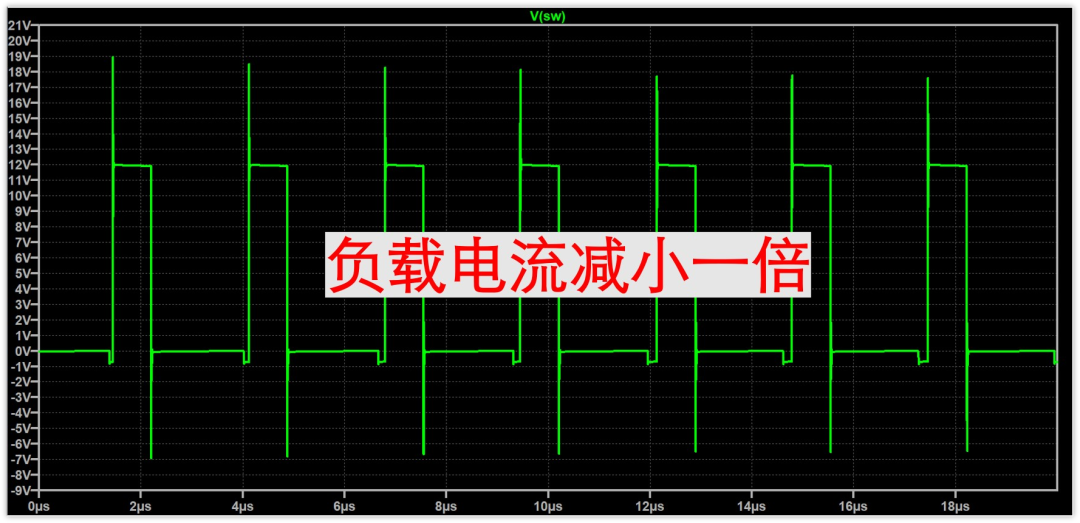

实验3:增大负载电流(减小负载电阻至0.25Ω)

- 上管电感保持0.8nH,负载电流加倍至约13.2A。

- 结果:上尖峰急剧增大至约19V。

说明:负载电流越大,尖峰幅值越大。

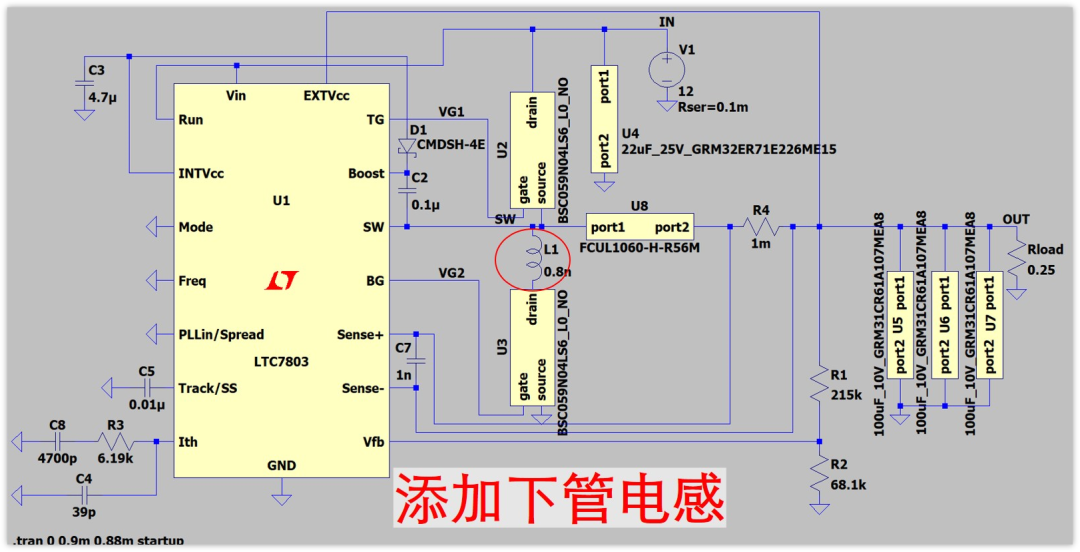

实验4:仅下管串联0.8nH电感

- 去掉上管电感,给下管串联0.8nH,负载电流13.2A。

- 结果:无上尖峰,出现约10.5V的下尖峰。

再次印证:上下尖峰各自独立,由其所在回路电感决定。

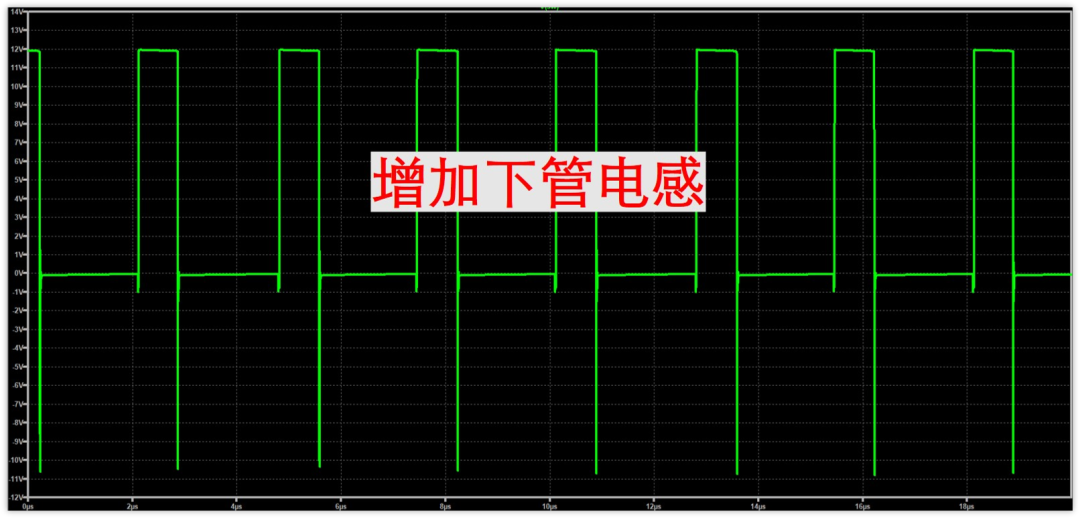

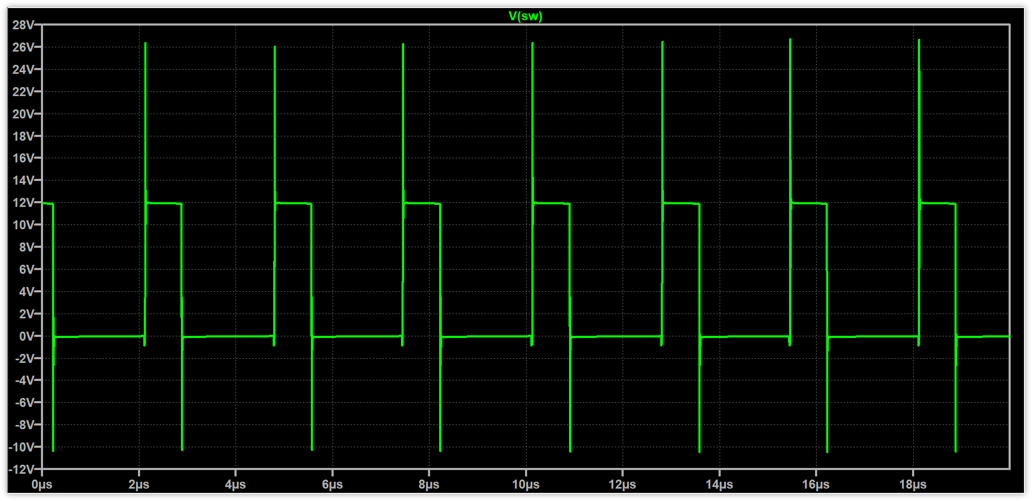

实验5:上下管同时串联0.8nH电感

- 负载电流13.2A。

- 结果:上下尖峰同时存在,上尖峰约14V,下尖峰约10V。

疑问:电感值相同,为何下尖峰更小?

观察波形相位发现:上尖峰发生在上管导通、下管关闭时;而下尖峰发生在死区时间(上下管均关闭),电感电流通过下管体二极管续流,其导通压降会损耗部分能量。

实验6:减小负载电流(上下管电感仍为0.8nH)

- 负载电阻改回0.5Ω,电流约6.6A。

- 结果:上下尖峰均减小至约7V,大小接近。

说明: 此时上下尖峰大小相近,是因为上管导通时电感电流最小,而下管续流时(死区)电感电流最大,两者对尖峰的影响趋势相反。因此,上下尖峰谁大谁小需视具体工作点而定。

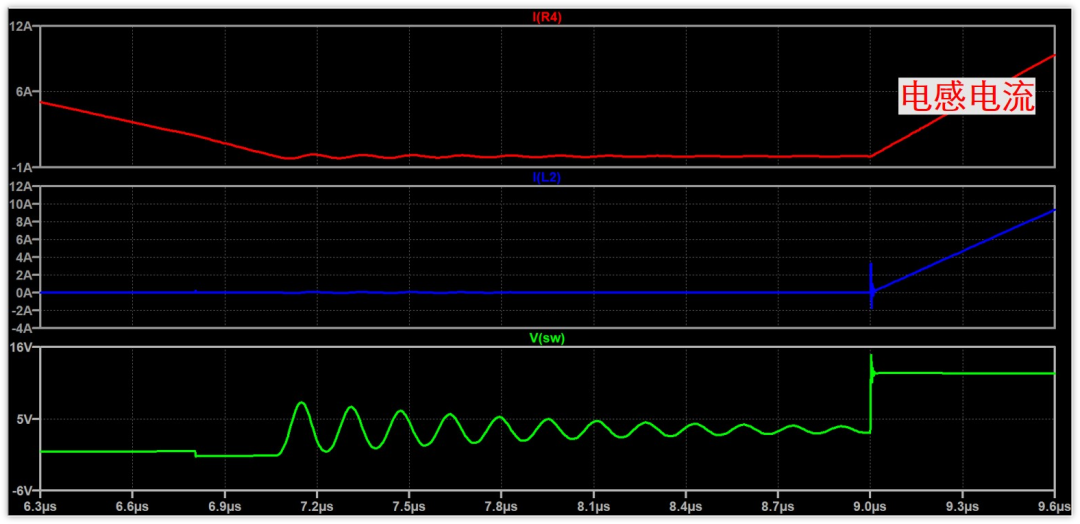

实验7:断续模式下的尖峰

- 将负载增至1Ω,电流约3A,使电路工作在断续模式。

- 结果:上升沿仍有尖峰。

分析: 尽管此时电感电流已降至零,但上管导通瞬间,仍需对下管的输出电容Coss从0V充电至Vin,这个LC回路(上管电感+Coss)仍然会引发振荡。

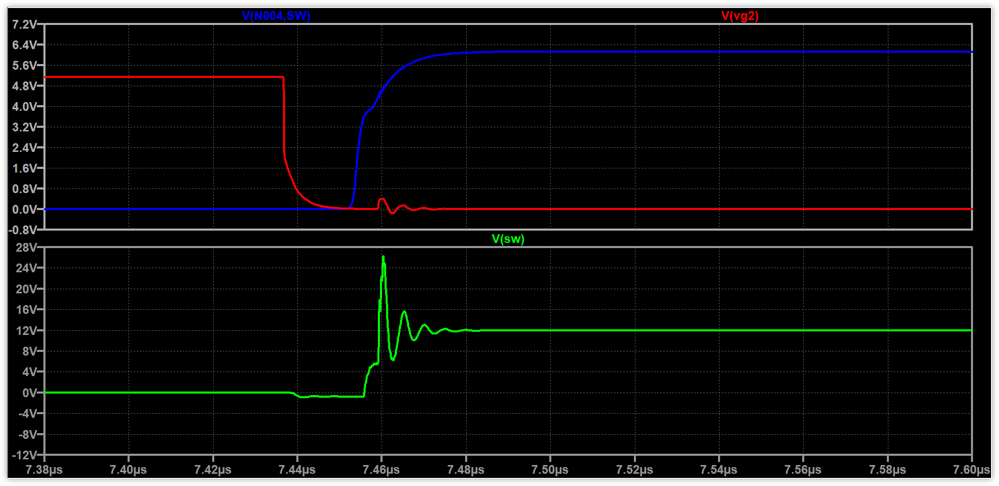

实验8:开关速度的影响(栅极串联电阻)

- 原始条件(上下管0.8nH,13.2A),无栅极电阻时,上管开启时间约7ns,上尖峰14V。

- 在上管栅极串联10Ω电阻。

- 结果:上管开启时间延长至约13ns,上尖峰幅值降至约9V。

说明:降低开关速度(增大开启时间),可以显著减小尖峰幅值。

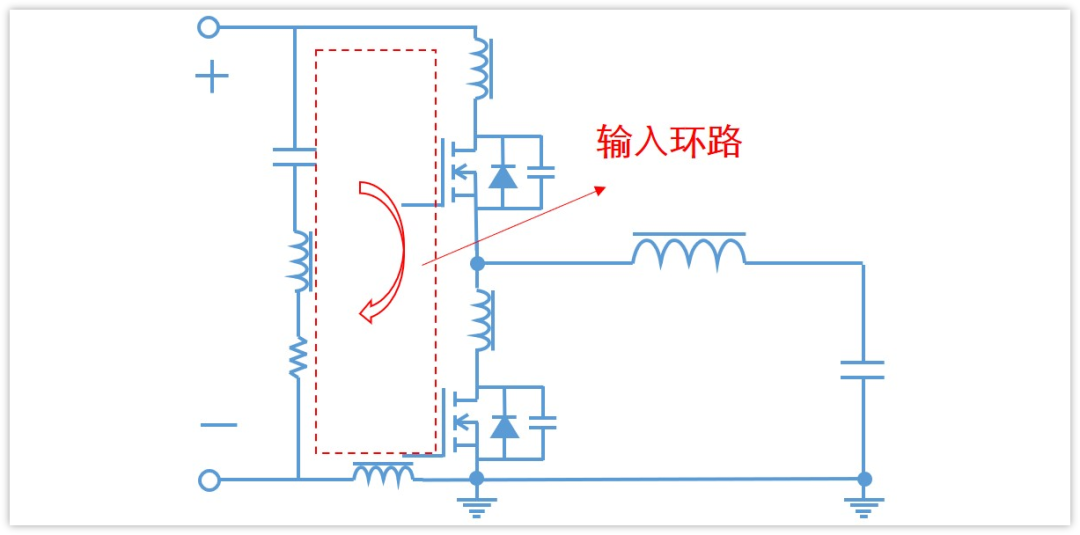

实际电路中的寄生电感来源与PCB布局优化

有人可能会说,我们用的DCDC芯片都是内置MOS管的,也不会在外围故意加电感,这些分析有什么用?

关键在于,仿真中我们添加的0.5nH、0.8nH小电感,模拟的正是实际电路中无法避免的寄生电感,它们存在于:

- 芯片内部键合线。

- PCB走线。

- 滤波电容的等效串联电感(ESL)。

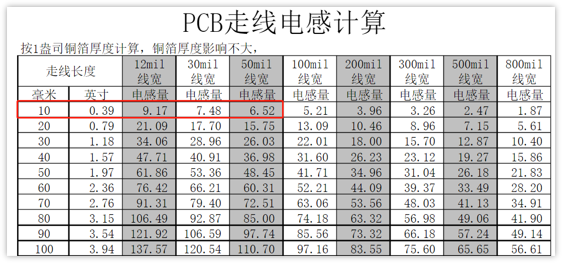

PCB走线电感的影响真的这么大吗?

我们仿真用的最大电感才0.8nH,产生的尖峰就已十分可观。那么0.8nH的走线是什么概念?请看下面PCB走线电感估算表:

对于常见的1盎司铜厚、线宽50mil(约1.27mm)的走线,长度仅为10mm时,电感量就高达6.52nH。即使我们将输入滤波电容放得很近,距离控制在2mm,走线电感也接近1nH。因此在分析百兆赫兹级的振荡尖峰时,PCB走线电感绝对不可忽略。

这也是为什么我们用示波器总能测到尖峰,只是幅度大小有别。

PCB布局的核心优化措施:

- 最小化输入环路面积:这是最重要的一条。务必将输入滤波电容尽可能靠近芯片的Vin和GND引脚放置,最好能直接跨接在引脚上。

- 谨慎处理背面电容:当芯片引脚布局不理想,不得不将输入电容放在PCB背面时,连接电容的过孔必须足够多。

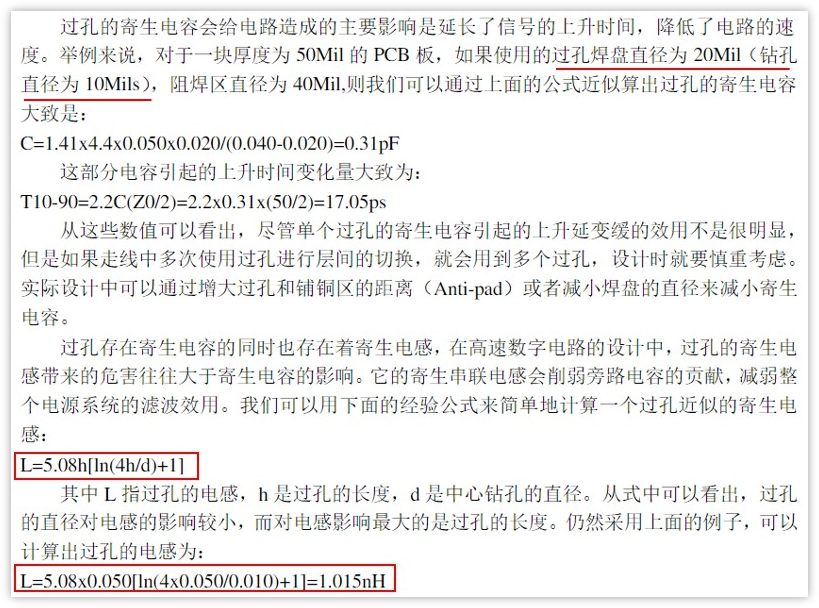

为什么? 因为单个过孔的寄生电感也不容小觑。例如一个10/20mil(钻孔/焊盘)的过孔,寄生电感约1nH。

多打过孔可以实现电感并联,从而减小总电感。这不仅仅是出于载流能力的考虑,更是为了抑制高频振荡。

总结

本文通过大量的LTspice仿真实验,对同步BUCK电路的开关振铃现象进行了逐步深入的剖析,主要结论如下:

- 死区时间是同步BUCK中为避免上下管直通而必然存在的。用示波器观察到开关切换时有一个负压台阶(约-0.7V)是正常现象,那是体二极管在续流。

- 寄生电感是BUCK开关尖峰振荡产生的必要条件。该电感主要来自芯片内部、PCB走线和电容ESL。没有寄生电感,就不会有显著的超调振荡。

- 尖峰幅值与寄生电感大小、负载电流大小、开关速度快慢成正比。要降低尖峰,需从这三方面着手(但负载电流由需求决定,通常不可更改)。

- PCB布局对尖峰有决定性影响。优化布局以最小化高频开关环路(尤其是输入环路)的面积和寄生电感,是抑制振铃、降低EMI的最有效手段。

希望这篇融合了理论分析与仿真实验的长文,能帮助你更透彻地理解BUCK电路开关振铃的本质,并在实际设计中做出更优的决策。如果你对电源设计或电路仿真有更多兴趣,欢迎到云栈社区与大家深入交流。